- •Введение

- •1. Основные определения и понятия микропроцессорной техники

- •1.1. Жесткая и гибкая логика

- •1.2. Микропроцессор и «сотоварищи»

- •Контрольные вопросы

- •2. Типы микропроцессорных систем и факторы, влияющие на их быстродействие

- •2.1. Типы микропроцессорных систем

- •2.2. Программируемые логические интегральные схемы

- •2.3. Факторы, влияющие на быстродействие микропроцессоров

- •Контрольные вопросы

- •3.3.1. Команды пересылки данных

- •3.3.2. Арифметические команды

- •3.3.3. Логические команды

- •3.3.4. Команды переходов

- •3.4. Быстродействие процессора

- •4.3.1. Память программ

- •4.3.2. Память данных

- •5.1.2. Микроконтроллеры семейств pic16cxxx и pic17cxxx

- •5.1.3. Особенности архитектуры микроконтроллеров семейства pic16cxxx

- •5.2. Микроконтроллеры подгруппы pic16f8x

- •5.2.1. Основные характеристики

- •5.2.2. Особенности архитектуры

- •5.2.3. Схема тактирования и цикл выполнения команды

- •5.2.4. Организация памяти программ и стека

- •5.2.5. Организация памяти данных

- •5.2.6. Регистры специального назначения

- •5.2.7. Счетчик команд

- •5.2.8. Прямая и косвенная адресации

- •5.2.9. Порты ввода/вывода

- •5.2.10. Модуль таймера и регистр таймера

- •5.2.11. Память данных в рпзу (eeprom)

- •5.2.12. Организация прерываний

- •5.2.13. Специальные функции

- •5.3. Система команд микроконтроллеров подгруппы pic16f8x

- •5.3.1. Перечень и форматы команд

- •5.3.2. Команды работы с байтами

- •5.3.3. Команды работы с битами

- •5.3.4. Команды управления и работы с константами

- •5.3.5. Особенности программирования и отладки

- •6.1. Разработка микропроцессорной системы на основе микроконтроллера

- •6.1.1. Основные этапы разработки

- •6.1.2. Разработка и отладка аппаратных средств

- •6.1.3. Разработка и отладка программного обеспечения

- •6.1.4. Методы и средства совместной отладки аппаратных и программных средств

5.2.9. Порты ввода/вывода

Контроллеры подгруппы PIC16F8X имеют два порта:PORTA(5 бит) иPORTB(8 бит) с побитовой индивидуальной настройкой на ввод или на вывод.

ПортA(PORTA) представляет собой 5-битовый фиксатор, соответствующий выводам контроллераRA<4:0>. ЛинияRA4имеет вход триггера Шмитта и выход с открытым стоком. Все остальные линиипортаимеют ТТЛ входные уровни и КМОП выходные буферы. АдресрегистрапортаА–05h.

Каждой линии портапоставлен в соответствие бит направления передачи данных, который хранится в управляющемрегистреTRISA, расположенном по адресу85h. Если бит управляющегоTRISAрегистраимеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующегорегистра-фиксаторапорта. При включении питания все линиипортапо умолчанию настроены на ввод.

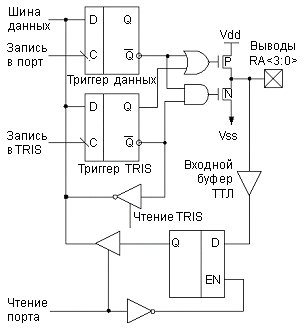

На рис. 5.8дана схема линийRA<3:0>портаA.

Рис.

5.8.Схема линий RA <3:0> порта А.

Выводы порта имеют защитные диоды к Vdd

и Vss.

Рис.

5.8.Схема линий RA <3:0> порта А.

Выводы порта имеют защитные диоды к Vdd

и Vss.

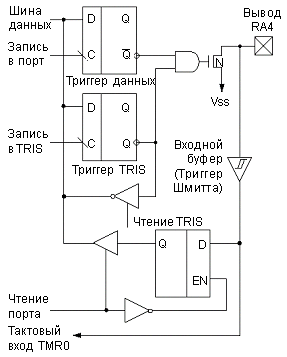

Операция чтения портаАсчитывает состояние выводовпорта, в то время как запись в него изменяет состояние триггеровпорта. Все операции спортомявляются операциями типа «чтение-модификация-запись». Поэтому запись впортпредполагает, что состояние выводовпортавначале считывается, затем модифицируется и записывается в триггер-фиксатор. ВыводRA4мультиплексирован с тактовым входомтаймераTMR0. Схема линииRA4портаАприведена нарис. 5.9.

ПортВ(PORTB) – это двунаправленный 8-битовыйпорт, соответствующий выводамRB<7:0>контроллера и расположенный по адресу06h. Относящийся кпортуВ управляющийрегистрTRISBрасположен на первой страницерегистровпо адресу86h. Если бит управляющегоTRISBрегистраимеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующегорегистразащелки. При включении питания все линиипортапо умолчанию настроены на ввод.

Рис.

5.9.Схема линии RA4 порта А. Вывод

порта имеет защитный диод только к Vss.

Рис.

5.9.Схема линии RA4 порта А. Вывод

порта имеет защитный диод только к Vss.

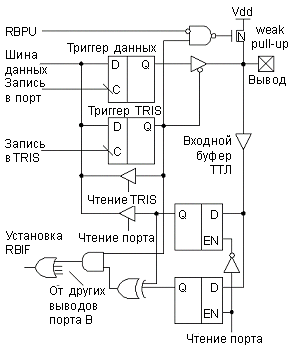

У каждой ножки портаВимеется небольшая активная нагрузка (около 100мкА) на линию питания (pull-up). Она автоматически отключается, если эта ножка запрограммирована как вывод. Более того, управляющий бит/RBPUрегистраOPTION<7>может отключить (приRBPU=1) все нагрузки. Сброс при включении питания также отключает все нагрузки.

Четыре линии портаВ(RB<7:4>) могут вызватьпрерываниепри изменении значения сигнала на любой из них. Если эти линии настроены на ввод, то они опрашиваются и защелкиваются в цикле чтенияQ1. Новая величина входного сигнала сравнивается со старой в каждом командном цикле. При несовпадении значения сигнала на ножке и в фиксаторе генерируется высокий уровень. Выходы детекторов «несовпадений»RB4,RB5,RB6,RB7объединяются по ИЛИ и генерируютпрерываниеRBIF(запоминаемое врегистреINTCON<0>). Любая линия, настроенная как вывод, в этом сравнении не участвует.Прерываниеможет вывести кристалл из режимаSLEEP. В подпрограмме обработкипрерыванияследует сбросить запроспрерыванияодним из следующих способов:

прочитать (или записать в) порт В. Это завершит состояние сравнения;

обнулить бит RBIF регистра INTCON<0>.

При этом необходимо иметь в виду, что условие «несовпадения» будет продолжать устанавливать признак RBIF. Только чтениепортаВможет устранить «несовпадение» и позволит обнулить битRBIF.

Прерываниепо несовпадению и программно устанавливаемые внутренние активные нагрузки на этих четырех линиях могут обеспечить простой интерфейс, например, с клавиатурой, с выходом из режимаSLEEPпо нажатию клавиш.

Схемы линий портаBприведены нарис. 5.10и5.11.

Рис.

5.10.Схема линий RB <7:4> порта B.

Выводы порта имеют защитные диоды к Vdd

и Vss.

Рис.

5.10.Схема линий RB <7:4> порта B.

Выводы порта имеют защитные диоды к Vdd

и Vss.

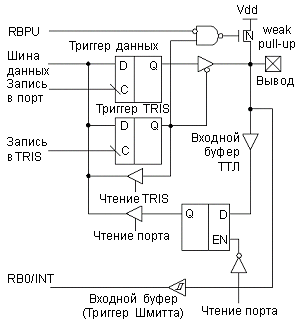

Рис.

5.11.Схема линий RB <3:0> порта B.

Выводы порта имеют защитные диоды к Vdd

и Vss.

Рис.

5.11.Схема линий RB <3:0> порта B.

Выводы порта имеют защитные диоды к Vdd

и Vss.

При организации двунаправленных портовнеобходимо учитывать особенности организации ввода/вывода данных МК. Любая команда, которая осуществляет запись, выполняет ее внутри как «чтение-модификация-запись». Например, командыBCFиBSFсчитываютпортцеликом, модифицируют один бит и выводят результат обратно. Здесь необходима осторожность. В частности, командаBSF PORTB, 5(установить в единицу бит 5портаB) сначала считывает все реальные значения сигналов, присутствующие в данный момент на выводахпорта. Затем выполняются действия над битом 5, и новое значение байта целиком записывается в выходные фиксаторы. Если другой битрегистраPORTBиспользуется в качестве двунаправленного ввода/вывода (скажем, бит 0), и в данный момент он определен как входной, то входной сигнал на этом выводе будет считан и записан обратно в выходной триггер-фиксатор этого же вывода, стирая предыдущее состояние. До тех пор, пока эта ножка остается в режиме ввода, никаких проблем не возникает. Однако если позднее линия 0 переключи тся в режим вывода, ее состояние будет неопределенным.

На ножку, работающую в режиме вывода, не должны нагружаться внешние источники токов («монтажное И», «монтажное ИЛИ»). Большие результирующие токи могут повредить кристалл.

Необходимо выдерживать определенную последовательность обращения к портамввода/вывода. Запись впортвывода происходит в конце командного цикла. Но при чтении данные должны быть стабильны в начале командного цикла. Будьте внимательны в операциях чтения, следующих сразу за записью в тот жепорт. Здесь надо учитывать инерционность установления напряжения на выводах. Может потребоваться программная задержка, чтобы напряжение на ножке (которое зависит от нагрузки) успело стабилизироваться до начала исполнения следующей команды чтения.