- •Введение

- •1. Основные определения и понятия микропроцессорной техники

- •1.1. Жесткая и гибкая логика

- •1.2. Микропроцессор и «сотоварищи»

- •Контрольные вопросы

- •2. Типы микропроцессорных систем и факторы, влияющие на их быстродействие

- •2.1. Типы микропроцессорных систем

- •2.2. Программируемые логические интегральные схемы

- •2.3. Факторы, влияющие на быстродействие микропроцессоров

- •Контрольные вопросы

- •3.3.1. Команды пересылки данных

- •3.3.2. Арифметические команды

- •3.3.3. Логические команды

- •3.3.4. Команды переходов

- •3.4. Быстродействие процессора

- •4.3.1. Память программ

- •4.3.2. Память данных

- •5.1.2. Микроконтроллеры семейств pic16cxxx и pic17cxxx

- •5.1.3. Особенности архитектуры микроконтроллеров семейства pic16cxxx

- •5.2. Микроконтроллеры подгруппы pic16f8x

- •5.2.1. Основные характеристики

- •5.2.2. Особенности архитектуры

- •5.2.3. Схема тактирования и цикл выполнения команды

- •5.2.4. Организация памяти программ и стека

- •5.2.5. Организация памяти данных

- •5.2.6. Регистры специального назначения

- •5.2.7. Счетчик команд

- •5.2.8. Прямая и косвенная адресации

- •5.2.9. Порты ввода/вывода

- •5.2.10. Модуль таймера и регистр таймера

- •5.2.11. Память данных в рпзу (eeprom)

- •5.2.12. Организация прерываний

- •5.2.13. Специальные функции

- •5.3. Система команд микроконтроллеров подгруппы pic16f8x

- •5.3.1. Перечень и форматы команд

- •5.3.2. Команды работы с байтами

- •5.3.3. Команды работы с битами

- •5.3.4. Команды управления и работы с константами

- •5.3.5. Особенности программирования и отладки

- •6.1. Разработка микропроцессорной системы на основе микроконтроллера

- •6.1.1. Основные этапы разработки

- •6.1.2. Разработка и отладка аппаратных средств

- •6.1.3. Разработка и отладка программного обеспечения

- •6.1.4. Методы и средства совместной отладки аппаратных и программных средств

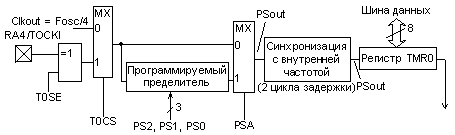

5.2.10. Модуль таймера и регистр таймера

Структурамодулятаймера/счетчикаTIMER0и его взаимосвязь срегистрамиTMR0иOPTIONпоказаны нарис. 5.12.TIMER0является программируемым модулем и содержит следующие компоненты:

8-разрядный таймер/счетчик TMR0 с возможностью чтения и записи как регистр;

8-разрядный программно управляемый предварительный делитель (пределитель);

мультиплексор входного сигнала для выбора внутреннего или внешнего тактового сигнала;

схему выбора фронта внешнего тактового сигнала;

формирователь запроса прерывания по переполнению регистра TMR0 с FFh до 00h.

Режим таймеравыбирается путем сбрасывания в ноль битаT0CSрегистраOPTION <5>. В режиметаймераTMR0инкрементируется каждый командный цикл (без пределителя). После записи информации вTMR0инкрементирование его начнется после двух командных циклов. Это происходит со всеми командами, которые производят запись или чтение-модификацию-записьTMR0(например,MOVF TMR0,CLRF TMR0). Избежать этого можно при помощи записи вTMR0скорректированного значения. ЕслиTMR0нужно проверить на равенство нулю без останова счета, следует использовать инструкциюMOVF TMR0,W.

Режим счетчика выбирается путем установки в единицу бита T0CSрегистраOPTION<5>. В этом режимерегистрTMR0будет инкрементироваться либо нарастающим, либо спадающим фронтом на выводеRA4/T0CKIот внешних событий. Направление фронта определяется управляющим битомT0SEврегистреOPTION<4>. ПриT0SE = 0будет выбран нарастающий фронт.

Пределитель может использоваться или совместно с TMR0, или со сторожевым (Watchdog)таймером. Вариант подключения делителя контролируется битомPSA регистраOPTION<3>. ПриPSA=0делитель будет подсоединен кTMR0. Содержимое делителя программе недоступно. Коэффициент деления пределителя программируется битамиPS2…PS0регистраOPTION<2:0>.

Рис.

5.12.Структурная схема таймера/счетчика

TMR0.

Рис.

5.12.Структурная схема таймера/счетчика

TMR0.

ПрерываниепоTMR0вырабатывается тогда, когда происходит переполнениерегистратаймера/счетчика при переходе отFFhк00h. Тогда устанавливается бит запросаT0IFврегистреINTCON<2>. Данноепрерываниеможно замаскировать битомT0IEврегистреINTCON<5>. Бит запросаT0IFдолжен быть сброшен программно при обработкепрерывания.ПрерываниепоTMR0не может вывести процессор из режимаSLEEPпотому, чтотаймерв этом режиме не функционирует.

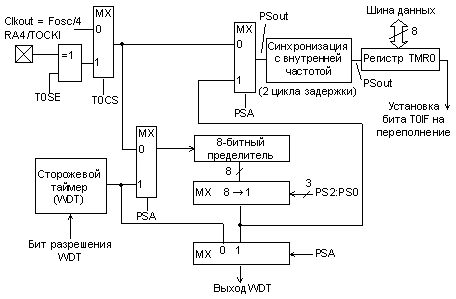

При PSA=1делитель будет подсоединен к сторожевомутаймерукак постделитель (делитель на выходе). Возможные варианты использования пределителя показаны нарис. 5.13.

При использовании пределителя совместно с TMR0, все команды, изменяющие содержимоеTMR0, обнуляют пределитель. Если пределитель используется совместно сWDT, командаCLRWDTобнуляет содержимое пределителя вместе сWDT.

При использовании модуля TIMER0в режиме счетчика внешних событий необходимо учитывать то, что внешний тактовый сигнал синхронизируется внутренней частотой Fosc. Это приводит к появлению задержки во времени фактического инкрементирования содержимогоTMR0.

Синхронизация происходит по окончании 2-го и 4-го тактов работы МК, поэтому, если пределитель не используется, то для фиксации входного события необходимо, чтобы длительности высокого и низкого состояний сигнала на входе RA4/T0CKIбыли бы не менее 2 периодов тактовой частоты Tosc плюс некоторая задержка ( ~ 20 нс).

Если модуль TIMER0используется совместно с пределителем, то частота входного сигнала делится асинхронным счетчиком так, что сигнал на выходе пределителя становится симметричным. При этом необходимо, чтобы длительности высокого и низкого уровней сигнала на входеRA4/T0CKIбыли бы не менее 10 нс. Синхронизация сигнала происходит на выходе пределителя, поэтому существует небольшая задержка между фронтом внешнего сигнала и временем фактического инкрементатаймера/счетчика. Эта задержка находится в диапазоне от 3 до 7 периодов колебаний тактового генератора. Таким образом, измерение интервала между событиями будет выполнено с точностью±4 · Tosc.

Рис.

5.13.Структура и возможные варианты

использования пределителя.

Рис.

5.13.Структура и возможные варианты

использования пределителя.