- •Введение

- •1. Основные определения и понятия микропроцессорной техники

- •1.1. Жесткая и гибкая логика

- •1.2. Микропроцессор и «сотоварищи»

- •Контрольные вопросы

- •2. Типы микропроцессорных систем и факторы, влияющие на их быстродействие

- •2.1. Типы микропроцессорных систем

- •2.2. Программируемые логические интегральные схемы

- •2.3. Факторы, влияющие на быстродействие микропроцессоров

- •Контрольные вопросы

- •3.3.1. Команды пересылки данных

- •3.3.2. Арифметические команды

- •3.3.3. Логические команды

- •3.3.4. Команды переходов

- •3.4. Быстродействие процессора

- •4.3.1. Память программ

- •4.3.2. Память данных

- •5.1.2. Микроконтроллеры семейств pic16cxxx и pic17cxxx

- •5.1.3. Особенности архитектуры микроконтроллеров семейства pic16cxxx

- •5.2. Микроконтроллеры подгруппы pic16f8x

- •5.2.1. Основные характеристики

- •5.2.2. Особенности архитектуры

- •5.2.3. Схема тактирования и цикл выполнения команды

- •5.2.4. Организация памяти программ и стека

- •5.2.5. Организация памяти данных

- •5.2.6. Регистры специального назначения

- •5.2.7. Счетчик команд

- •5.2.8. Прямая и косвенная адресации

- •5.2.9. Порты ввода/вывода

- •5.2.10. Модуль таймера и регистр таймера

- •5.2.11. Память данных в рпзу (eeprom)

- •5.2.12. Организация прерываний

- •5.2.13. Специальные функции

- •5.3. Система команд микроконтроллеров подгруппы pic16f8x

- •5.3.1. Перечень и форматы команд

- •5.3.2. Команды работы с байтами

- •5.3.3. Команды работы с битами

- •5.3.4. Команды управления и работы с константами

- •5.3.5. Особенности программирования и отладки

- •6.1. Разработка микропроцессорной системы на основе микроконтроллера

- •6.1.1. Основные этапы разработки

- •6.1.2. Разработка и отладка аппаратных средств

- •6.1.3. Разработка и отладка программного обеспечения

- •6.1.4. Методы и средства совместной отладки аппаратных и программных средств

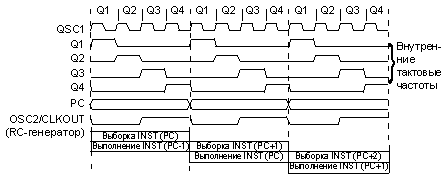

5.2.3. Схема тактирования и цикл выполнения команды

Входная тактовая частота, поступающая с вывода OSC1/CLKIN, делится внутри на четыре, и из нее формируются четыре циклические не перекрывающиеся тактовые последовательностиQ1,Q2,Q3иQ4. Счетчик команд увеличивается в тактеQ1, команда считывается из памяти программы и защелкивается врегистрекоманд в тактеQ4. Команда декодируется и выполняется в течение последующего цикла в тактахQ1...Q4. Схема тактирования и выполнения команды изображена нарис. 5.2.

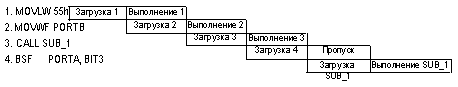

Цикл выполнения командысостоит из четырех тактов:Q1...Q4. Выборка команды и ее выполнение совмещены по времени таким образом, что выборка команды занимает один цикл, а выполнение – следующий цикл. Эффективное время выполнения команды составляет один цикл. Если команда изменяет счетчик команд (например, командаGOTO), то для ее выполнения потребуется два цикла, как показано нарис. 5.3.

Рис.

5.2.Схема тактирования и выполнения

команды.

Рис.

5.2.Схема тактирования и выполнения

команды.

Рис.

5.3.Выборка команд.

Рис.

5.3.Выборка команд.

Цикл выборки начинается с увеличения счетчика команд в такте Q1. Вцикле выполнения командывыбранная команда защелкивается врегистркоманд в тактеQ1. В течение тактовQ2,Q3иQ4происходит декодирование и выполнение команды. В тактеQ2считывается память данных (чтение операнда), а запись происходит в тактеQ4.

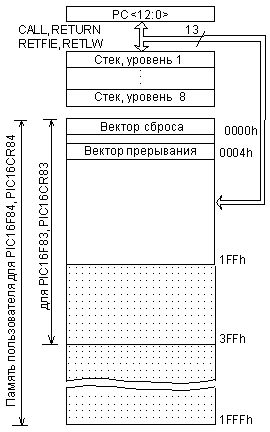

5.2.4. Организация памяти программ и стека

Счетчик команд в МК PIC16F8Х имеет ширину 13 бит и способен адресовать 8Кх14бит объема программной памяти. Однако физически на кристаллах PIC16F83 и PIC16CR83 имеется только 512х14 памяти (адреса 0000h-01FFh), а в МК PIC16F84 и PIC16CR84 – 1Кх14 памяти (адреса0000h-03FFh). Обращение к адресам выше1FFh(3FFh) фактически естьадресацияв те же первые 512 адресов (первые 1К адресов).

Организация памяти программ и стека приведена на рис. 5.4.

В памяти программ есть выделенные адреса. Вектор сброса находится по адресу 0000h, векторпрерывания– по адресу0004h. Обычно по адресу0004hрасполагается подпрограмма идентификации и обработкипрерываний, а по адресу0000h– команда перехода на метку, расположенную за подпрограммой обработкипрерываний.

Рис.

5.4.Организация памяти программ и

стека.

Рис.

5.4.Организация памяти программ и

стека.

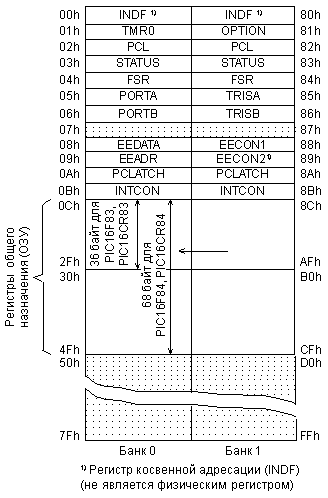

5.2.5. Организация памяти данных

Память данных МК разбита на две области. Первые 12 адресов – это область регистровспециальных функций (SFR), а вторая – областьрегистровобщего назначения (GPR). Область SFR управляет работой прибора.

Обе области разбиты в свою очередь на банки 0 и 1. Банк 0 выбирается обнулением бита RP0регистрастатуса (STATUS). Установка битаRP0в единицу выбирает банк 1. Каждый банк имеет протяженность 128 байт. Однако для PIC16F83 и PIC16CR83 память данных существует только до адреса02Fh, а для PIC16F84 и PIC16CR84 – до адреса04Fh.

На рис. 5.5изображена организация памяти данных.

Рис.

5.5.Организация памяти данных.

Рис.

5.5.Организация памяти данных.

Некоторые регистрыспециального назначения продублированы в обоих банках, а некоторые расположены в банке 1 отдельно.

Регистрыс адресами0Ch-4Fhмогут использоваться какрегистрыобщего назначения, которые представляют собой статическое ОЗУ. Адресарегистровобщего назначения банка 1 отображаются на банк 0. Следовательно, когда установлен банк 1, то обращение к адресам8Ch-CFhфактически адресует банк 0.

В регистрестатуса помимо битаRP0есть еще битRB1, что позволяет обращаться к четырем страницам (банкам) будущих модификаций этого кристалла.

К ячейкам ОЗУ можно адресоваться прямо, используя абсолютный адрес каждого регистра, или косвенно, черезрегиструказательFSR. Косвеннаяадресацияиспользует текущее значение разрядовRP1:RP0для доступа к банкам. Это относится и кEEPROMпамяти данных. В обоих случаях можно адресовать до 512регистров.