- •Лабораторная работа № 5 Наименование работы

- •Цель работы

- •Задание к лабораторной работе

- •Перечень используемого оборудования и по

- •Краткие теоретические сведения Определение.

- •Математическая модель дешифратора

- •Способы построения дешифраторов

- •Дешифраторы адреса

- •Дешифратор кода операции

- •Применение дешифраторов в схемах управления

- •Мультиплексоры

- •Требования безопасности труда

- •Порядок проведения работы

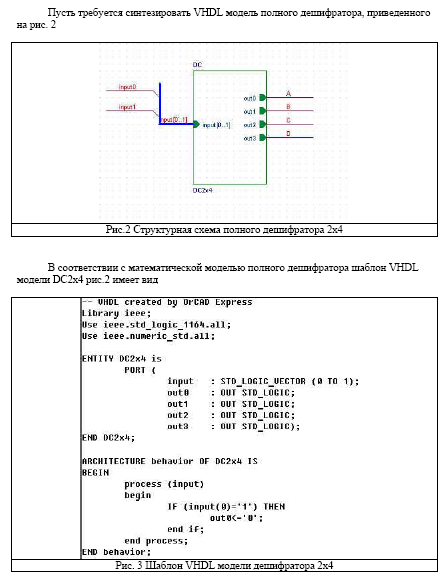

- •Пример разработкиVhdl модели дешифратора

- •Содержание отчета

- •Контрольные вопросы

- •Список литературы

Порядок проведения работы

1. Подготовка к выполнению лабораторной работы.

Разработка VHDLмоделей дешифраторов и мультиплексоров и их верификация должны быть проведены в средеOrCAD(hostPC)

Выполнение лабораторной работы проводится в аудитории под контролем преподавателя.

Перед выполнением лабораторной работы необходимо проверить наличие защитного заземления, исправность схем аварийного отключения питания.

2. Порядок выполнения лабораторной работы:

- в соответствии с разработанной принципиальной электрической схемой, выполнить необходимые коммутации на макетной плате FLEX8000 (target);

- подсоединить к контрольным точкам щупы осциллографа;

- включить питание (подсоединить FLEX8000 к удлинителюUSB);

- при правильном соединении загорается светодиод HL1;

- при возникновении проблем с соединением необходимо обратиться к преподавателю;

- сконфигурировать ПЛИС FLEX8000 в средеMAXPLUS(Host PC+target);

- наблюдать временные диаграммы в контрольных точках, обеспечивая синхронизацию органами управления осциллографа;

- при несоответствии наблюдаемых осциллограмм заданию, необходимо повторить синтез VHDLмоделей схем с учетом отмеченных недостатков; затем необходимо провести верификациюVHDLмодели. Внесенные изменения необходимо согласовать с преподавателем и повторить валидациюVHDLмодели (Host PC);

- скопировать временные диаграммы с экрана осциллографа.

Пример разработкиVhdl модели дешифратора

Содержание отчета

Отчет к лабораторной работе должен содержать:

Задание на разработку дешифратора и мультиплексора

Структурную схему VHDLмодели цифровой системы

Программную модель цифровой системы в среде GHDL

Временной анализ верификации VHDLмодели в средеGHDL.

Принципиальную электрическую схему валидации VHDLмодели на макетеFLEX8000.

Временной анализ валидации VHDLмодели цифровой системы.

Оценку коэффициентов управляемости и коэффициентов наблюдаемости схемы

Оценку длины критического пути

Тестирование VHDL- модели устройства вGHDL.

Рекомендации по совершенствованию системы тестирования

Выводы по лабораторной работе.

Контрольные вопросы

Приведите математическую модель дешифратора

Дайте определение полного дешифратора

Дайте определение и приведите пример неполного дешифратора

Приведите пример прямоугольного дешифратора

Приведите пример пирамидального дешифратора

Приведите определение критического пути.

Приведите пример мультиплексора 8 –> 1.

Список литературы

1. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на

интегральных микросхемах: Справочник.- М.: Радио и связь, 1990.- 340 с.

2. Хопкфорт Джон Э., Мотванн Раджив, Ульиман Джефри Д. Введение в теорию

автоматов, языков и вычислений.: Пер. с англ.- М.: Издательский дом «Вильямс»,

2002.- c. 224.

3. Мик Дж., Брик Дж. Проектирование микропроцессорных устройств с разрядно-

модульной организацией: Пер. с англ.-М.: Мир, 1984.- Кн.1 – 252 с.

4. Рафикузаман М. Микропроцессоры и машинное проектирование

микропроцессорных систем. Пер. с англ.- М.: Мир, 1988.- 312 с.

Содержание

Наименование работы 1

Цель работы 1

Задание к лабораторной работе 1

Перечень используемого оборудования и ПО 2

Краткие теоретические сведения 2

Определение. 2

Математическая модель дешифратора 3

Способы построения дешифраторов 4

Дешифраторы адреса 5

Дешифратор кода операции 5

Применение дешифраторов в схемах управления 5

Мультиплексоры 5

Требования безопасности труда 6

Порядок проведения работы 6

Пример разработки VHDL модели дешифратора 8

Содержание отчета 9

Контрольные вопросы 9

Список литературы 9