Laba_po_elt4

.docxФГБОУ ВПО МГТУ СТАНКИН

Лабораторная работа №4

Триггеры, счетчики, регистры.

Выполнили студенты группы ИДБ-11-04

Шерстнёва Алёна

Петрунин Андрей

Москва 2013

Цель работы: Исследование работы синхронных и асинхронных триггеров, а также различных типов счетчиков и регистров построенных на основе триггеров.

Ход работы:

-

Исследование работы асинхронного RS-триггера

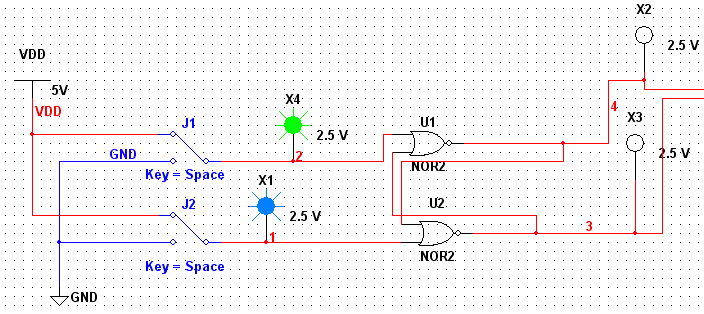

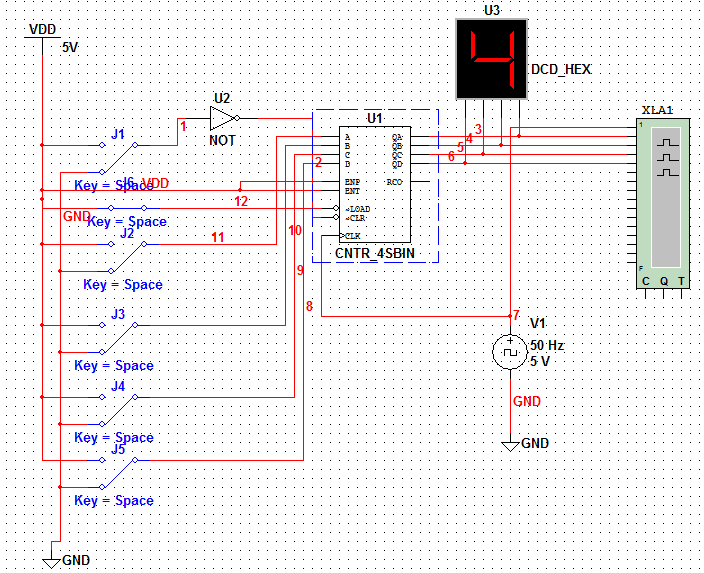

Схема для моделирования работы асинхронного RS-триггера

Таблица переключений асинхронного RS триггера

|

R |

S |

Q |

NQ |

Режим |

|

0 |

1 |

1 |

0 |

Установка |

|

0 |

0 |

1 |

0 |

Хранение |

|

1 |

0 |

0 |

1 |

Сброс |

|

0 |

0 |

0 |

1 |

Хранение |

|

1 |

1 |

0 |

0 |

Запрещенный |

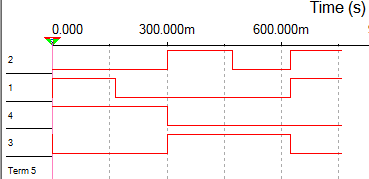

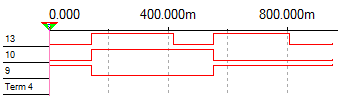

Временные диаграммы:

4 – Q; 3-NQ; 2-R; 1-S

Вывод: Мы смоделировали асинхронный RS триггер, и по показаниям индикаторов определили режимы его работы, с помощью логического анализатора сняли временные диаграммы.

-

Исследование работы синхронных триггеров

Схема

для моделирования работы триггеров

Схема

для моделирования работы триггеров

Таблица переключений синхронного RS триггера:

|

С |

R |

S |

Q |

NQ |

Режим |

|

1 |

0 |

1 |

1 |

0 |

Установка |

|

1 |

0 |

0 |

1 |

0 |

Хранение |

|

1 |

1 |

0 |

0 |

1 |

Изменение на инверсное |

|

1 |

0 |

0 |

0 |

1 |

Хранение |

|

1 |

1 |

1 |

0 |

0 |

Сброс |

|

0 |

Любые |

Любые |

0 |

0 |

Запрещенное |

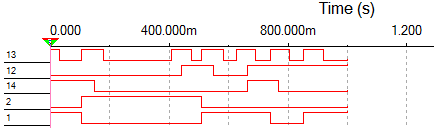

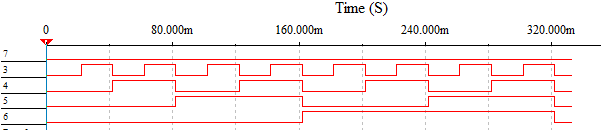

Временная диаграмма для синхронного RS триггера:

С-13,R-12,S-14,Q-2,NQ-1.

|

C |

J |

K |

Q |

NQ |

Режим |

|

1 |

0 |

1 |

0 |

1 |

Запись |

|

1 |

0 |

0 |

0 |

1 |

Блокировка |

|

1 |

1 |

0 |

1 |

0 |

Запись |

|

1 |

0 |

0 |

1 |

0 |

Хранение |

|

1 |

1 |

1 |

0 |

1 |

Запрещенное |

|

0 |

Любые |

Любые |

0 |

1 |

- |

Таблица переключений синхронного JK триггера:

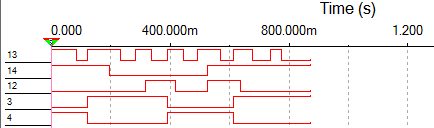

Временная диаграмма для синхронного JK триггера:

C-13,K-12,J-14,Q-3,NQ-4.

Таблица переключений синхронного D триггера:

|

C |

D |

Q |

NQ |

Режим |

|

1 |

1 |

1 |

0 |

Установка |

|

0 |

0 |

1 |

0 |

Хранение |

|

1 |

0 |

0 |

1 |

Установка |

|

0 |

1 |

0 |

1 |

Хранение |

Временная диаграмма для синхронного D триггера:

Таблица переключений синхронного T триггера:

|

С |

Т |

Q |

NQ |

Режим |

|

1 |

1 |

1 |

0 |

Установка |

|

0 |

0 |

1 |

0 |

Хранение |

|

1 |

0 |

1 |

0 |

Хранение |

|

0 |

0 |

1 |

0 |

Хранение |

|

1 |

1 |

0 |

1 |

Установка |

Временная диаграмма для синхронного T триггера:

Таблица переключений синхронного D триггера в счетном режиме:

|

C |

Q |

NQ |

Режим |

|

1 |

1 |

0 |

Установка |

|

0 |

1 |

0 |

Хранение |

|

1 |

0 |

1 |

Установка |

|

0 |

0 |

1 |

Хранение |

Временная диаграмма для синхронного D триггера в счетном режиме:

Вывод: Мы построили модели синхронных RS, JK, D T и D (в счетном режиме) триггеров, и по показаниям индикаторов определили логику их работы.

-

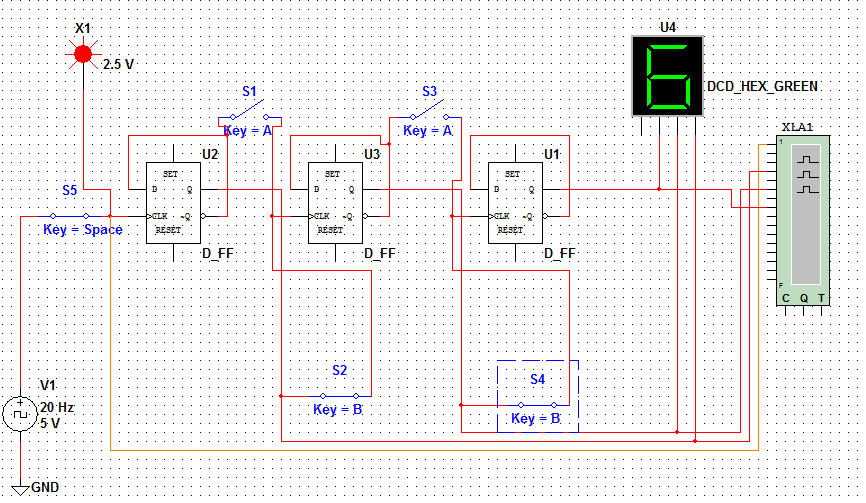

Исследование работы реверсивного счетчика на D триггерах:

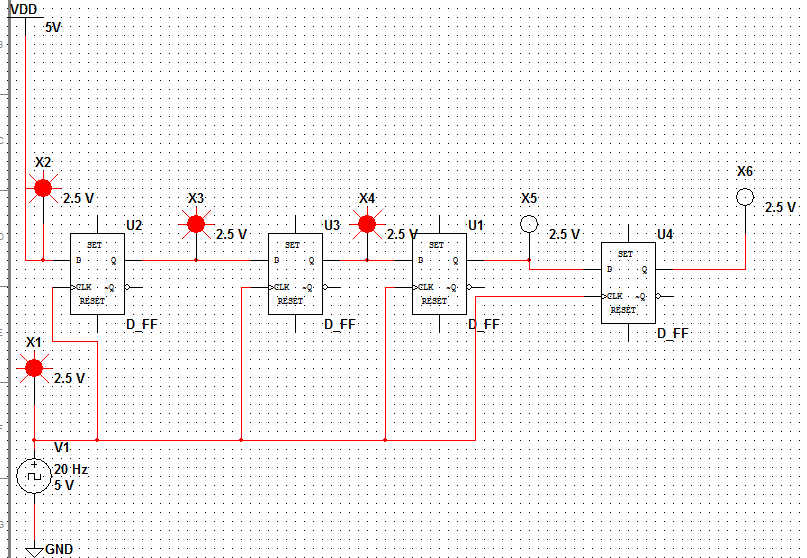

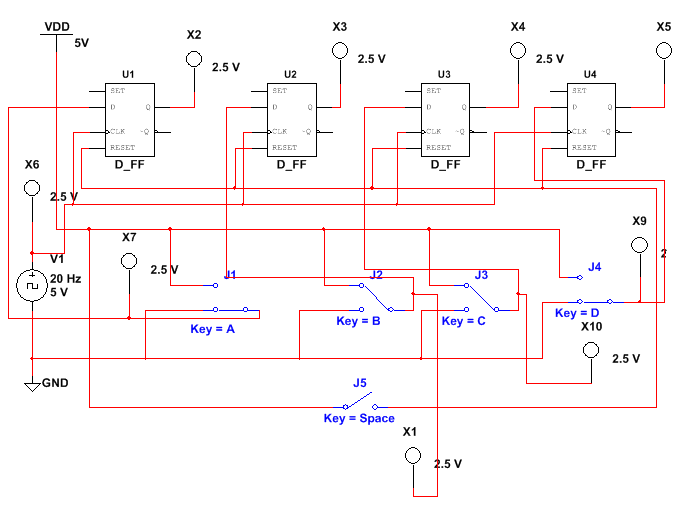

Схема для моделирования реверсивного счетчика на D триггерах

3.3

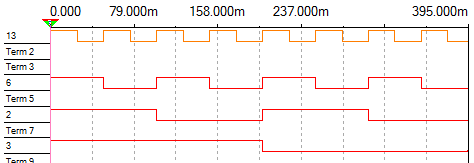

При замкнутых ключах B и разомкнутых ключах A наблюдается обратное направление счета.

3.4

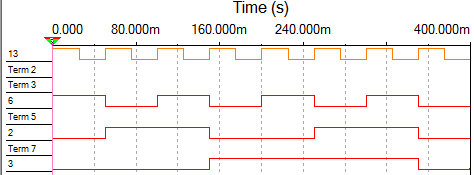

При замкнутых ключах A и разомкнутых ключах B наблюдается прямое направление счета.

3.5

Вывод: мы смоделировали реверсивный счетчик на D триггерах, изучили его поведение при различных входных сигналах на триггерах и пришли к выводу, что с помощью ключей мы можем управлять направлением счета счетчика.

-

Исследование работы интегрального суммирующего счетчика:

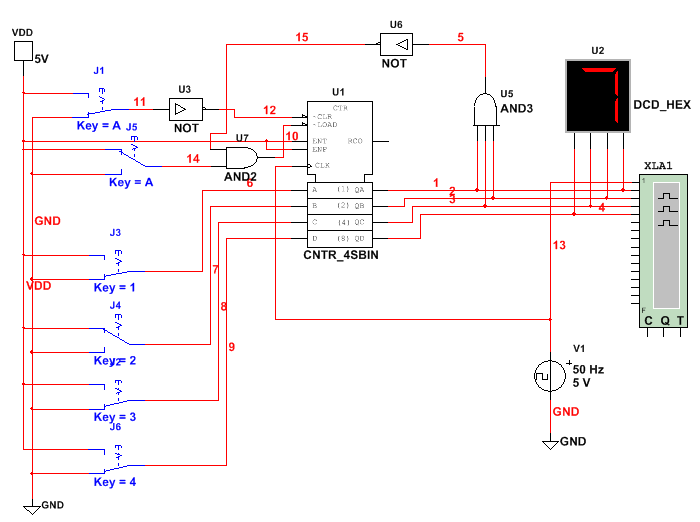

Схема для моделирования работы интегрального суммирующего счетчика

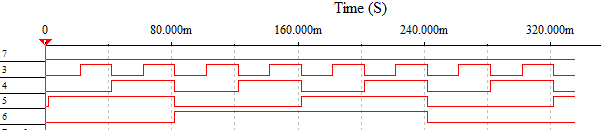

Временная диаграмма при отсчете с 0:

Временная диаграмма при отсчете с заданного значения(4):

4.5 Возможная схема суммирующего счетчика с заданным коэффициентом пересчета:

-

Исследование работы последовательного регистра

Схема для моделирования работы последовательного регистра

Таблица переключений триггеров:

|

№ синхроимпульса |

Q3 |

Q2 |

Q1 |

Q0 |

|

1 |

1 |

0 |

0 |

0 |

|

2 |

1 |

1 |

0 |

0 |

|

3 |

1 |

1 |

1 |

0 |

|

4 |

1 |

1 |

1 |

1 |

Вывод: мы исследовали работу последовательного регистра(запись логической единицы), и заполнили таблицу переключения триггеров.

-

Исследование работы параллельного регистра:

Схема для моделирования работы параллельного регистра

Таблица правил функционирования регистра:

|

A |

B |

C |

D |

CLK |

RESET |

Q3 |

Q2 |

Q1 |

Q0 |

Режим |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

Вывод: Параллельный регистр используется для хранения чисел, представленных в параллельном двоичном коде. Поэтому параллельные регистры называются еще регистрами памяти.

-

Исследование работы интегрального регистра:

Схема для моделирования работы интегрального регистра

Таблица правил функционирования регистра:

|

A |

B |

C |

D |

CKL |

CLR |

S0 |

S1 |

QA |

QB |

QC |

QD |

Режим |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

Запись |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

Запись |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

Сдвиг влево |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

Запись |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

Сдвиг вправо |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Выходы регистров недоступны |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

Запись |

|

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

Хранение |