- •Лабораторная работа Триггеры, счетчики, регистры Краткие теоретические сведения.

- •Рабочее задание.

- •Исследование работы асинхронного rs-триггера

- •2 Исследование работы синхронных триггеров

- •3 Исследование работы реверсивного счетчика на d триггерах

- •4 Исследование работы интегрального суммирующего счетчика

- •5 Исследование работы последовательного регистра

- •6 Исследование работы параллельного регистра

- •7 Исследование работы интегрального регистра

Лабораторная работа Триггеры, счетчики, регистры Краткие теоретические сведения.

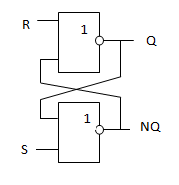

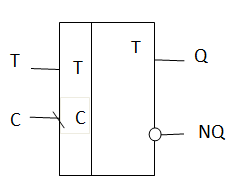

Триггер представляет собой запоминающий элемент, хранящий один бит двоичной информации. В интегральной электронике триггер может быть реализован на основе минимального логического базиса. Реализация триггера в базисе ИЛИ-НЕ представляет собой кольцевую схему соединения (Рис.1). Выходную переменную триггера обозначают Q, и ему соответствует значение сигнала на одноименном выходе. На другом выходе имеем дополняющий сигнал NQ, благодаря наличию в цепи инвертора. Если Q=1,то говорят, что триггер установлен, если Q=0, то сброшен. Входные сигналы подают на свободные (информационные) входы ЛЭ и обозначают S (Set – установка) и R (Reset – сброс). Смену устойчивых состояний триггера осуществляют подачей внешних сигналов на информационные входы.

Рис.1 Реализация триггера в базисе ИЛИ-НЕ

Название триггера содержит наименования информационных входов (RS, JK, T, D, и т.д.). Наиболее распространены различные модификации тактируемых RS- триггеров, универсальных JK триггеров, D - триггеров задержки и Т триггеров со счетным входом. Кроме информационных, триггеры могут содержать управляющие входы синхронизации и установочные входы. В основу построения большинства триггеров заложен рассмотренный выше асинхронный RS – триггер (Рис.2а). Асинхронный RS триггер реализуется с прямыми или инверсными входами. В отличие от ЛЭ, состояние выходов триггера Qn определяется не только состоянием информационных входов , но и его предыдущим состоянием Qn-1.

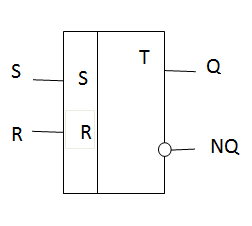

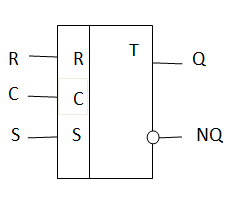

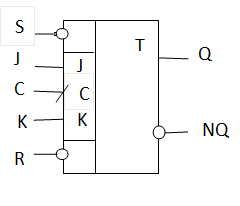

Асинхронные триггеры срабатывают в момент поступления сигналов на информационные входы. Синхронные триггеры срабатывают только в момент поступления тактирующих синхроимпульсов на вход синхронизации С. Сигналы на информационных входах устанавливают до подачи синхроимпульса. Триггер со статическим управлением синхронизируется уровнем напряжения тактирующего сигнала, т.е. может переключаться только при наличии на входе «С» соответствующего потенциала. Динамическое управление триггером может осуществляться на интервале перехода напряжения синхросигнала от U0 к U1 ( передним фронтом) или на интервале от U1 к U0 (задним фронтом) импульса синхронизации. Условные обозначения триггеров приводятся на Рис 2.

а б в

г д

Рис.2 Условные обозначения триггеров

а – асинхронный RS; б - синхронный RS со статическим управлением; в - синхронный JK c динамическим управлением по переднему фронту и установочными инверсными R и S входами; г – синхронный D (задержки) с динамическим управлением по заднему фронту и установочными инверсными R и S входами; д - синхронный Т (счетный) с динамическим управлением по заднему фронту.

Функционирование триггера отображают таблица переключений и временная диаграмма переключений. В таблице переключений различным состояниям входов соответствует состояние выходов: 1, 0, Qn, Qn-1 ,NQn , NQn-1 и режим работы триггера: установка – на выходе Q устанавливается 1 (Qn=1), сброс - на выходе Q устанавливается 0 (Qn=0), хранение – состояние триггера не изменяется (Qn =Qn-1), счетный - состояние триггера изменяется на инверсное предыдущему значение с приходом каждого синхроимпульса (Qn= NQn-1) , запрещенный – состояние триггера не определено.

Таблица переключений триггеров.

|

С |

S (J,…) |

R (K,…) |

Q |

NQ |

Режим |

|

|

|

|

|

|

|

Процесс обработки цифровых данных реализуют с помощью последовательностных цифровых устройств (ПЦУ). Структура последовательностного устройства содержит комбинационное цифровое устройство (КЦУ) и запоминающее устройство которое состоит из элементов памяти – триггеров. Типовыми последовательностными цифровыми узлами являются счетчики и регистры.

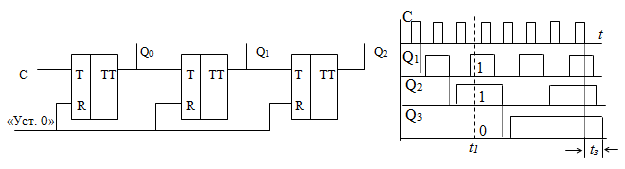

Счетчик представляет собой устройство, осуществляющее подсчет числа входных импульсов, подаваемых на синхровход, и фиксирующее это число в заданном коде. Двоичный счетчик на n – разрядов содержит n последовательно соединенных элементов счета, в качестве которых используют счетные триггеры Т – типа (Рис.3,а).

а б

Рис.3. Структура двоичного счетчика (а) и диаграммы его работы (б)

Каждый триггер образует разряд счетчика. Первый изних соответствует младшему разряду числа подсчитанных импульсов. Исходное состояние (нулевое) устанавливается подачей сигнала на все установочные входы R сброса. Двоичный счетчик с естественным порядком счета переходит к следующему значению двоичного кода на выходе при поступлении на вход единичного сигнала (Рис.3,б). В приведенной схеме триггеры изменяют свое состояние по заднему фронту синхроимпульса, сохраняя свое состояние между импульсами. Счетчик запоминает число поступивших импульсов в двоичном коде N=2n. Счетчики с произвольным модулем, т.е коэффициентом счета N 2n (например, 6; 10 и т.п.) реализуют путем исключения лишних (2n - Ксч) состояний. Этого достигают использованием комбинационной схемы или с помощью предварительной установки начального кода.

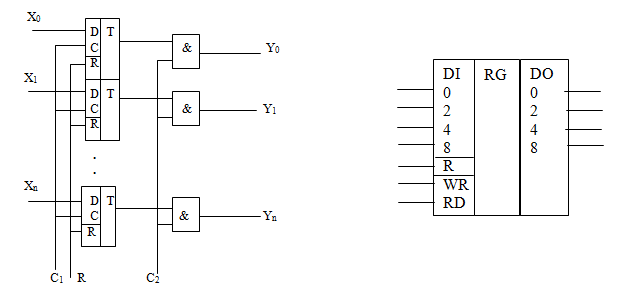

Регистр представляет собой устройство, выполняющее функции приема, хранения и выдачи информации, представленной n- разрядным двоичным словом. Структура регистра представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов регистра и схему комбинационного цифрового устройства (КЦУ), обеспечивающего выполнение логических преобразований. Среди множества регистров выделяют две основные группы, отличающиеся функциональным назначением: хранения (памяти) и сдвига.

Регистры

памяти

предназначены для хранения двоичной

информации небольшого объема: байта (8

бит) или двухбайтового слова (16 бит).

Структурно они представляют собой набор

n

синхронных триггеров для хранения n

разрядных

двоичных чисел и комбинационные схемы

совпадения для организации их записи

и чтения (Рис.4).

а б

Рис. 4 Регистр памяти: а)структура, б)обозначение.

Регистр сдвига осуществляют последовательный прием или выдачу двоичных чисел. В этих регистрах с приходом тактового импульса происходит запись разряда входной информации в первый триггер, а из других триггеров информация смещается (сдвигается) на один разряд вправо или влево в зависимости от сигнала схемы управления (Рис.5).

Рис.5 Регистр сдвига