3385

.pdf

Рис. 6.8. Управляющая панель регистратора программы Virtual Bench.

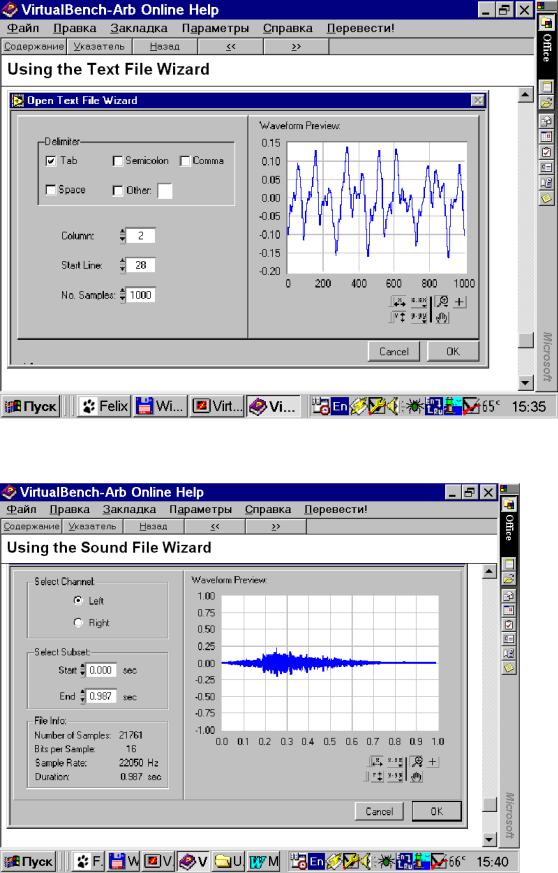

Рис.6.9. Виртуальные приборы программы VIRTUAL BENCH (Вывод текстового файла с расширением типа .txt).

Рис. 6.10. Виртуальные приборы программы VIRTUAL BENCH (файлы с расширением типа .wau).

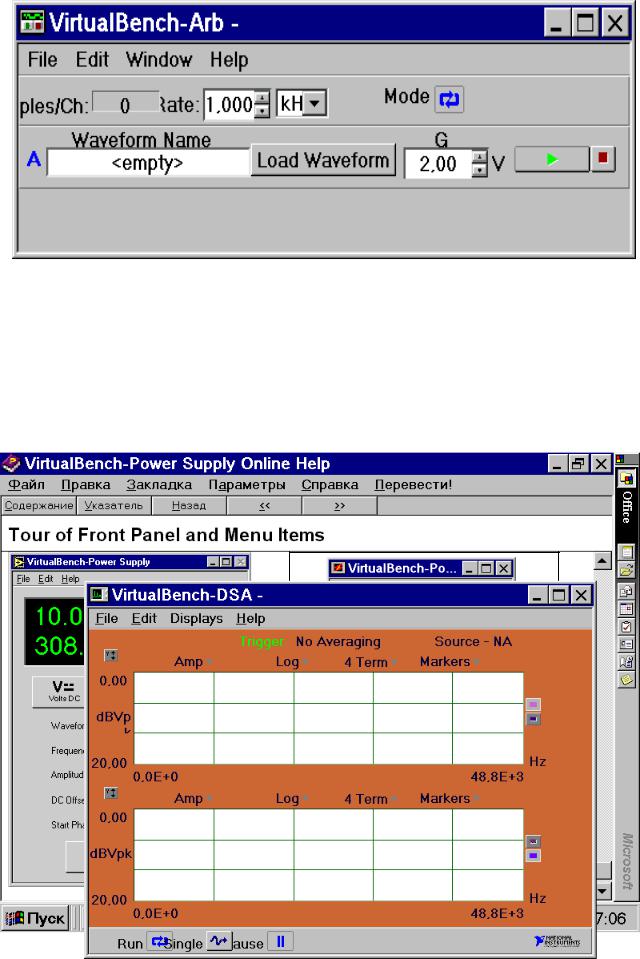

Рис.6.11. Передняя панель виртульного генератора гармонических сигналов

Рис. 6.13. Панель установки параметров аналогового анализатора

.

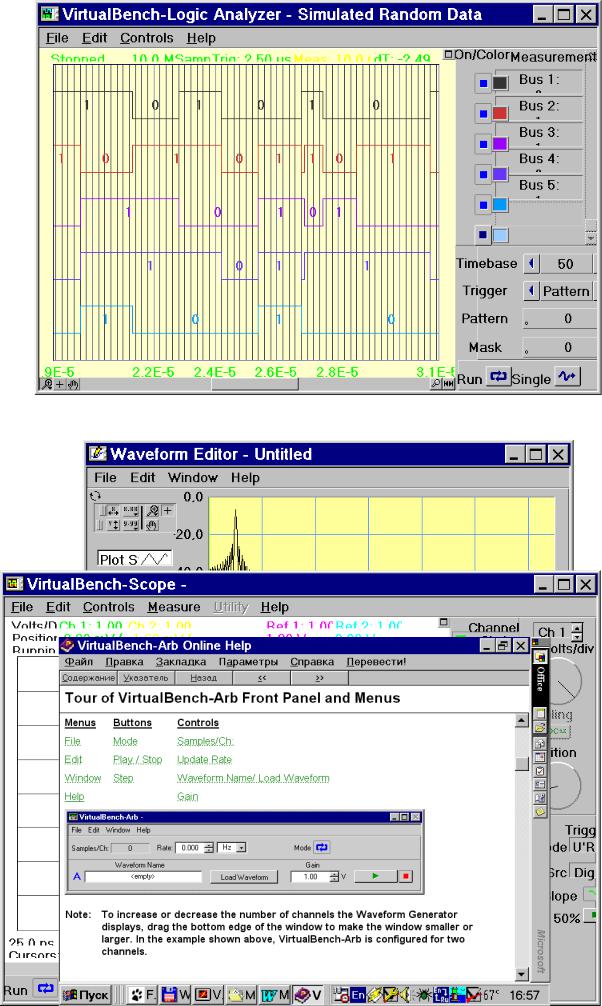

Рис. 6.14. Логический анализатор

Рис. 6.17. Описание функций генератора гармонических сигналов

6.2. Генератор импульсных сигналов высокой точности

Программа WAVE FORMER позволяет разрабатывать импульсные последовательности с привязкой их параметров к стабильным сигналам реального времени (часам). Рассмотрим кратко возможности программы, используя перевод с английского описания этого виртуального средства измерения.

Краткое описание состава программы.

SynaptiCAD предлагает пять различных программ, которые основаны на графической синхронизации и схематическом изображении редактора:

-TestBencherPro много диаграммный, само проверяющийся испытательный генератор, у которого место размещения элементов: Verilog и VHDL, генератор стимула, рассчитывающий редактор диаграмм.

-VeriLoggerPro дешев, полностью показан Verilog имитатор, который включает средство просмотра сигнала, отлаживая среду редакторов с цветным синтаксисом.

-Таблица данных обеспечивает окончательную среду для документационных профес-

сионалов, работающих с многодиаграммными проектами.

-WaveFormerPro - Интерактивный HDL имитатор, генератор стимула (VHDL, Verilog, Viewlogic, ОрКАД, и т.д.), и редактор, рассчитывающий диаграммы

-Синхронизация DiagrammerPro - основная синхронизация, схематическое изображение редактора.

Краткий обзор.

TestBencherPro - инструмент электронного цифрового анализатора (EDA) , который предназначен для производства само испытания, места размещения элементов испытания много-диаграммны для VHDL и Verilog. TestBencherPro включает в себя все особенности WaveFormerPro, рассчитывающий DiagrammerPro. С TestBencherPro пользователи делают ряд диаграмм синхронизации многократного использования (например, чтение и запись циклов), с выборками, указывающими, что должно быть сгенерировано при само испытании кода. Пользователь записывает короткий текст для места размещения элемента, который делает запросы к его диаграммам синхронизации. Это позволяет пользователю управлять последовательностью, в которой испытания диаграммы применяются на имитационную модель. TestBencherPro был представлен в 1996

ипреследуется ASIC/FPGA, микропроцессор связывает проектировщика с помощью интерфейса. Продажа в розницу $ 9,500 для Windows 95/98/NT, Solaris,

иHP-UX. См. ценовой лист для скидок объема.

VeriLoggerPro - новый тип Verilog среды моделирования, которая комбинирует все особенности традиционного Verilog имитатора с наиболее мощным графическим испытательным генератором на планете. Испытание модели про-

исходит настолько быстро в VeriLoggerPro, что вы можете использовать испытание каждой модели в вашем проекте, критический шаг, часто пропускается, чтобы торговаться. Испытательные версии могут быть импортированы или экспортироваться от анализаторов логики HEWLETT-PACKARD (HP), генераторов испытательного сигнала, и 3-ей партии VHDL, Verilog, и имитаторов SPICE для многократного использования. Особенности моделирования включают рассмотрение сигнала, оптимизированное моделирование на уровне логических элементов, пошаговую отладку, контрольные точки " направляют и щелкают ", иерархический броузер для руководства проектом, и пакетного выполнения.

Таблица данных обеспечивает более эффективной средой документационных профессионалов для управления документов, содержащих множитель, рассчитывающий диаграммы. Особенности включают связь и внедрение объектов (OLE), чтобы обеспечить непосредственную правку по месту синхронизации диаграмм, поддержки стилей таблицы, поддержки представления изображения, сеть готового формирования изображения, руководства проектом, и поддержки для промышленного стандарта, рассчитывающего язык пометок диаграмм (TDML). Таблица данных, особенностями которой позволяют пользоваться руководством проекта, объединяет диаграммы синхронизации для множественных инженеров, в один проект с одним форматированием.

Wave Former Pro позволяет вам автоматически определить критические пути, проверять границы синхронизации, корректировать переходящие эффекты разветвления на выходе, и "если что", исполнять анализ, чтобы определить оптимальную тактовую частоту. Wave Former Pro также позволяет вам определять и анализировать синхронизацию системы и исполнять моделирование уровня без потребности в схемных решениях или имитационных моделях. Когда ваша диаграмма синхронизации готова, вы только тогда можете генерировать цифровые стимулы для вашего фаворита Verilog, VHDL, SPICE или имитатора с дверным уровнем. Wave FormerPro имеет способность импортировать и аннотировать моделирование и логические данные анализатора, поскольку качество публикации проектирует документацию. Wave Former Pro включает в себя все особенности синхронизации Diagrammer Pro, плюс к этому имеет способность генерировать сигналы, использующие Булевы и временные уравне-

ния. Продажа в розницу цена за Windows 95/98/NT - $ 1,750. Для UNIX SunOS, Solaris, или HP-UX $ 3,500. См. ценовой лист для скидок объема.

Синхронизация Diagrammer Pro, рассчитана мощная, загруженная особенностью синхронизации, изображающая редактор схематически, для бюджета, начинающего инженера, будет дорого стоить. Прежде, чем вы примете схемное решение, анализируйте ваш проект на ранних стадиях. Выполните полнофункциональный временной анализ минимума / максимума, чтобы устранить все нарушения синхронизации и условия состояния. Синхронизация Diagrammer Prо автоматически вычисляет критические пути и корректирует переходящие разветвления на выходе. Вставка диаграмм в текстовые процессоры простая, благодаря разнообразию форматов сбора данных изображения, включая WMF метафайлы, метафайлы машинной графики (CGM), расширенные ме-

тафайлы, EPS файлы, и MIF файлы. Включает связанные библиотеки параметров синхронизации. Синхронизация DiagrammerPro была представлена в 1994.

Розничная цена - $ 975 для Windows 95/98/NT.

Как выбрать программу для себя.

TestBencherPro: Если вы моделируете проекты в VHDL или Verilog, и тратите впустую время, для размещения элементов, чтобы моделировать части системы, для которой вы не имеете полных моделей (например, интерфейсы шины, интерфейсы микропроцессора, заказные специализированные интегральные схемы), тогда покупайте TestBencherPrо. TestBencherPrо даст вам простой способ графически проектировать испытательные места для размещения элементов многократного использования. Оценивание TestBencherPro как много диаграммную, само проверяющую особенности HDL делают TestBencherPrо одной из обучающих программ, расположенных в каталоге: tutb5a.doc для VHDL и tutb5b.doc для Verilog. Для полного списка особенностей

TestBencherPro, посетите наш сайт в сети в http://www.syncad.com/.

WaveFormerPro: Если вы используете имитатор, чтобы проверить ваши проекты, но не нуждаетесь в генерировании ваших собственных шин функциональной модели, то покупайте WaveFormerPro. С WaveFormer вы будете способны графически использовать сигнал и импорт / экспорт данных синхронизации в различных формах имитатора типа VHDL, Verilog, Viewlogic, ОрКАД, SPICE, и других имитаторах. WaveFormerPro использует язык созданий сценария, чтобы импортировать / экспортировать данные синхронизации, так что вы можете разрабатывать сценарии, чтобы поддержать внутренние имитаторы. Посетите наш участок сети для самых новых сценариев имитатора.

WaveFormerPro: Если вы используете испытательное оборудование, чтобы фиксировать данные синхронизации от ваших проектов / систем, то покупайте WaveFormerPro. С WaveFormerPro вы будете способны импортировать данные синхронизации в WaveFormer для анализа документации или для преобразования в различные форматы имитатора. WaveFormerPro использует открытый формат создания сценария, чтобы исполнить его функции импорта, так что вы сможете записывать сценарии, чтобы поддержать внутреннее испытание и оборудование сбора данных. WaveFormerPrо в настоящее время поддерживает Pod-A-Lyzer и Hewlett-Packard, поддержка осуществляется для другого популярного испытательного оборудования.

WaveFormerPro: Если вы хотите чрезвычайно быструю, чрезвычайно удобную среду моделирования для схем с дверным уровнем, то покупаете WaveFormerPrо. WaveFormerPrо содержит HDL двигатель моделирования, плюс логический мастер, который упрощает HDL генерацию объектного кода для схем с дверным уровнем (Булевы уравнения, регистраторы, и замки). Для подробной информации относительно этих особенностей см. продвинутую обучающую программу в tutadv.wri файле.

Синхронизация DiagrammerPrо: Если вы хотите быстро рисовать и анализировать синхронизацию системы, используя инструмент проекта профес-

сионального качества, но не моделируя проект, и все сигналы будут выполнены вручную, то сделайте покупку DiagrammerPrо.

Синхронизация DiagrammerPrо: Если вы хотите быть способным и быстро документировать вашу синхронизацию системы. Все три программы позволяют рассчитывать диаграммы, которые будут преобразованы в WMF метафайлы, метафайлы машинной графики, расширенные метафайлы, EPS файлы с предварительными просмотрами, FrameMaker MIF файлы, и режим точного отображения (WYSIWYG) точечного рисунка. Вы можете легко изображать диаграммы синхронизации в документы обработки текстов, электронные таблицы, и программы настольной издательской системы типа FrameMaker, PageMaker, и Corel Draw.

Все программы SynaptiCAD с тем же самым номером выпуска - совместимый файл.

Все программы SynaptiCAD отправлены с нашими стандартными частями библиотеки и X86 библиотеками.

Все программы SynaptiCAD поддерживают TDML стандарт, используемый ECIX интерактивные листы данных.

TestBencherPro, VeriLoggerPro, WaveFormerPro, и DiagrammerPro все ос-

нованы на объектно-ориентированной синхронизации, изображают схематически редактора, рисунок, команды редактирования. Несколько окон, которые вы будете использовать, содержат особенность справки контекста, которая позволит вам выполнять больше определенных действий, которые вы выполняете. Эта форма справки очень полезна в разрешении, чтобы иметь практическое введение, также как разрешение, чтобы получить переход непосредственно к более глубокой информации в соответствующем руководстве. Окна с этой особенностью имеют маленькую кнопку с вопросительным знаком в правом верхнем углу окна (рядом с близкой кнопкой). Чтобы использовать особенность, нажмите вопросительный знак, и затем нажмите пункт в окне, относительно которого Вы хотели бы видеть справку.

Основной рисунок и команды редактирования.

-Используем Add Signal or Add Clock для добавления сигнала и часов.

-Используем левую кнопку мыши, чтобы рисовать долю сигнала с конца сигнала к

курсору мыши. Тип оттянутого сигнала определяется красной кнопкой (высоко, низко, и т.д.). Кнопки переключаются автоматически. Состояние с маленьким красным "T" выше названия - состояние переключателя.

-Двойной левый щелчок на объекте для того, чтобы редактировать свойства объекта.

-Drag-n-Drop, используем для того, чтобы переместить объекты.

Главы 4, 5, и 6 охватывают основные особенности временного анализа, выполненные, помещая параметры подобно задержкам, установкам, проводя и производя выборку на диаграмме синхронизации. Эти параметры определяют причинные отношения между гранями сигнала. Правая кнопка мыши используется для того, чтобы добавить параметры и несколько других объектов подобно маркерам и тексту. Большинство времени будет потрачено, на рисование или

редактирование сигнала, используя левую кнопку мыши: правой кнопки мыши можно управлять рисунком, сохранять время.

Добавление параметров синхронизации.

-Левый щелчок на одной из кнопок устанавливает, проводит, производит выборку, маркер, чтобы активизировать режим (кнопка станет красной).

-В одном из режимов параметра (задержка, установка, счет или выборка), левый один щелчок на переходе выбирает, правый щелчок на втором переходе, нужен для того, чтобы добавлять параметры между первыми и вторыми переходами.

-В текстовом режиме или режиме маркера, нажмите правую кнопку мыши, чтобы добавить объект.

Глава 12 описывает временной анализ, который поддерживается через интерактивный HDL модуль моделирования, включенный с Wave Former Pro и TestBencherPro. Интерактивный HDL имитатор поддерживает поведенческий код HDL, Булевы уравнения, и истинное моделирование минимума/максимума. Изменения во входных сигналах автоматически вызывают пере моделирование.

Особенности моделирования, с помощью окно свойств сигнала:

-Двойной левый щелчок на сигнале используется, чтобы открыть окно свойств сигнала.

-Использовать Булевы уравнения или окна редактирования кода HDL, нужно чтобы определить моделирование для сигнала.

-Проверим флажок Simulated Signal, чтобы непрерывно моделировать

сигнал.

Главы 7, 8, и 9 охватывают изображение, печать, и диаграмму синхронизации, форматирующую особенности. Все три программы обеспечивают 6 различных методов для герметизации, рассчитывающих изображения диаграммы в документы и программы размещения страницы. Все основанные загрузочные модули можно сгенерировать, используя команды File>Print: WMF, метафайл машинной графики, и EMF метафайлы, FrameMaker MIF файлы, и EPS с предварительными просмотрами. Команда Edit>Copy-to-Clipboard создает изображение Windows текущего окна, которое является совместимым с почти всеми программами Windows. Также поддержан новый промышленный стандарт формата TDML и OLE.

Более поздние главы охватывают более продвинутые типы сигнала, которые вычисляют их собственные сигналы или отображают специализированную информацию:

-Часы, повторные формы волны, охвачены во второй главе: Часы.

-Моделируемые и виртуальные шины, сигналы, значение их дисплея, охвачены в главе 3: Моделируемые и виртуальные шины.

-Моделируемые сигналы, которые вычисляют формы волн, основанные на булевых уравнениях и на коде HDL, охвачены в главе 12: Интерактивное HDL моделирование.

Функции, сигнала и рисунка:

6.2.1 Добавление и удаление сигналов.

6.2.2Редактирование свойств сигнала.

6.2.3Сигнал.

6.2.4Редактирование сигнала с помощью мыши.

6.2.5Редактирование сигнала, использование окна.

6.2.6Редактирование граней сигнала.

6.2.7Перемещение сигнала.

6.2.8Сокрытие и показ сигналов.

6.2.9Копия сигнала.

6.2.10Копирование и вставка сигналов.

6.2.11Авто обозначение сигналов.

6.2.1. Добавление и удаление сигналов.

Добавление нового сигнала:

-Левой кнопкой щелкнуть на Add Signal. Удаление сигнала:

-Выбираем имя сигнала, левым щелчком нажав на него. Имя выбранного сигнала будет высвечено.

-Нажимаем на удаляющийся сигнала, включаем клавиатуру или выбираем

Edit>Delete.

Обратите внимание: когда сигнал удален, любые параметры или текст, связанные с этим сигналом также удалены. Если вы делаете ошибки, вы можете отменить удаляющийся сигнал, выбирая Edit>Undo или Edit> Undo Delete.

6.2.2. Редактирование свойств сигнала.

Редактирование свойств сигнала (имя, Булево уравнение, экспорт, направление, тип):

-Двойной левый щелчок, чтобы открыть окно Signal Properties.

-Вводим новые данные, и нажимаем OK, чтобы закрыть окно.

Обратите внимание: свойства нескольких сигналов могут быть отредактированы в то же самое время, тогда как выберите сигнал, нажимая в окне Label и Edit меню отобранный сигнал.

Имеются четыре входных секции в окне Signal Properties:

1) Секция имени: будет иметь заданное по умолчанию имя. Имена должны быть, по крайней мере, одним символом (пробелы позволяются). Имя сигнала, начинающееся с "$$" зарезервировано для внутреннего использования. Имя сигнала не должны начаться с цифры или содержать математические операторы. Имя сигнала не должны быть оператором Boolean.

Активный низкий переключатель имени: Если к имени сигнала добав-

лено с $BAR в конец, и сигнал отображен с областью имени. Если активный низкий сигнал используется в уравнении другого сигнала, то имя активного низкого сигнала – name $BAR.

Аналоговая кнопка Properties: Открывает аналоговые свойства (переход к новой странице SPICE) окна, которое позволяет, чтобы вы установили логи-

ческое напряжение, выравнили повышение / падение времени, используемое SPICE. Имеется также кнопка Properties, которая открывает общее окно Object Properties. Это - продвинутая особенность, которая является доступной пользователям, пишущим сценарии Perl, чтобы поддержать память определенных атрибутов пользователя, приложенных к объектам WaveFormer. Для подробной информации читайте главу 14: Свойства объекта.

Кнопка линии координатной сетки: открывает окно сетки, который оп-

ределяет, как рисовать вертикальные строки от граней сигнала.

2) Логическая секция мастера: В WaveFormerPro и TestBencherPro, сиг-

нал может быть описан как зарегистрированное Булево уравнение других сигналов. Определите Булево уравнение, рассчитывая информацию, и тип регистра, используя окно. Нажмите на кнопку Simulate Once, чтобы видеть результаты. Выберите кнопку "радио" для автоматического пере моделирования. Состояние диска - заданное по умолчанию состояние для сигналов, используется, чтобы описать сигналы, которые оттянуты пользователем. Используется состояние часов, чтобы рассмотреть сигналы, внедренные во внешние модели.

Для подробной информации читайте главу 12: Интерактивное HDL моделирование. 3) Временная секция уравнения: сигнал может быть сгенерирован, используя временное уравнение. Используя уравнение сигнала, он будет помечен. Для подробной информации читайте главу 11: Порождение уравнения сигнала.

4) Экспортная секция свойств: Эти свойства затрагивает, как WaveFormerPro, так и TestBencherPro. Они также затрагивают, как отображены значения сигнала.

-Экспортный флажок Signal определяет, действительно ли сигнал будет экспортироваться в стимул и испытательные файлы.

-Аналог Diaplay: переключатель This используется, чтобы определить - будет ли ото-

бранный сигнал, отображен как аналоговый сигнал или нет.

-Направление: Используется для экспорта VHDL или кода Verilog. См. TestBencher pro руководство для подробной информации.

-Отношение размера: Используют, чтобы определить высоту дисплея fo сигнал.

-VHDL: и Verilog: Определяет тип HDL сигнала (например, std_logic, целого числа, провода). Пользователь может также вводить новый тип в раскрывающееся окно редактирования. VHDL и Verilog списки хронологии могут быть перестроены, редактируя .ini файл (waveform.ini для WaveFormerPro, и tbench.ini для TestBencherPro) расположенного в каталоге Windows. Убедитесь, что программа не выполняется, когда вы редактируете ее .ini файл

-Шина MSB и LSB: Определите разрядный размер сигнала. Единственный разрядный сигнал - (0,0). Это используется интерактивным HDL имитатором, чтобы определить результат много разрядных операций. Это также используется в течение экспорта VHDL или Verilog файлов стимула и испытательных мест для размещения элементов, чтобы определить, как инициализировать сигнал в модели HDL.