.Проектирование устройств и систем с высокоскоростными соединениями

.pdf

Рис. 6.31. Делитель тактовых частот для последовательных и параллельных данных

Узел анализа запаса устойчивого приема. Поскольку ско-

рость передачи и ослабление в канале увеличиваются, то для уменьшения ослабления все чаще задействуется встроенный эквалайзер. Это делает проблематичным определение качества канала на его дальнем конце с помощью измерения раскрыва глаза на выводах приемника микросхемы. Поэтому в приемник встроен механизм сканирования глаза, позволяющий измерять и визуализировать запас устойчивого приема как с эквалайзером, так и при его отключении.

Сигнал RXDATA восстанавливается путем стробирования из скорректированного эквалайзером дифференциального сигнала линии передачи. Позиция горизонтального стробирования определяется узлом CDR, а вертикальная является дифференциальным нулем (рис. 6.32).

Функция сканирования выполняет дополнительное стробирование с программируемым смещением (вертикальным и горизонтальным) относительно точки стробирования данных.

161

Рис. 6.32. Стробирование данных, смещенное стробирование

В процессе каждого измерения увеличивается на единицу счетчик числа стробов данных и счетчик ошибок, если значение в точке смещения не соответствует значению в центральной точке. Величина BER для программируемого смещения определяется как отношение значения счетчика ошибок к значению счетчика числа стробов. Величина счетчика стробов может быть от десятков тысяч до величины, большей 1014. Выполняя такие измерения для полного множества горизонтальных и вертикальных смещений (или их подмножества), можно получить карту BER для глаза. Через атрибут ES_HORZ_OFFSET задается задержка момента появления смещенного строба относительно строба данных. Через атрибут ES_VERT_OFFSET повышается или понижается уровень порога дифференциального напряжения, с которым сравнивается скорректированный входной сигнал.

Узел контроля тестовых последовательностей. Для про-

верки целостности сигнала в канале приемник содержит встроенный контроль стандартных PRBS-последовательностей, генерируемых передатчиком. Встроенный контроль является самосинхронизируемым и работает с битовыми последовательностями перед их выравниванием.

Выравнивание по границе слова. Последовательные дан-

ные на приеме должны быть выровнены по границе слова перед их преобразованием в параллельный вид. Для этого передатчик посылает распознаваемую последовательность, обычно называемую «запятая» (разделитель). Приемник осуществляет поиск за-

162

пятой во входных данных. Когда она находится, приемник смещает границу символов так, чтобы она соответствовала границе параллельных данных на передаче. На рис. 6.33 приведен пример выравнивания с помощью 10-битной запятой вида 0101111100.

Рис. 6.33. Выравнивание с помощью 10-битной запятой

Через атрибуты ALIGN_MCOMMA_VALUE и ALIGN_ PCOMMA_VALUE задается комбинация 0 и 1 для запятой, а атрибут ALIGN_COMMA_ENABLE – маска действительных бит запятой.

Декодирование 8B/10B (8B/10B Decoder). Приемник со-

держит встроенный декодер кода 8B/10B, состоящий из четырех однобайтных модулей декодера 8B/10B. Декодер обеспечивает 2, 4 и 8-байтные операции, генерацию К-символов, удаление 10битных символов, отсутствующих в таблице кода, сцепление гирлянды из компонент текущего дисбаланса. Через интерфейс RXCHARISCOMMA[7:0] сообщается о том, что соответствующий параллельный байт данных на интерфейсе RXDATA является запятой. Через интерфейс RXCHARISK[7:0] сообщается о том, что соответствующий параллельный байт данных на интерфейсе RXDATA является К-символом.

Эластичный буфер приемника (RX Elastic Buffer). При-

емник имеет два внутренних домена тактовых частот для параллельных данных, используемых в подуровне PCS: домен частоты XCLK PMA и домен частоты RXUSRCLK PCS. Для приема данных XCLK и RXUSRCLK должны быть достаточно близкими. Для решения проблемы в разнице между XCLK и RXUSRCLK используется эластичный буфер.

163

Коррекция тактовой частоты на приеме. Эластичный буфер является мостом между двумя разными доменами тактовой частоты RXUSRCLK и XCLK, выделенными узлом CDR из входных данных. Даже если RXUSRCLK и XCLK получены из одной тактовой частоты, между ними всегда существует некоторая разница, которая постепенно накапливается и, очевидно, может привести к переполнению буфера или его опустошению, если не делать коррекцию. Для коррекции передатчик периодически посылает один или два специальных символа, которые приемник при необходимости или удаляет, если эластичный буфер полностью заполнен, или дублирует, если эластичный буфер становится пустым. На рис. 6.34 представлена работа этого механизма.

Рис. 6.34. Механизм коррекции тактовой частоты

Связывание канала (RX Channel Bonding). Такие прото-

колы, как XAUI и PCI Express, объединяют несколько соединений трансиверов для создания одного канала с высокой пропускной способностью. Каждое такое соединение трансиверов на-

164

зывают дорожкой (lane). Даже если каждое последовательное соединение имеет одинаковую длину, перекос между дорожками может привести к тому, что данные, переданные одновременно, достигнут приемника в разное время. Механизм связывания канала нейтрализует этот перекос, используя эластичный буфер как узел с переменной задержкой. Для связывания канала передатчики используют одновременную отправку специальных символов или их последовательность (SEQ). Приемники, получая эту последовательность, могут определить перекос между дорожками и подстроить задержку эластичного буфера так, что данные будут переданы в микроструктуру FPGA без перекоса (Deskew), как показано на рис. 6.35.

Связывание канала поддерживается только для кода 8B/10B. В канале одна дорожка является ведущей (Mater), а остальные – ведомыми (Save). Через интерфейсы RXCHBONDI [4:0] (выход) и RXCHBONDO[4:0] (вход) ведомые по цепочке получают от ведущего необходимую информацию для связывания. Через группу 10-разрядных атрибут CHAN_BOND_SEQ задается вид последовательности SEQ.

Рис. 6.35. Механим связывания канала

165

«Коробка скоростей» приемника (RX Gearbox). Коробка скоростей на приеме поддерживает разделение заголовка и нагрузки для кодов 64B/66B и 64B/67B. Интерфейс коробки скоростей приемника и микроструктуры FPGA содержит такие сигналы, как:

•выходы коробки скоростей RXDATA[63:0] и RXHEADER[2:0] – данные и заголовок;

•выходы коробки скоростей RXHEADERVALID и RXDATAVALID свидетельствуют о действительности заголов-

ка и данных;

• выход RXGEARBOXSLIP микроструктуры FPGA используется для сдвига данных коробки скоростей цикл за циклом до тех пор, пока не будет достигнуто корректное выравнивание.

Дескремблирование данных и блочная синхронизация выполняется микроструктурой FPGA.

Интерфейс между микроструктурой FPGA и приемни-

ком RX (FPGA RX Interface). Параллельные данные из приемника MGT записываются в порт RXDATA по положительному фронту сигнала RXUSRCLK2. Разрядность порта может быть сконфигурирована как 2, 4 или 8 байт. Реальная разрядность за-

висит от атрибутов RX_DATA_WIDTH и RX_INT_DATAWIDTH

и значения порта RX8B10BEN. Таким образом, разрядность порта может быть 16, 20, 32, 40, 64 или 80 бит. Значение тактовой частоты параллельных данных RXUSRCLK2 определяется скоростью передачи по последовательному каналу RX, разрядностью порта RXDATA и значением порта RX8B10BEN.

6.4. ПРИМЕР РЕАЛИЗАЦИИ ПОЛЬЗОВАТЕЛЬСКОГО ПРОТОКОЛА НА XILINX 7 SERIES

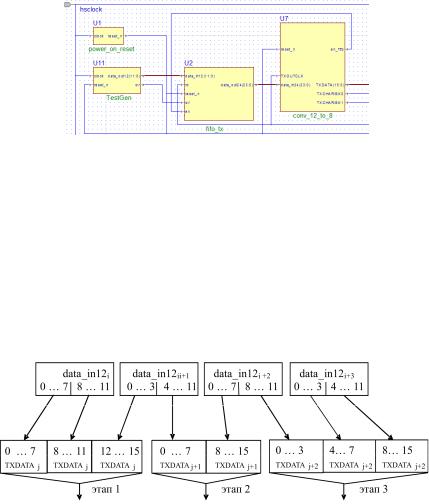

Рассмотрим реализацию на FPGA Xilinx 7 series пользовательского протокола из примера в подразд. 3.1.2. В дальнейшем этот проект будем называть третьим (#3). На рис. 6.36 приведена структурная схема передающей части пользовательского протокола проекта #3.

Узел power_on_reset моделирует формирование сигнала сброса при включении питания, а узел TestGen введен для отладки проекта средствами моделирования и представляет собой генератор тестовых последовательностей. MGT FPGA Xilinx 7

166

series уже содержит узел кодирования 8B/10B. Минимальная ширина данных интерфейса микроструктуры FPGA и MGT составляет 16 бит. Поэтому в проекте необходимо предусмотреть лишь узлы для согласования 12-разрядных данных с 16-разряд-

ным интерфейсом MGT – FIFO_Tx и conv_12_to_8.

Рис. 6.36. Структурная схема передающей части пользовательского протокола проекта #3

На рис. 6.37 приведена трехэтапная схема, по которой узел conv_12_to_8 преобразует четыре 12-разрядных слова в три 16-раз- рядные слова данных для передачи на подуровень PCS MGT.

Как видно из этой схемы, для получения одного 16-разряд- ного символа необходимы два соседних 12-разрядных символа. Поэтому выход данных data_out24 узла FIFO_Tx является 24-разрядным, тогда как на его вход data_in12 поступают 12-раз- рядные данные. Ниже приведена синтезируемая VHDL-модель узла FIFO_Tx, построенная по принципу удвоения памяти.

Рис. 6.37. Схема преобразования 4 слов по 12 разрядов в 3 слова по 16 разрядов

167

VHDL программа-спецификация узла FIFO_Tx проекта #3

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all; entity FIFO_Tx is

port(

reset_n : in STD_LOGIC; wr : in STD_LOGIC;

rd : in STD_LOGIC; en : in STD_LOGIC;

data_in12 : in STD_LOGIC_VECTOR(11 downto 0); data_out24 : out STD_LOGIC_VECTOR(23 downto 0)

); end FIFO_Tx;

architecture FIFO_Tx of FIFO_Tx is

type TYPE_FIFO is array (0 to 3) of STD_LOGIC_VECTOR(11 downto 0); signal FIFO: TYPE_FIFO;

signal FIFO_out: TYPE_FIFO;

signal addr_cnt_rd:STD_LOGIC_VECTOR(1 downto 0); begin

FIFO_WITE: process(reset_n,wr) begin

if reset_n='0' then FIFO(0)<=(others=>'0'); FIFO(1)<=(others=>'0'); FIFO(2)<=(others=>'0');

FIFO(3)<=(others=>'0');

elsif rising_edge(wr) then -- Реализация магазинной памяти в виде регистра

FIFO(0)<=data_in12; -- сдвига при записи данных

FIFO(1)<=FIFO(0);

FIFO(2)<=FIFO(1);

FIFO(3)<=FIFO(2); end if;

end process;

NEXT_ADDRESS:

process(reset_n,rd, en) -- Формирование указателя addr_cnt_rd при чтении данных

begin -- из магазинной памяти if reset_n='0' or en='0' then

addr_cnt_rd<=(others=>'0'); elsif falling_edge(rd) then

168

if en='1' then addr_cnt_rd<=addr_cnt_rd+2;

end if; end if;

end process;

FIFO_to_ FIFO_out: -- Реализация удвоения памяти FIFO_out – FIFO process(reset_n,en)

begin

if reset_n='0' then FIFO_out(0)<=(others=>'0'); FIFO_out(1)<=(others=>'0'); FIFO_out(2)<=(others=>'0'); FIFO_out(3)<=(others=>'0');

elsif rising_edge(en) then FIFO_out(0)<=FIFO(3); FIFO_out(1)<=FIFO(2); FIFO_out(2)<=FIFO(1); FIFO_out(3)<=FIFO(0);

end if;

end process;

FIFO_out_READ: --Чтение 24-разрядных данных из двух соседних ячеек

FIFO_out process(reset_n,rd) begin

if reset_n='0' then data_out24<=(others=>'0');

elsif rising_edge(rd) then if en='1' then

data_out24(11 DOWNto 0)<= FIFO_out(conv_integer(addr_cnt_rd)); data_out24(23 DOWNto 12)<= FIFO_out(conv_integer(addr_

cnt_rd+1)); end if;

end if; end process; end FIFO_Tx;

12-разрядныые входные данные data_in12 по положительному фронту сигнала wr запоминаются в памяти магазинного типа FIFO емкостью четыре слова (процесс FIFO_WITE). В соответствии со схемой преобразования именно четыре последовательных 12-разрядных слова данных преобразуются в три последовательных 16-разрядных слова (шесть символов кода 8B/10B). По положительному фронту en данные из FIFO копируются в FIFO_out с организацией 2 слова по 24 разряда (про-

169

цесс FIFO_to_ FIFO_out). В процессе FIFO_out_READ данные из текущего слова FIFO_out по положительному фронту rd читаются на выход data_out24. Такая организация узла с удвоенной памятью позволяет максимально изолировать поток записи от потока чтения.

Узел conv_12_to_8 по сигналу TXOUTCLK передатчика MGT устанавливает на 16-разрядном выходе TXDATA данные для передачи по высокоскоростному каналу, прочитанные из FIFO_Tx и преобразованные в соответствии со схемой на рис. 6.37. Ниже приведена синтезируемая VHDL-модель узла

conv_12_to_8.

VHDL программа-спецификация узла conv_12_to_8

library IEEE;

use IEEE.STD_LOGIC_1164.all; use IEEE.NUMERIC_STD.all; entity conv_12_to_8 is

port(

reset_n : in STD_LOGIC; TXOUTCLK: in STD_LOGIC; en_fifo : out STD_LOGIC;

data_in24 : in STD_LOGIC_VECTOR(23 downto 0); TXCHARISK0,TXCHARISK1 : out STD_LOGIC; TXDATA : out STD_LOGIC_VECTOR(15 downto 0)

);

end conv_12_to_8;

architecture conv_12_to_8 of conv_12_to_8 is signal buff: STD_LOGIC_VECTOR(15 downto 0);

type TYPE_STATE is (SF, DATA0, DATA1, DATA2, EF, IDLE); signal state: TYPE_STATE;

signal symbol_counter:unsigned(2 downto 0);

begin

STATE_MACHINE: --Автомат управления узла process(TXOUTCLK,reset_n)

begin

if reset_n='0' then state<=SF;

symbol_counter<=(others=>'0'); en_fifo<='0';

elsif falling_edge(TXOUTCLK) then case state is

when SF =>

170