.Проектирование устройств и систем с высокоскоростными соединениями

.pdf5.3.ТЕСТИРОВАНИЕ ПЕЧАТНОЙ ПЛАТЫ

СВЫСОКОСКОРОСТНЫМИ СИГНАЛАМИ

5.3.1. Измерение BER

Искажения бит при передаче сигналов оценивают с помощью коэффициента битовых ошибок (BER – Bit Error Ratio). Так, значение BER в 10−4 говорит о том, что в среднем из 10 000 бит искажается значение одного бита. Значение BER для печатной платой с высокоскоростными сигналами можно считать интегральным показателем качества ее разработки. На рис. 5.12 приведен пример схемы измерения BER для оценочной платы ML321, содержащей FPGA с MGT, работающих на частоте 3,2 Гбит/с. Схема содержит следующие устройства:

1)N5182A (Agilent) – векторный генератор 100 кГц – 6 ГГц;

2)HFS9003 (Tektronix) – 12-канальный генератор импульсов, 50 кГц – 630 МГц;

3)Infiniium DCA-X 86100D (Agilent) – широкополосный

осциллограф (анализатор цифровых систем связи):

•режим осциллографа – точное измерение параметров сиг-

налов;

•режим глаз-диаграммы/испытаний на соответствие маске – быстрое и точное тестирование приемопередатчиков на соответствие требованиям стандартов;

•режим рефлектометра во временной области – точное измерение импеданса и S-параметров;

•режим измерения амплитуды и джиттера;

•опция встроенного прецизионного опорного генератора обеспечивает величину джиттера менее 100 фс и поддержку большого числа каналов;

4) N4906B (Agilent) – BER-тестер, содержащий генератор

испытательного сигнала (до 12,5 Гбит/с) и детектор ошибок;

5) ML321 (Xilinx) – плата для исследования и эксперимен-

тирования с |

FPGA Virtex®-II Pro RocketIO™ |

с MGT, |

622 Мбит/с – |

3,125 Гбит/с, уровень предыскажения |

от 10 до |

33 %, перепад напряжения на дифференциальном выходе от 400 до 800 мВ. BREFCLK – вход с наименьшим джиттером для подачи опорной тактовой частоты, но с ограниченной гибкостью изза более высокой стоимости реализации.

121

Рис. 5.12. Пример тестера печатной платы с микрополосковыми линиями

На вход синхронизации BREFCLK платы ML321 подается опорная тактовая частота 160 МГц с малым джиттером от системного задающего генератора Tektronix HFS9003, а также на вход запуска широкополосного осциллографа DCA-X 86100D. Опорная частота 10 МГц для Tektronix HFS9003 поступает от векторного генератора N5182A, который также является источником тактовой частоты 3,2 ГГц для BER-тестера. BER-тестер на этой частоте формирует псевдослучайную последовательность, которая по дифференциальной паре поступает на вход оценочной платы ML321. Выходной сигнал ML321 может быть подключен к BER-тестеру для подсчета ошибок или к осциллографу для формирования глаз-диаграммы.

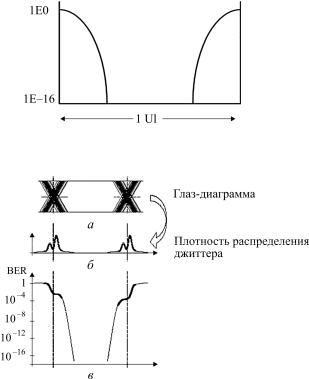

BER-тестер может сформировать результат в виде U-диа- граммы (рис. 5.13).

U-диаграмма показывает битовые ошибки относительно отсчетов внутри единичного (битового) интервала UI. Нижняя часть диаграммы не достигает нулевого значения, а останавливается на уровне 10–12–10–16 (измерение начинается с присвоения единичного начального значения счетчику ошибок), верхняя граница равна 1. В некоторых случаях зависимость между глаз-

122

диаграммой и U-диаграммой формируют в виде WaveCrest («гребень волны»), как показано на рис. 5.14. Эта зависимость будет действительной только при определенных условиях. U-диаграм- ма или BER будут недействительными, если они выведены из глаз-диаграммы для пути прохождения сигнала, внешнего по отношению к MGT с активным эквалайзером.

Рис. 5.13. U-диаграмма

Рис. 5.14. WaveCrest. Взаимосвязь между глаз-диаграммой, распределением джиттера и U-диаграммой: а – глаз-диаграмма показывает пороговые значения сигналов при передаче данных;

б– плотность распределения джиттера (толстая линия)

иее экстраполяция (тонкая линия); в – U-диаграмма

выводится из плотности распределения джиттера (толстая линия) и ее экстраполяции (тонкая линия)

123

Опыт отладки устройств с высокоскоростными сигналами позволил сформулировать подсказки, позволяющие разработчикам преодолевать возникающие проблемы.

Низкий уровень сигнала на выводах приемника. Если ам-

плитуда сигнала очень мала, то можно повысить напряжение на выходе драйвера. Если нет возможности исправить проблему с выходом драйвера, то в этом случае возникает необходимость выполнения аналогового моделирования, чтобы затем переделать разводку. Перед тем как решиться на это, необходимо убедится в том, что проблема не связана с испытательным оборудованием или производственным дефектом платы. Необходимо также проверить все соединения, шифры компонент, значения компонент и т.д. Можно вместе с тем проверить амплитуду сигнала в различных точках трассировки, чтобы установить, где происходят потери.

Малый раскрыв глаз-диаграммы. Если амплитуда сигнала достаточна, но раскрыв глаза мал, то амплитуда одних бит будет высокой, а других – низкой. Это часто является результатом различия в коэффициенте усиления/ослабления трассы или передатчика на некоторых частотах. Как правило, проще всего проверить настройки предыскажения. Если есть эквалайзер или выровненный кабель на пути передачи сигнала, то необходимо проверить и обеспечить корректную установку значений.

Чрезмерный джиттер на приеме. Это наиболее общая проблема для неработающих соединений. Малый раскрыв глаза часто сопровождается проблемами с джиттером, так что все рекомендации для малого раскрыва глаза применимы и в этом случае. Если нет проблемы с предыскажением и джиттер не связан с целостностью внутреннего сигнала или установками эквалайзера, то необходимо начать поиск других источников джиттера, таких как:

•питание, вводы питания и шумы по питанию;

•перекрестные помехи;

•асимметрия времени нарастания и спада сигнала;

•несогласованные дифференциальные трассы;

•вандер или джиттер генератора.

Определение источника джиттера является непростой задачей. Необходимо задействовать лучшее измерительное оборудо-

124

вание, хорошие рекомендации и т.д. для систематического процесса экспериментирования и анализа – «разделяй и властвуй». Необходимо также, чтобы каждая особенность испытательного оборудования стала понятной. Некоторые DCA высокого класса имеют очень мощную диагностику джиттера, помогающую «смотреть в корень» проблемы.

Выявление причин начинается со сбора глаз-диаграмм из различных точек вдоль пути прохождения сигнала. Анализ этих данных должен показать участки и их источники джиттера. Например, если джиттер является приемлемым для передатчика и не является таковым после соединителя, то возможными источниками джиттера могут быть:

•перекрестные помехи от других сигналов платы между соединителем и передатчиком;

•перекрестная помеха от слоев питания платы;

•отражение из-за искажения импеданса соединителем или переходными отверстиями;

•перекрестные помехи от других сигналов соединителя. Выдвинуть предположение о причине джиттера просто,

проблемой является ее доказательство. Если это перекрестная помеха, то надо показать, как отключить ее источник.

Рис. 5.15. Пайка измерительных кабелей к печатной плате

Наблюдение сигналов. Немаловажным является и то, как сигналы с платы поступают в измерительные устройства, обычно имеющие коаксиальные соединители типа SNA. Поэтому необ-

125

ходимы переходные кабели либо промышленного производства, либо собственного изготовления. Подключение их к печатной плате – более трудоемкая задача. Так, если наблюдать соединение переменного тока, то необходимо будет удалить переходный конденсатор и припаять маленькие проводники. Может потребоваться и удаление компонент, и пайка на освободившиеся контактные площадки измерительных проводников (рис. 5.15).

5.3.2. Измерение S-параметров

S-параметры измеряют с помощью векторного анализатора цепей (VNA – vector network analyzer). На рис. 5.16 приведена схема базовой части VNA, где DUT – устройство, S-параметры которого измеряются.

Рис. 5.16. Схема измерения S-параметров VNA

Прецизионные соединители векторного анализатора с помощью прецизионных кабелей PC1 и PC2 подключаются к портам P1 и P2 DUT через подходящие адаптеры A1 и A2. Генератор несущей формирует сигнал требуемой частоты, мощность кото-

126

рого задается регулятором уровня. Позиция ключа SW1 определяет направление подачи сигнала на DUT. Пусть SW1 находится в положении 1, что означает измерение параметров S11 и S21. Тестовый сигнал через сплиттер 1 подается на эталонный вход

(RX REF1) и через направленный ответвитель DC1, кабель PC1

и адаптер А1 – на порт P1 DUT. Через третий порт DC1 отраженная от P1 мощность подается на тестовый вход 1 (RX TEST1). Аналогично сигнал, выходящий из порта P2, проходит через A2, PC2 и DC2 к RX TEST2. RX REF1, RX TEST1, RX REF2 и RXTEST2 известны как когерентные приемники с общим опорным генератором. Они способны измерять амплитуду и фазу тестового сигнала.

Рис. 5.17. Пример измерения S-параметров трасс блока

Выходные сигналы приемников вводятся в процессор для цифровой обработки и отображения. На рис. 5.17 приведен пример стенда для измерения S-параметров с помощью VNA Agilent N5249A, имеющего следующие основные технические характеристики:

•Диапазон частот: от 10 МГц до 8,5 ГГц.

•2 или 4 измерительных порта с двумя встроенными источниками.

127

•Динамический диапазон: 126 дБ на измерительных портах, 129 дБ при прямом доступе к приемнику, 32 001 точка трассы, 200 каналов, ширина полосы ПЧ от 1 Гц до 15 МГц.

•Высокая выходная мощность (+16 дБм), низкий уровень гармоник (–60 дБн) и широкий диапазон свипирования (качания) по мощности (41 дБ).

•Точка компрессии (точка, где отклонение амплитудной характеристики устройства от идеальной составляет 1 дБ) 0,1 дБ при входной мощности на измерительном порте +15 дБм.

•Низкий уровень собственных шумов: –111 дБм при ширине полосы ПЧ 10 Гц.

Вопросы для самоконтроля

1.В чем отличие цифрового осциллографа с памятью от цифрового стробоскопического осциллографа?

2.Какова роль эталонного кабеля DL1 при измерении отражения сигнала (см. рис. 5.4)?

3.Какие параметры глаз-диаграммы характеризуют способность приемника принять сигнал?

4.Какая часть глаз-диаграммы представляет джиттер?

5.Какова длительность измерения величины BER 10−12 для скорости передачи сигнала 2 Гбит/с?

6.О чем свидетельствует малый раскрыв глаз-диаграммы?

7.При каких условиях можно доверять зависимости

WaveCrest?

8.Какова роль векторного анализатора цепей при тестировании высокоскоростных соединений?

128

6. FPGA С ВЫСОКОСКОРОСТНЫМ ВВОДОМ-ВЫВОДОМ

6.1. ALTERA STRATIX V

Семейство FPGA Stratix V [9], выполненное по технологии 28-nm, содержит трансиверы для передачи сигналов на скорости 14.1 Гит/с через объединительную плату, между микросхемами платы, микросхемами платы и модулями (варианты GS и GX); на скорости 28 Гит/с между микросхемами платы, микросхемами платы и модулями (вариант GT). Семейство содержит более миллиона логических ячеек и до 4096 блоков DSP с переменной точностью. Stratix V поддерживает низковольтные дифференциальные сигналы (LVDS) для высокоскоростных коммуникаций, мини-LVDS и дифференциальные сигналы с уменьшенным пе-

репадом (RSDS – Reduced Swing Differential Signaling) для инди-

каторных панелей. На рис. 6.1 показана структура банка высокоскоростного ввода-вывода LVDS SERDES.

Рис. 6.1. Структура банка LVDS SERDES

Stratix V содержит следующие специализированные схемы для поддержки высокоскоростного ввода-вывода:

•Дифференциальный буфер ввода-вывода.

•Сериалайзер (передающая часть SERDES).

•Десериалайзер (приемная часть SERDES).

•Ресинхронизация данных (бит-проскальзывание).

•Динамическое выравнивание фазы (DPA – Dynamic Phase Alignment).

129

•Синхронизатор (FIFO буфер).

•Фракционную ФАПЧ (ФФАПЧ, Fractional PLL).

Приемник и передатчик SERDES также поддерживают дифференциальные варианты входов-выходов HSTL (интерфейсы синхросигнала), дифференциальные варианты HSUL и SSTL (интерфейсные сигналы синхронной динамической памяти).

Многие устройства семейства Stratix V и их свойства поддерживает САПР Quartus II версии 13.0. Оставшиеся устройства и свойства доступны в следующих версиях Quartus II. С помощью «Мастера настройки мега функций» Quartus II выполняет установку конфигурации узлов LVDS SERDES.

SERDES может быть сконфигурирован для поддержки таких коммуникационных протоколов с синхронизацией от источ-

ника, как параллельный RapidIO, XSBI (10-Gb Sixteen Bit Interface), SPI (Serial Peripheral Interface), SGMII (Serial Gigabit Media Independent Interface) и протокол со встроенной синхронизацией

GbE (Gigabit Ethernet).

RapidIO LP-LVDS – параллельный 8- или 16-разрядный дуплексный интерфейс точка-точка, частота тактового сигнала – 250, 375, 500, 750 или 1000 МГц. Интерфейс состоит из выходных дифференциальных шин TD[0:7], TD[8:15], входных дифференциальных шин RD[0:7], RD[8:15], дифференциальных выходных сигналов синхронизации TCLK0, TCLK1, TFRAME и дифференциальных выходных сигналов синхронизации RCLK0, RCLK1, RFRAME.

Шина XSBI состоит из двух однонаправленных дифферен-

циальных 16-битных шин TXD[0:15]P/N и RXD[0:15]P/N и двух линий синхросигналов TXCP/N и RXCP/N.

SGMII содержит две дифференциальные пары для передачи TX (данные), TXCLK (синхросигнал) и две дифференциальные пары для приема RX (данные), RXCLK (синхросигнал), работающих на частоте 625 МГц по технологии DDR.

6.1.1. Передатчик MGT Altera Stratix V

На рис. 6.2 приведена схема передатчика LVDS SERDES. Передатчик содержит истинный дифференциальный выходной буфер, сериалайзер и ФФАПЧ, которую можно разделять между передатчиком и приемником. Сериалайзер принимает парал-

130