.Проектирование устройств и систем с высокоскоростными соединениями

.pdf

Рис. 6.17. Передатчик GTX/GTH

Рассмотрим организацию MGT-трансиверов, предназначенных для высокоскоростной передачи. Каждый трансивер включает независимый передатчик (рис. 6.17), который состоит из бло-

ков PCS (Physical Coding Sublayer) и PMA (Physical Medium Attachment Sublayer). Параллельные данные из микроструктуры FPGA поступают на интерфейс передатчика и далее через PCS и PMA на выходной драйвер – уже как высокоскоростные после-

довательные данные. Элемент PMA PISO (Parallel Input Serial Output) является сериализатором.

6.3.1. Передатчик GTX/GTH Xilinx 7 series

Интерфейс между микроструктурой FPGA и передат-

чиком TX (FPGA TX Interface). Узлы проекта для микроструктуры FPGA передают данные через передатчик MGT, записывая значения в порт TXDATA по положительному перепаду сигнала TXUSRCLK2. Разрядность порта может быть сконфигурирована равной 2, 4 или 8 байт. Тактовая частота для параллельных данных (TXUSRCLK2) определяется скоростью передачи по линии, разрядностью порта TXDATA и тем, используется ли кодирование 8B/10B (если кодирование не используется, то разрядность может быть 20, 40 или 80 бит).

Кодирование 8B/10B (8B/10B Encoder). Многие протоколы используют это кодирование, являющееся промышленным стан-

151

дартом. Для передачи К-символов в интерфейсе передатчика предусмотрены линии TXCHARISK по одной на каждый байт поступающих на кодирование параллельных данных.

«Коробка скоростей» передатчика (TX Gearbox). Неко-

торые высокоскоростные протоколы используют 64B/66B кодирование для уменьшения накладных расходов кода 8B/10B. Механизм «Коробки скоростей» обеспечивает для кодов 64B/66B и 64B/67B поддержку объединения заголовка и нагрузки для 2, 4 и 8-байтного интерфейса. Скремблирование выполняется на уровне пользовательского проекта. Через входной порт TXHEADER[2:0] поступает заголовочная часть кода. [1:0] используется для заголовка кода 64B/66B, а [2:0] – для 64B/67B. Механизм «Коробки скоростей» поддерживает также режим интерфейса CAUI – 10-полосный 100 Гбит/с Ethernet для передачи данных между микросхемами.

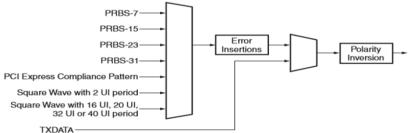

Генератор испытательных сигналов (Pattern Generator)

содержит псевдослучайный генератор (Pseudo-Random Bit Sequences – PRBS) для проведения проверки целостности высокоскоростных соединений. PRBS поддерживает промышленные стандарты PRBS-7, PRBS-15, PRBS-23, PRBS-31 (рис. 6.18).

Генератор испытательных сигналов также формирует последовательности прямоугольных импульсов с параметрами 16-UI, 20-UI, 32-UI и 40-UI и испытательные последовательности, совместимые с интерфейсом PCI Express.

Рис. 6.18. Схема-генератор испытательных сигналов GTX/GTH

Через входной порт TXPRBSSEL[2:0] задается вид испытательного сигнала. Значение 000 соответствует отключению

152

генератора. Входной порт TXPRBSFORCEERR предназначен для разрешения введения в испытательную последовательность ошибок.

Управление полярностью передатчика (Polarity). Если на печатной плате случайно перепутали полярность трасс дифференциальной пары для выводов TXP/TXN трансивера MGT, то для исправления ошибки предназначен узел Polarity, доступный пользовательским проектам через порт TXPOLARITY.

Устройство управления фазового интерполятора PPM пе-

редатчика (TX Phase Interpolator PPM Controller или TXPIPPM)

обеспечивает динамическое управление фазового интерполятора передатчика (TX PI), необходимого для приложений, требующих тонкой настройки управления данными в узле PMA (только для GTH). В наиболее общем случае фазовый интерполятор имеет два периодических входных сигнала φ и ψ обычно одного периода, от одного источника и единого узла управления. На вход узла управления (порт TXPI_PPM_CFG[7:0]) поступает значение взвешенного фактора интерполяции w (изменяется от 0 до W), задающее требование по фазовому смешиванию. Интерполированный выходной сигнал θ формируется в соответствии с выражением

θ = (w/W) · φ + (W – w/W) · ψ.

На рис. 6.19 приведена временная диаграмма фазового интерполятора. При w = 0 –> θ = ψ, а при w = W –> θ = φ.

Рис. 6.19. Временная диаграмма фазового интерполятора

Узел управления делителя тактовой частоты (рис 6.20)

состоит из двух основных компонентов: управление делителем для тактовой частоты последовательных данных и управление

153

делителем и выбором тактовой частоты параллельных данных. На делитель поступают такие тактовые сигналы, как:

•QPLLREFCLK – опорный тактовый сигнал общей ФАПЧ MGT-четверки, выполненной базе LC-контура;

•QPLLCLK – тактовый сигнал общей ФАПЧ MGT-чет-

верки;

• MGT REFCLK0, REFCLK1 – дифференциальные порты FPGA для подачи внешних опорных тактовых частот.

Рис. 6.20. Последовательный и параллельный делители тактовой частоты передатчика

Конфигурируемый драйвер передатчика (TX Driver) реали-

зован по технологии CML (рис. 6.21). Для максимизации целостности сигнала он содержит следующие функции:

•управление напряжением;

•предкурсор и посткурсор при предыскажении;

•калиброванные терминальные резисторы.

154

Рис. 6.21. Схема конфигурируемого драйвера передатчика

Через порт TXDIFFCTRL[3:0] задается уровень выходного сигнала драйвера, а через порты TXPRECURSOR[4:0] и TXPOSTCURSOR[4:0] задаются номера предопределенных значений искажений для предкурсора и посткурсора механизма предыскажения. Курсор, предкурсор, посткурсор – термины, используемые в описании сигнала с предыскажением (рис. 6.22). Искажение определяется в децибелах как |20log10 (Vlow/Vhigh)|.

Рис. 6.22. Терминология предыскажения

Внеполосная сигнализация (Out Of Band Signaling – OOB).

Протоколы SATA и SAS поддерживают эту схему сигнализации, которая используется при взаимодействии между хостом и дисководом для идентификации его типа и объема. Сигнал OOB является трехуровневым и формируется из двух символов – idle (холостой) и burst (пакет), как показано на рис. 6.23.

155

Рис. 6.23. Символы OOB

В SATA определено два разных OOB-сигнала – COMRESET/COMINIT и COMWAKE, а в SAS – еще и COMSAS. Пере-

дача этих сигналов инициируется через порты TXCOMINIT, TXCOMWAKE и TXCOMSAS передатчика MGT. Полная OOB-

последовательность содержит несколько периодов burst/idle с последующей паузой (последовательность из символов idle). Длительность символа idle используется для идентификации типа и скорости сигнала OOB. На рис. 6.24 приведен пример сигнала

COMRESET. Через порт SATA_BURST_SEQ_LEN[3:0] устанав-

ливается количество символов burst в в сигнале OOB.

Рис. 6.24. Пример OOB сигнала COMRESET

6.3.2 Приемник GTX/GTH Xilinx 7 series

Каждый трансивер включает независимый приемник (рис. 6.25), который, как и передатчик, состоит из блоков PCS

и PMA.

Высокоскоростной поток данных по печатным проводникам платы поступает на Аналоговую схему ввода (RX AFE – Analog Front End) узла PMA приемника MGT (рис. 6.26), имеющую:

•конфигурируемый источник напряжения для терминальных резисторов MGTVTT;

•калиброванные терминальные резисторы 50 Ом.

156

Рис. 6.25. Приемник GTX/GTH

Рис. 6.26. Входная аналоговая схема приемника

Источник терминального напряжения задается через интерфейс RX_CM_SEL[1:0], обеспечивающий подключение предопределенного значения AVTT, земли GND, плавающего потенциала Floating (в этом случае выполняется прием по постоянному току, т.е. отсутствуют внешние разделительные конденсаторы) или программируемого источника Programmable. Величина напряжения Programmable задается через интерфейс

RX_CM_TRIM[3:0] и лежит в диапазоне от 100 до 1100 мВ.

Значения сигналов на контактах RX AFE через буферы ACJTAG RX вводятся в подсистему граничного сканирования по

157

стандарту JTAG. Входные диоды защищают входную схему от перенапряжения.

Внеполосная сигнализация на приеме. Приемник поддер-

живает декодирование OOB-последовательностей, описанных в спецификациях для интерфейсов SATA, SAS, и аварийную сигнализацию для спецификации PCI Express. Поддержка SATA/SAS OOB выполняется аналоговой схемой и автоматом для декодирования символов burst.

Входной эквалайзер (выравниватель частотной характеристики). Среда передачи сигнала имеет ограниченную полосу пропускания, поэтому он подвержен ослаблению и искажению. Приемник поддерживает два типа адаптивной фильтрации, связанной с компромиссом на системном уровне между мощностью и производительностью.

Для оптимизации по мощности с малым рассеянием приемник может работать в адаптивном режиме LPM (Low-Power Mode) энергосбережения (рис. 6.27). Сигнал поступает на ограничитель с автоматической регулировкой усиления (Limiter AGC), затем на линейный эквалайзер (Linear EQ), Через атрибу-

ты RXLPM_LF_CFG[7:1] и RXLPM_HF_CFG[7:1] задаются низ-

кочастотная и высокочастотная части характеристики эквалайзера. Скорректированный сигнал поступает на адаптивный LPMконтроллер, оценивающий раскрыв его глаз-диаграммы.

Рис. 6.27. Режим энергосбережения LPM

Для коррекции затухания сигнала приемник может работать в режиме DFE (Decision Feedback Equalization – коррекции с ре-

шающей обратной связью) – рис. 6.28. Это позволяет улучшить

158

компенсацию потерь в канале передачи с помощью точной подстройки параметров цифрового адаптивного фильтра высокой частоты по сравнению с просто линейным эквалайзером.

Рис. 6.28. Режим DFE

DFE не может удалить предкурсор передаваемого бита, а только выполняет компенсацию посткурсора. Значения коэффициентов вычисляются по адаптивному алгоритму, реализуемому в MMSE-контроллере. Через атрибуты RX_DFE_UT_ CFG[10:4], RX_DFE_H2_CFG[6:1], RX_DFE_H3_CFG[6:1], RX_DFE_H4_CFG[5:1], RX_DFE_H5_CFG[5:1] задаются значе-

ния по умолчанию.

Режим LPM рекомендуется для приложений со скоростью передачи до 11,2 Гбит/с и коротких расстояний с затуханием не больше 12 дБ на частоте Найквиста. Режим DFE рекомендуется для средних и больших расстояний с затуханием 8 дБ и больше. DFE имеет преимущество в выравнивании канала, так как не усиливает шумы и наводки. DFE может также корректировать отражения, вызванные сосредоточенными неоднородностями внутри первых пяти посткурсоров. DFE является лучшим выбором в случае, когда наводки или отражения идентифицируются при анализе отклика единичного бита.

Выделитель тактовой частоты и данных (CDR). На рис. 6.29 приведена структурная схема CDR с ротацией фазы. Входные данные сначала проходят стадию коррекции (Linear EQ), а затем захватываются узлами стробирования фронта (Edge Sampler) и данных (Data Sampler). Захваченные Data Sampler данные

159

поступают в управляющий автомат CDR и в узлы-потребители. Управляющий автомат CDR использует результаты стробирования данных и фронтов с целью определения фазы входных данных для последующего управления фазовыми интерполяторами PI(D) и PI(X). Фаза для Edge Sampler блокируется при установлении фазы Data Sampler посередине раскрыва глаза данных, как на рис. 6.30, где E и D – позиции стробирования фронтов и данных.

Рис. 6.29. Структурная схема CDR

Рис. 6.30. Позиции стробирования CDR

PLL (CPLL или QPLL) обеспечивает базовое тактирование PI. В свою очередь, PI дает чистые, равноотстоящие стробы, позволяющие автомату управления CDR давать чистые управляющие воздействия для установки фазы. Автомат управления CDR может следить за входными данными, частота которых может отличаться от локальной тактовой частоты PLL.

На рис. 6.31 приведена схема управления делителя тактовой частоты на приеме, состоящая из узла управления делителем тактовой частоты для последовательных данных (/D{1, 2, 4, 8, 16}), узла управления делителем тактовой частоты (RXOUTCLK) для параллельных данных и узла управления выбором частоты.

160