Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №3 по дисциплине «Электроника и схемотехника»

Вариант №2

Выполнил: Студент гр.

Принял

Томск 2022

Введение

Целью данной работы является получение навыков создания мультиплексоров и демультиплексоров на разных базисах, а также реализации функции на мультиплексоре и демультиплексоре.

Поставленные задачи:

−Собрать на холсте схемы мультиплексора 8-1 (на базисе И, ИЛИ,

НЕ), на его основе мультиплексора 16-2, демультиплексора 1-4 (на базисе И-

НЕ), на его основе демультиплексора 1-8, а также описать элементы на HDL и

промоделировать работы схем.

− Собрать на холсте схему для выражения = ∩ ∩ на основе мультиплексора и дешифратора, промоделировать работы схем.

2

1МУЛЬТИПЛЕСОР 8-1

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности устройства MUX 8-1.

Таблица 1.1 – Таблица истинности MUX 8-1

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

a2 |

a1 |

a0 |

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

b0 |

0 |

0 |

0 |

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

b1 |

x |

0 |

0 |

1 |

b1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

b2 |

x |

x |

0 |

1 |

0 |

b2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

b3 |

x |

x |

x |

0 |

1 |

1 |

b3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

b4 |

x |

x |

x |

x |

1 |

0 |

0 |

b4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

b5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

b5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

b6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

b6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

b7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.2 |

Формула |

|

|

|

|

|

|

|

̅̅̅̅ |

̅̅̅̅ |

̅̅̅̅ |

|

Формула для выхода F будет иметь вид: = ∩ ( 0 ∩ 2 ∩ 1 |

∩ 0 |

|||||

̅̅̅̅ ̅̅̅̅ |

̅̅̅̅ |

̅̅̅̅ |

̅̅̅̅ |

|

̅̅̅̅ |

|

1 ∩ 2 ∩ 1 ∩ 0 2 ∩ 2 ∩ 1 ∩ 0 3 ∩ 2 ∩ 1 ∩ 0 4 ∩ 2 ∩ 1 ∩ |

||||||

̅̅̅̅ |

̅̅̅̅ |

|

̅̅̅̅ |

|

|

|

0 5 ∩ 2 ∩ 1 ∩ 0 6 ∩ 2 ∩ 1 ∩ 0 7 ∩ 2 ∩ 1 ∩ 0). |

|

|

|

|||

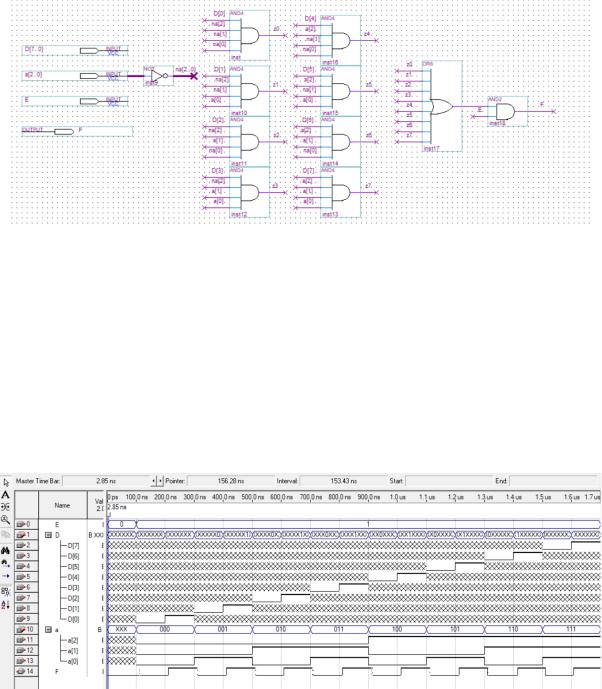

1.3Функциональная схема

На рисунке 1.1 представлена функциональная схема устройства MUX 8-1.

3

Рисунок 1.1 – Функциональная схема MUX 8-1

Схема выполнена на базисе НЕ, ИЛИ, И.

1.4Моделирование

На рисунках 1.2 и 1.3 представлено моделирование в двух режимах.

Рисунок 1.2 – Моделирование MUX 8-1 (Timing)

4

Рисунок 1.3 – Моделирование MUX 8-1 (Functional)

Результаты моделирования совпадают с таблицей истинности.

1.5Код на HDL

На рисунке 1.4 представлено описание устройства на SystemVerilog HDL.

Рисунок 1.4 – MUX 8-1 на SystemVerilog HDL

1.6Схема из RTL viewer для кода HDL

На рисунке 1.5 представлена схема для устройства MUX 8-1 из RTL viewer.

5

Рисунок 1.5 – Схема устройства из RTL viewer

1.7Моделирование устройства, описанного кодом HDL

На рисунке 1.6 представлено моделирование устройства, описанного на

HDL, в режиме Timing.

Рисунок 1.6 – Моделирование MUX 8-1, описанного на SystemVerilog HDL (Timing)

Результаты моделирования совпадают с таблицей истинности.

1.8Таблица истинности масштабируемого устройства

Втаблице 1.2 представлена таблица истинности масштабируемого устройства MUX 16-2.

6

Таблица 1.2 – Таблица истинности MUX 16-2

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

Выходы |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 |

E0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

a2 |

a1 |

a0 |

F1 |

F0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

x |

x |

x |

x |

x |

b0 |

x |

x |

x |

x |

x |

x |

x |

a0 |

0 |

0 |

0 |

0 |

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

x |

x |

x |

x |

b1 |

x |

x |

x |

x |

x |

x |

x |

a1 |

x |

0 |

0 |

1 |

0 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

x |

x |

x |

b2 |

x |

x |

x |

x |

x |

x |

x |

a2 |

x |

x |

0 |

1 |

0 |

0 |

a2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

x |

x |

b3 |

x |

x |

x |

x |

x |

x |

x |

a3 |

x |

x |

x |

0 |

1 |

1 |

0 |

a3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

x |

b4 |

x |

x |

x |

x |

x |

x |

x |

a4 |

x |

x |

x |

x |

1 |

0 |

0 |

0 |

a4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

x |

b5 |

x |

x |

x |

x |

x |

x |

x |

a5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

0 |

a5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x |

b6 |

x |

x |

x |

x |

x |

x |

x |

a6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

0 |

a6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

b7 |

x |

x |

x |

x |

x |

x |

x |

a7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

0 |

a7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

d0 |

x |

x |

x |

x |

x |

x |

x |

c0 |

0 |

0 |

0 |

d0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

x |

x |

x |

x |

d1 |

x |

x |

x |

x |

x |

x |

x |

c1 |

x |

0 |

0 |

1 |

d1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

x |

x |

x |

d2 |

x |

x |

x |

x |

x |

x |

x |

c2 |

x |

x |

0 |

1 |

0 |

d2 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

x |

x |

d3 |

x |

x |

x |

x |

x |

x |

x |

c3 |

x |

x |

x |

0 |

1 |

1 |

d3 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

x |

d4 |

x |

x |

x |

x |

x |

x |

x |

c4 |

x |

x |

x |

x |

1 |

0 |

0 |

d4 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

x |

d5 |

x |

x |

x |

x |

x |

x |

x |

c5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

d5 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

x |

d6 |

x |

x |

x |

x |

x |

x |

x |

c6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

d6 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

d7 |

x |

x |

x |

x |

x |

x |

x |

c7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

d7 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

x |

x |

x |

x |

f0 |

x |

x |

x |

x |

x |

x |

x |

e0 |

0 |

0 |

0 |

f0 |

e0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

x |

x |

x |

f1 |

x |

x |

x |

x |

x |

x |

x |

e1 |

x |

0 |

0 |

1 |

f1 |

e1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

x |

x |

f2 |

x |

x |

x |

x |

x |

x |

x |

e2 |

x |

x |

0 |

1 |

0 |

f2 |

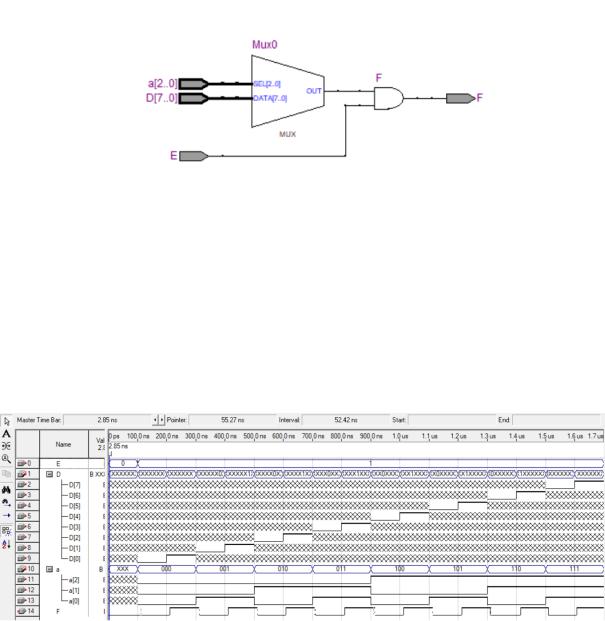

e2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

x |

f3 |

x |

x |

x |

x |

x |

x |

x |

e3 |

x |

x |

x |

0 |

1 |

1 |

f3 |

e3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

f4 |

x |

x |

x |

x |

x |

x |

x |

e4 |

x |

x |

x |

x |

1 |

0 |

0 |

f4 |

e4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

f5 |

x |

x |

x |

x |

x |

x |

x |

e5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

f5 |

e5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

f6 |

x |

x |

x |

x |

x |

x |

x |

e6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

f6 |

e6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

f7 |

x |

x |

x |

x |

x |

x |

x |

e7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

f7 |

e7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

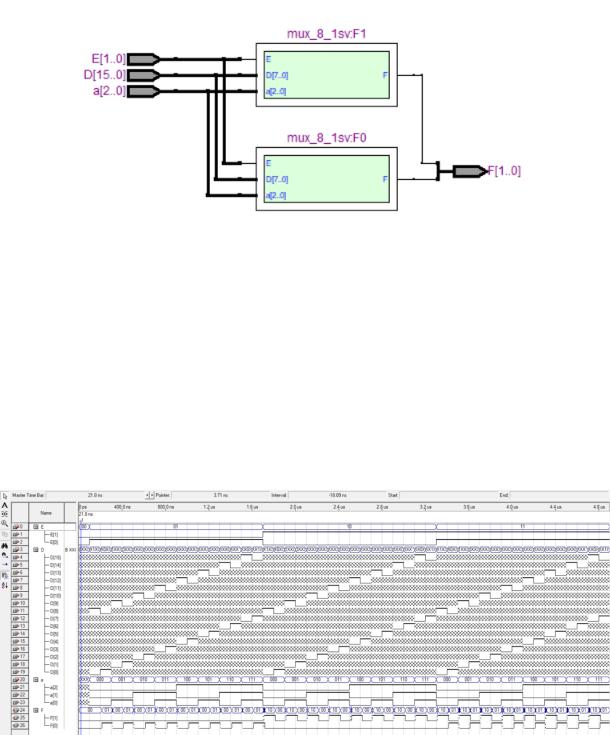

1.9Функциональная схема масштабируемого устройства

На рисунке 1.7 представлена схема устройства MUX 16-2, построенного

на основе MUX 8-1.

7

Рисунок 1.7 – Функциональная схема MUX 16-2

1.10 Моделирование масштабируемого устройства

На рисунках 1.8 и 1.9 представлено моделирование MUX 16-2 в двух

режимах.

Рисунок 1.8 – Моделирование MUX 16-2 (Timing)

8

Рисунок 1.9 – Моделирование MUX 16-2 (Functional)

Результаты моделирования совпадают с таблицей истинности.

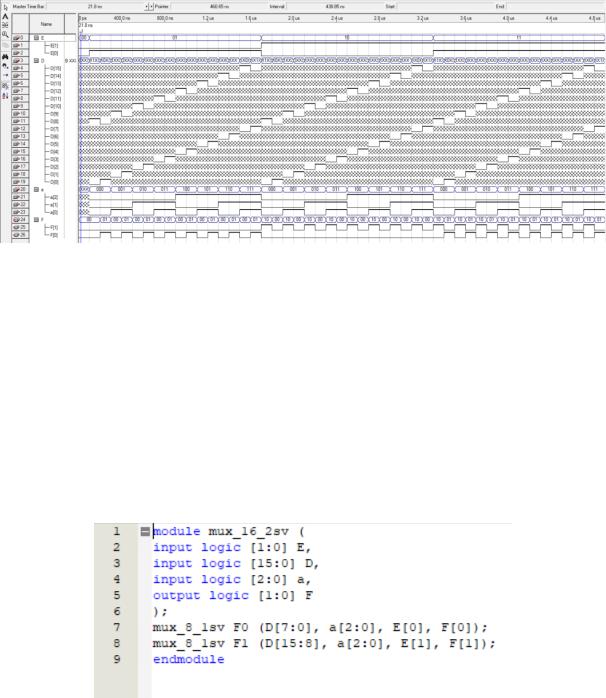

1.11 Код на HDL масштабируемого устройства

На рисунке 1.10 представлено описание устройства на SystemVerilog

HDL.

Рисунок 1.10 – MUX 16-2 на SystemVerilog HDL

1.12 Схема из RTL viewer для кода HDL масштабируемого устройства

На рисунке 1.11 представлена схема для устройства MUX 16-2 из RTL

viewer.

9

Рисунок 1.11 – Схема устройства из RTL viewer

1.13 Моделирование масштабируемого устройства, описанного кодом

HDL

На рисунке 1.12 представлено моделирование устройства, описанного на

HDL, в режиме Timing.

Рисунок 1.12 – Моделирование MUX 16-2, описанного на SystemVerilog HDL (Timing)

Результаты моделирования совпадают с таблицей истинности.

10