Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4

по дисциплине «Электроника и схемотехника» Вариант №2

Студент гр.

Руководитель

Томск 2022

Введение

Целью данной работы является изучение основных типов триггеров, их принципы построения и работы.

Поставленные задачи:

Собрать на холсте схемы динамического RS триггера (на базисе ИЛИ-НЕ),

одноступенчатого T триггера (на базисе И-НЕ), двухступенчатого D триггера (на базисе ИЛИ-НЕ), а также описать элементы на VHDL и промоделировать работы схем.

2

1ДИНАМИЧЕСКИЙ RS ТРИГГЕР

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности динамического RS

триггера.

Таблица 1.1 – Таблица истинности динамического RS триггера

R |

S |

C |

Q(t) |

Q(t+1) |

Режим |

|

|

|

|

|

|

|

|

X |

X |

0 |

0/1 |

0/1 |

Хранение |

|

|

|

|

|

|

|

|

0 |

1 |

0→1 |

X |

1 |

Установка в |

|

1 |

||||||

|

|

|

|

|

||

|

|

|

|

|

|

|

1 |

0 |

0→1 |

X |

0 |

Установка в |

|

0 |

||||||

|

|

|

|

|

||

|

|

|

|

|

|

|

1 |

1 |

0→1 |

X |

X |

Запрещенный |

|

|

|

|

|

|

|

1.2Функциональная схема

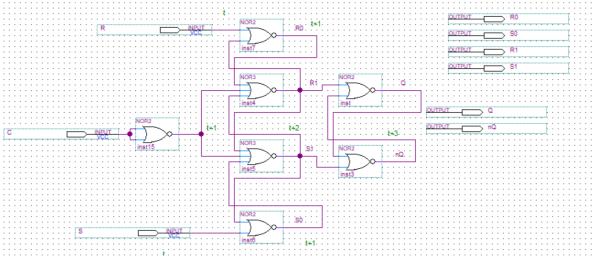

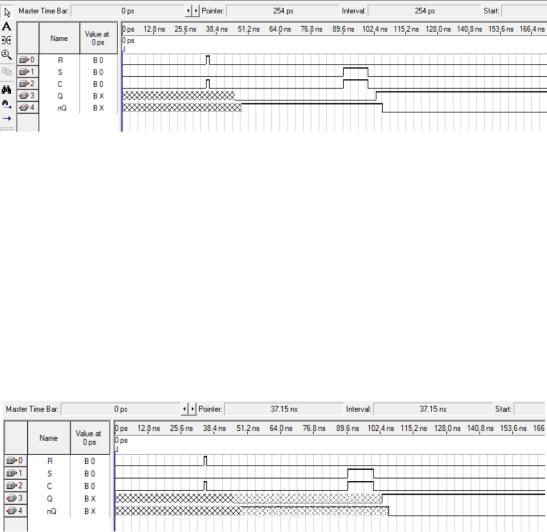

На рисунке 1.1 представлена функциональная схема динамического RS

триггера.

Рисунок 1.1 – Динамический RS триггер

3

Схема выполнена на базисе ИЛИ-НЕ.

1.3Формула

Формула для важных точек, обозначенных на функциональной схеме,

выглядят следующим образом:

0( + 1) = ( ) 1( )0( + 1) = ( ) 1( )

1( + 2) = 0( + 1) ( + 1) 1( + 1)1( + 2) = 0( + 1) ( + 1) 1( + 1)

( + 3) = 1( + 2) ( + 2)( + 3) = 1( + 2) ( + 2)

1.4Моделирование

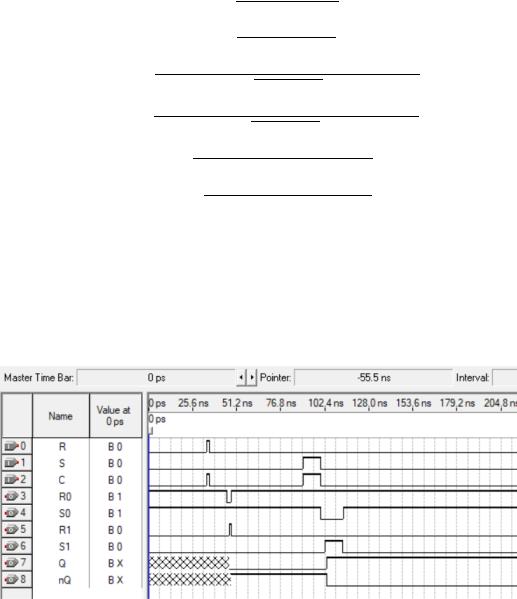

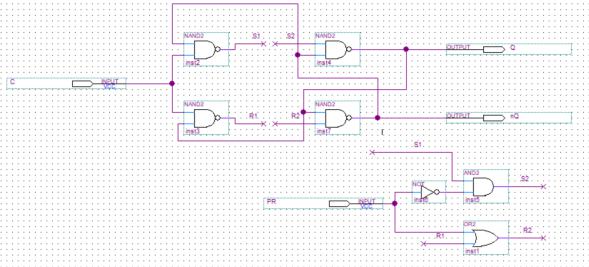

На рисунках 1.2 и 1.3 представлено моделирование в двух режимах.

Рисунок 1.2 – Моделирование динамического RS триггера (Timing)

4

Рисунок 1.3 – Моделирование RS триггера (Functional)

Результаты моделирования совпадают с таблицей истинности.

Минимальная продолжительность управляющего сигнала 1,3 нс.

На рисунке 1.4 представлено моделирование с длительностью входного сигнала 1,2 нс.

Рисунок 1.4 – Моделирование, длительность входного сигнала 1,2 нс

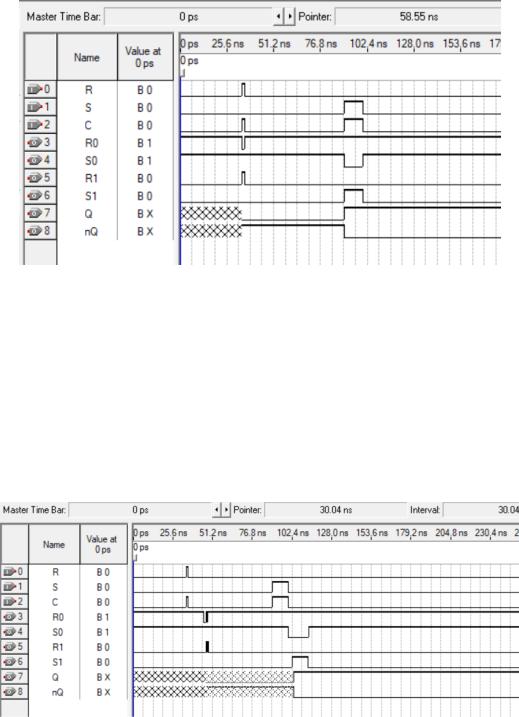

1.5Код на VHDL

На рисунке 1.5 представлено описание устройства на VHDL.

5

Рисунок 1.5 – RS триггера на VHDL

1.6Схема из RTL viewer для кода VHDL

На рисунке 1.6 представлена схема для устройства RS триггера из RTL viewer.

Рисунок 1.6 – Схема устройства из RTL viewer

1.7Моделирование устройства, описанного кодом VHDL

На рисунке 1.7 представлено моделирование устройства, описанного на

VHDL, в режиме Timing.

6

Рисунок 1.7 – Моделирование динамического RS триггера, описанного на

VHDL (Timing)

Результаты моделирования совпадают с таблицей истинности.

Минимальная продолжительность управляющего сигнала 1,1 нс.

На рисунке 1.8 представлено моделирование с длительностью входного сигнала 1 нс.

Рисунок 1.8 – Моделирование, длительность входного сигнала 1 нс

7

2 T ТРИГГЕР НА ОСНОВЕ D ТРИГГЕРА

2.1Одноступенчатый Т триггер

При попытке реализации одноступенчатого Т триггера возникли сложности, связанные с тем, что внутренние связи между элементами и их расположение определил САПР.

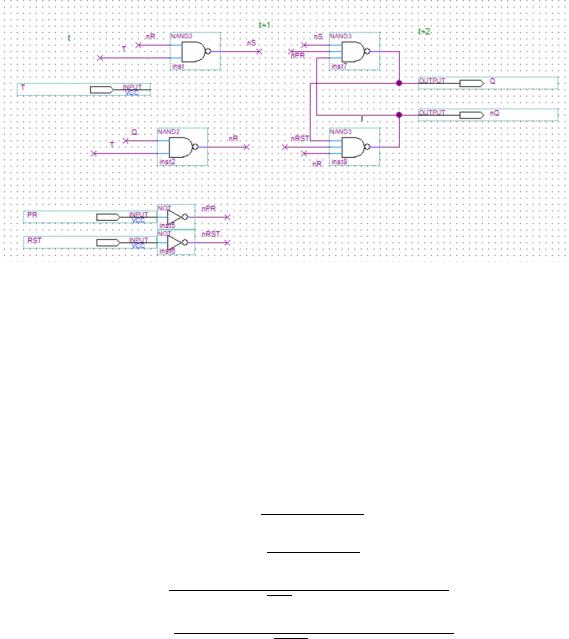

На рисунке 2.1 представлена функциональная схема Т триггера.

Рисунок 2.1 – Функциональная схема одноступенчатого Т триггера

2.2Таблица истинности

Втаблице 2.1 представлена таблица истинности T триггера на основе D

триггера.

Таблица 2.1 – Таблица истинности T триггера на основе D триггера

T |

Q(t) |

Q(t+1) |

Режим |

|

|

|

|

0 |

0/1 |

0/1 |

хранение |

|

|

|

|

1 |

0 |

1 |

счетный в 1 |

|

|

|

|

1 |

1 |

0 |

счетный в 0 |

|

|

|

|

8

2.3Функциональная схема

На рисунке 2.2 представлена функциональная схема T триггера на основе

D триггера.

Рисунок 2.2 – Функциональная схема T триггера на основе D триггера

Схема выполнена на базисе И-НЕ.

2.4Формула

Формула для важных точек, обозначенных на функциональной схеме,

выглядят следующим образом:

( + 1) = ( ) ∩ ( ) ( + 1) = ( ) ∩ ( )

( + 2) = ( + 1) ∩ ( + 1) ∩ ( + 1) ( + 2) = ( + 1) ∩ ( + 1) ∩ ( + 1)

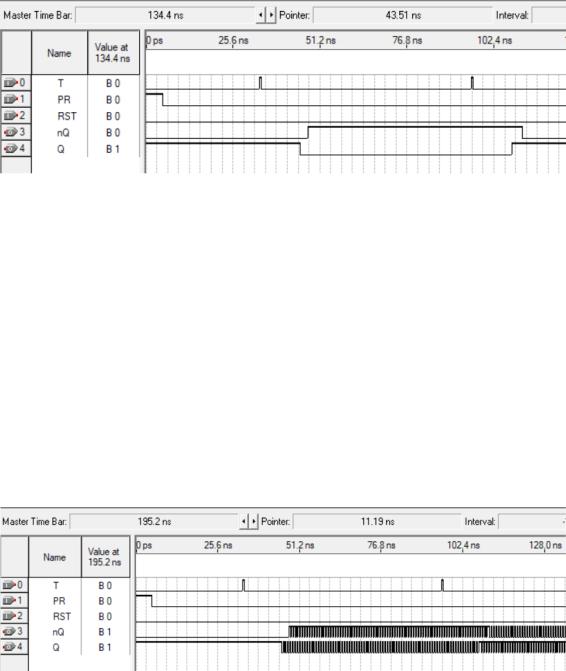

2.5Моделирование

На рисунке 2.3 представлено моделирование в режиме Timing. 9

Рисунок 2.3 – Моделирование T триггера на основе D триггера (Timing)

Так как данная реализация Т триггера на основе D триггера основана с учетом задержек, а режим Functional не учитывает их, то моделирование в данном режиме невозможно.

Результаты моделирования совпадают с таблицей истинности.

Минимальная длительность входного сигнала 0,6 нс.

На рисунке 2.4 представлено моделирование с длительностью входного сигнала 0,5 нс.

Рисунок 2.4 – Моделирование, длительность входного сигнала 0,5 нс

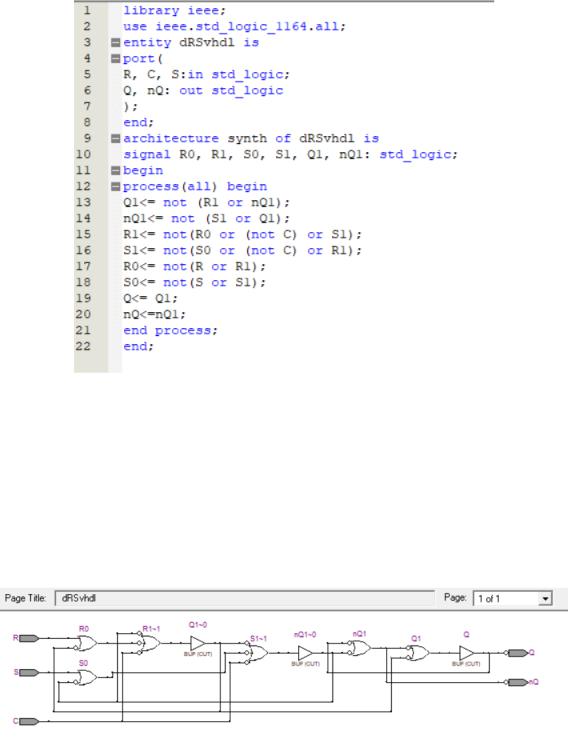

2.6Код на VHDL

На рисунке 2.5 представлено описание устройства на VHDL.

10