Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ РЕГИСТРОВ И СЧЕТЧИКОВ

Отчет по лабораторной работе №7

по дисциплине «Электроника и схемотехника» Вариант №2

Студент гр.

Руководитель

Томск 2022

Введение

Целью данной работы является получение навыков совместного применения регистров и счетчиков.

Поставленные задачи:

Собрать схему конечного автомата с приемом данных по заднему фронту сигнала внешней синхронизации параллельным кодом с асинхронным сбросом. Произвести вычисления функций из лабораторной работы №1 для вариантов: 1,

2, 3, 24 (формулы представлены в пункте 1.1). После получения логического нуля по линии «read» произвести выдачу полученных результатов последовательным кодом младшими разрядами вперед. Синхронизация передаваемых разрядов будет осуществляться передним фронтом выходного синхросигнала, который передается вместе с данными. Также необходимо собрать схемы для обеспечения «чистого» выхода у синхронного (вычитающий, М = 17) и асинхронного (суммирующий, М = 22) счетчиков из лабораторной работы №5. Описать перечисленные устройства на SystemVerilog

и промоделировать оба варианта.

2

1 ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ

1.1Таблица истинности и формулы

Функции, расчет которых выполняет конечный автомат имеют вид:

24 = ˄ ˄ ˄ ;3 = ( ˄ )˅ ( ˄ );2 = ( ˄ )˅ ( ˄ );1 = ˄ ˄ ˄ .

В таблице 1.1 представлена таблица истинности для вычислителя функций.

Таблица 1.1 – Таблица истинности

|

Входы |

|

|

Выходы |

|

||

Ст. разряд |

|

|

Мл. разряд |

Ст. разряд |

|

|

Мл. разряд |

x |

y |

z |

w |

F24 |

F3 |

F2 |

F1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1.2Функциональная схема

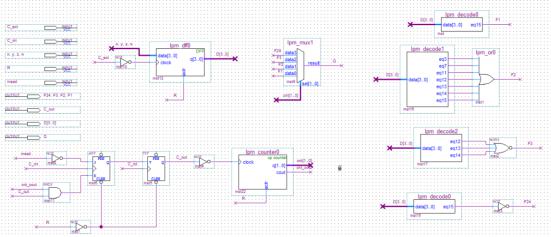

На рисунке 1.1 представлена функциональная схема вычислителя

функций с параллельной записью данных по заднему фронту, с асинхронным

3

сбросом и последовательной выдачей данный младшими разрядами вперед по переднему фронту, с активным уровнем сигнала nread 0.

Рисунок 1.1 – Функциональная схема

На вход в регистр lpm_dff0 мы подаем сигналы x, y, z, w и синхросигнал

C_ext, который подается через инвертор, для записи входных значений.

Полученные сигналы отправляются на дешифраторы для вычисления результатов функций. Результирующие сигналы имеют вид F24, F3, F2, F1. Эти сигналы подаются на мультиплексор, куда на адресный вход подаются сигналы cnt[1..0]. Сигналы cnt[1..0] выходят из счетчика lpm_counter0, куда на вход поступает инверсный сигнал C_out. Данный сигнал выходит из Т триггера,

который тактируется внутренним сигналом синхронизации. На вход Т триггера поступает сигнал из JK триггера, тактируемый тем же сигналом. На вход J

подается инверсия сигнала nread, а на сигнал K подается сигнал, получаемый в результате конъюнкции сигналов cnt_out и C_out. Оба счетчика имеют асинхронный сброс.

1.3Моделирование

На рисунке 1.2 представлен результат моделирования в режиме «Timing».

4

Рисунок 1.2 – Моделирование конечного автомата (Timing)

При подаче комбинации «0000» на входы x, y, z, w и такта C_ext (50-100

нс, 100 нс – активный фронт), далее на nread приходит активный уровень (300-

362,5 нс). Активные фронты выходной синхронизации: 383,098 нс, 483,098 нс, 583,098 нс, 683,098 нс (сигнал Q в логической единице 540,199-740,199 нс).

Результат на выходе «0011» - младшими разрядами вперед.

При подаче комбинации «1111» на входы x, y, z, w (937,5-962,5 нс) и

такта C_ext (900-950 нс, 950 нс – активный фронт), далее на nread приходит активный уровень (1600-1700 нс). Активные фронты выходной синхронизации: 1683,098 нс, 1783,098 нс, 1883,098 нс, 1983,098 нс (сигнал Q в логическом нуле

1940,48-2040,48 нс). Результат на выходе «1110» - младшими разрядами вперед.

При подаче комбинации «1011» на входы x, y, z, w (2438-2463 нс) и такта

C_ext (2400-2450 нс, 2450 нс - активный фронт), далее на nread подается активный уровень (2762,5-2812,5). Активные фронты выходной синхронизации: 2833,098 нс, 2933,098 нс, 3033,098 нс, 3133,098 нс (сигнал Q в логической единице 2890,48-3190,199 нс). Результат на выходе «1110» - младшими разрядами вперед.

На рисунке 1.3 представлен результат моделирования в режиме

«Functional».

5

Рисунок 1.3 – Моделирование конечного автомата (Functional)

Результаты моделирования совпадают с таблицей истинности.

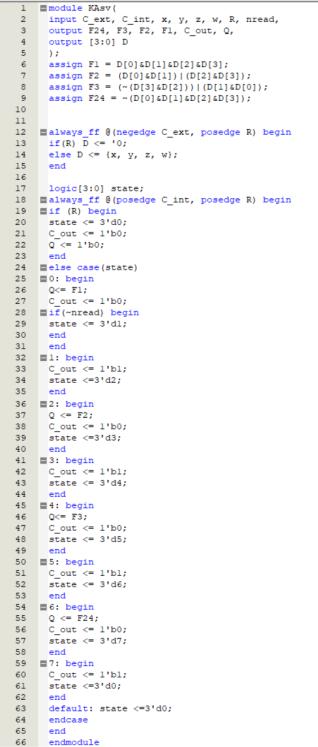

1.4Код на SystemVerilog

На рисунке 1.4 представлено описание конечного автомата на

SystemVerilog.

6

Рисунок 1.4 – Код на SystemVerilog

С 12 по 15 строку описывается триггер, записывающий входные данные x, y, z, w и обеспечивающий сброс при подаче сигнала R. С 6 по 9 строку описывается получение результатов функций. С 17 по 65 строку описывается восемь состояний конечного автомата при помощи модуля case, где мы имеем

разные выходные данные и переход к следующему состоянию, например, в

7

нулевом состоянии сигнал выходной Q принимает сигнал F1 (вывод младшими разрядами вперед), сигнал C_out уходит в логический 0, и происходит проверка на сигнал ~nread, в результате которой автомат может перейти в следующее состояние. До модуля case описывается асинхронный сброс сигналом R.

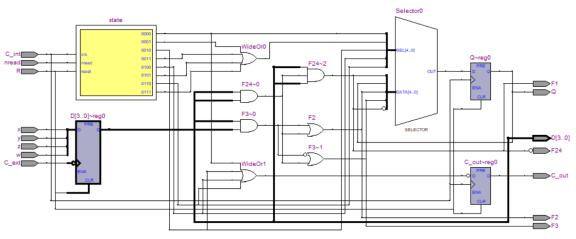

1.5Схема из RTL viewer для кода SystemVerilog

На рисунке 1.5 представлена схема из RTL viewer для кода SystemVerilog.

Рисунок 1.5 - Схема из RTL viewer для кода SystemVerilog

Сам автомат является блоком state, который имеет 8 состояний. Ниже него регистр, записывающий значения входных данных. Регистр C_out~reg0

генерирует сигнал синхронизации передаваемых данных C_out, а регистр

Q~reg0 обеспечивает передачу результатов последовательным кодом. Останые блоки в данной схеме представляют собой комбинационную схему генерации выходных данных.

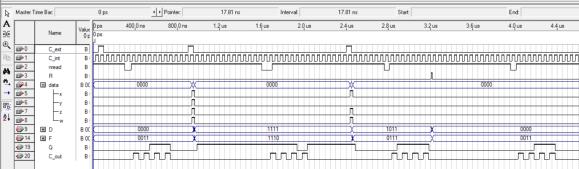

1.6Моделирование устройства, описанного кодом SystemVerilog

На рисунке 1.6 представлено моделирование конечного автомата,

описанного на SystemVerilog.

8

Рисунок 1.6 – Моделирование конечного автомата, описанного кодом

SystemVerilog

Моделирование соответствует таблице истинности.

9

2АСИНХРОННЫЙ СЧЕТЧИК С ВЫХОДНЫМ БУФЕРОМ

2.1Таблица функционирования

Втаблице 2.1 представлена таблица функционирования для асинхронного суммирующего счетчика с модулем счета 22.

Таблица 2.1 – Таблица функционирования

№ сигнала |

|

|

Выходы |

|

|

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

||

|

||||||

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

1 |

1 |

|

4 |

0 |

0 |

1 |

0 |

0 |

|

5 |

0 |

0 |

1 |

0 |

1 |

|

6 |

0 |

0 |

1 |

1 |

0 |

|

7 |

0 |

0 |

1 |

1 |

1 |

|

8 |

0 |

1 |

0 |

0 |

0 |

|

9 |

0 |

1 |

0 |

0 |

1 |

|

10 |

0 |

1 |

0 |

1 |

0 |

|

11 |

0 |

1 |

0 |

1 |

1 |

|

12 |

0 |

1 |

1 |

0 |

0 |

|

13 |

0 |

1 |

1 |

0 |

1 |

|

14 |

0 |

1 |

1 |

1 |

0 |

|

15 |

0 |

1 |

1 |

1 |

1 |

|

16 |

1 |

0 |

0 |

0 |

0 |

|

17 |

1 |

0 |

0 |

0 |

1 |

|

18 |

1 |

0 |

0 |

1 |

0 |

|

19 |

1 |

0 |

0 |

1 |

1 |

|

20 |

1 |

0 |

1 |

0 |

0 |

|

21 |

1 |

0 |

1 |

0 |

1 |

|

22 |

0 |

0 |

0 |

0 |

0 |

2.2Функциональная схема

На рисунке 2.1 представлена функциональная схема асинхронного суммирующего счетчика с модулем счета 22.

10