Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №6

по дисциплине «Электроника и схемотехника» Вариант №2

Студент гр.

Руководитель

Томск 2022

Введение

Целью данной работы является изучение регистров, их принципов построения и работы.

Поставленные задачи:

Собрать, используя D триггеры, на холсте схемы регистра типа SISO со сдвигом влево, синхронной параллельной загрузкой данных, асинхронным сбросом и разрядностью в 10 бит, регистра типа SIPO со сдвигом вправо,

асинхронным сбросом и разрядностью в 12 бит, регистра типа PIPO с

асинхронной загрузкой данных, синхронным сбросом и разрядностью в 14 бит,

а также описать их на VHDL и промоделировать работы схем.

2

1РЕГИСТР ТИПА SISO

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности регистра SISO.

Таблица 1.1 – Таблица истинности регистра SISO

№ |

|

|

|

|

|

Входы |

|

|

|

|

|

|

Выход |

||

сигнала |

a |

R |

load |

9 |

8 |

7 |

6 |

|

5 |

4 |

3 |

2 |

1 |

0 |

Q9 |

1 |

a0 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

2 |

a1 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

3 |

a2 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

4 |

a3 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

5 |

a4 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

6 |

a5 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

7 |

a6 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

8 |

a7 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

9 |

a8 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

0 |

10 |

a9 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

a0 |

11 |

a10 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

a1 |

12 |

x |

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

13 |

x |

0 |

1 |

b9 |

b8 |

b7 |

b6 |

|

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

b9 |

14 |

a13 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b8 |

15 |

a14 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b7 |

16 |

a15 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b6 |

17 |

a16 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b5 |

18 |

a17 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b4 |

19 |

a18 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b3 |

20 |

a19 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b2 |

21 |

a20 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b1 |

22 |

a21 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

b0 |

23 |

a22 |

0 |

0 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

x |

a13 |

1.2Функциональная схема

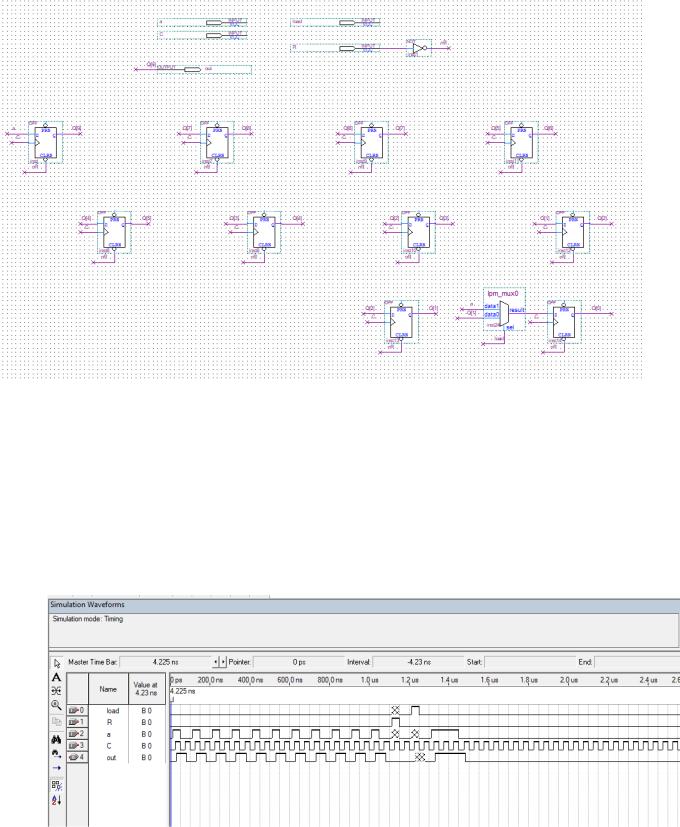

На рисунке 1.1 представлена функциональная схема регистра SISO.

3

Рисунок 1.1 – Функциональная схема регистра SISO

1.3Моделирование

На рисунке 1.2 представлено моделирование регистра SISO в режиме

Timing.

Рисунок 1.2 – Моделирование регистра SISO (Timing)

4

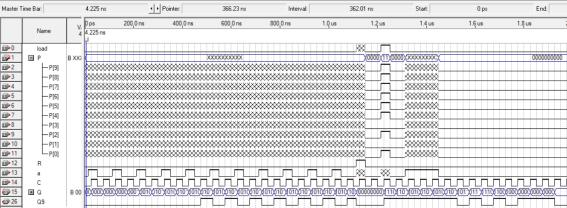

На рисунке 1.3 представлено моделирование регистра SISO в режиме

Functional.

Рисунок 1.3 – Моделирование регистра SISO (Functional)

Моделирование соответствует таблице истинности. На скриншотах подтверждается, что загрузка синхронная, а сброс асинхронный.

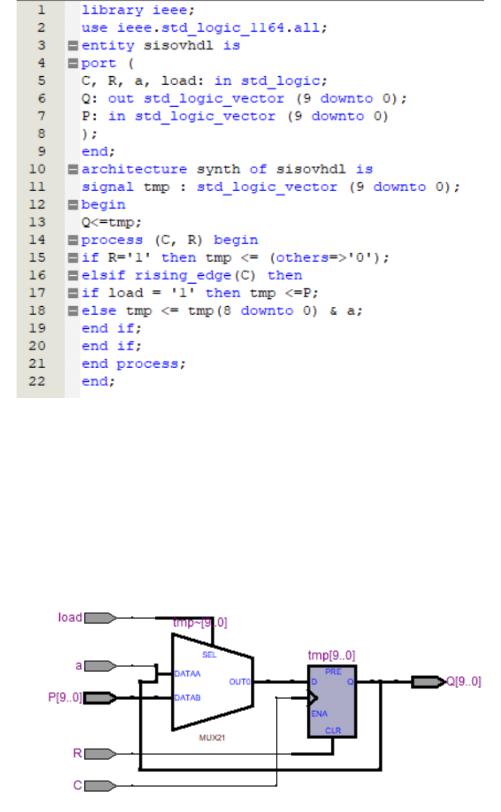

1.4Код на VHDL

На рисунке 1.4 представлено описание регистра SISO на VHDL.

5

Рисунок 1.4 – Описание регистра SISO на VHDL

1.5Схема из RTL viewer для кода VHDL

На рисунке 1.5 представлена схема из RTL viewer для кода VHDL.

Рисунок 1.5 – Схема из RTL viewer для кода VHDL

1.6Моделирование устройства, описанного кодом VHDL

6

На рисунке 1.6 представлено моделирование регистра SISO, описанного кодом VHDL.

Рисунок 1.6 – Моделирование регистра SISO (Timing)

Моделирование соответствует таблице истинности, подтверждается, что загрузка синхронная, а сброс асинхронный

7

2РЕГИСТР ТИПА SIPO

2.1Таблица истинности

Втаблице 2.1 представлена таблица истинности регистра SIPO.

Таблица 2.1 – Таблица истинности регистра SIPO

№ |

Входы |

|

|

|

|

|

Выходы |

|

|

|

|

|

||

сигнала |

sin |

R |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

a0 |

0 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

a1 |

0 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

3 |

a2 |

0 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

4 |

a3 |

0 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

5 |

a4 |

0 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

6 |

a5 |

0 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

0 |

7 |

a6 |

0 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

0 |

8 |

a7 |

0 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

0 |

9 |

a8 |

0 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

0 |

10 |

a9 |

0 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

0 |

11 |

a10 |

0 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

0 |

12 |

a11 |

0 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

a0 |

13 |

x |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

14 |

a12 |

0 |

a12 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

15 |

a13 |

0 |

a13 |

a12 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

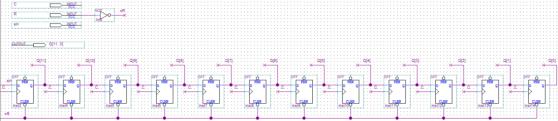

2.2Функциональная схема

На рисунке 2.1 представлена функциональная схема регистра SIPO.

Рисунок 2.1 – Функциональная схема регистра SIPO

8

2.3Моделирование

На рисунке 2.2 представлено моделирование регистра SIPO в режиме

Timing.

Рисунок 2.2 – Моделирование регистра SIPO (Timing)

На рисунке 2.3 представлено моделирование регистра SIPO в режиме

Functional.

Рисунок 2.3 – Моделирование регистра SIPO (Functional)

Моделирование соответствует таблице истинности, подтверждается, что сброс асинхронный.

2.4Код на VHDL

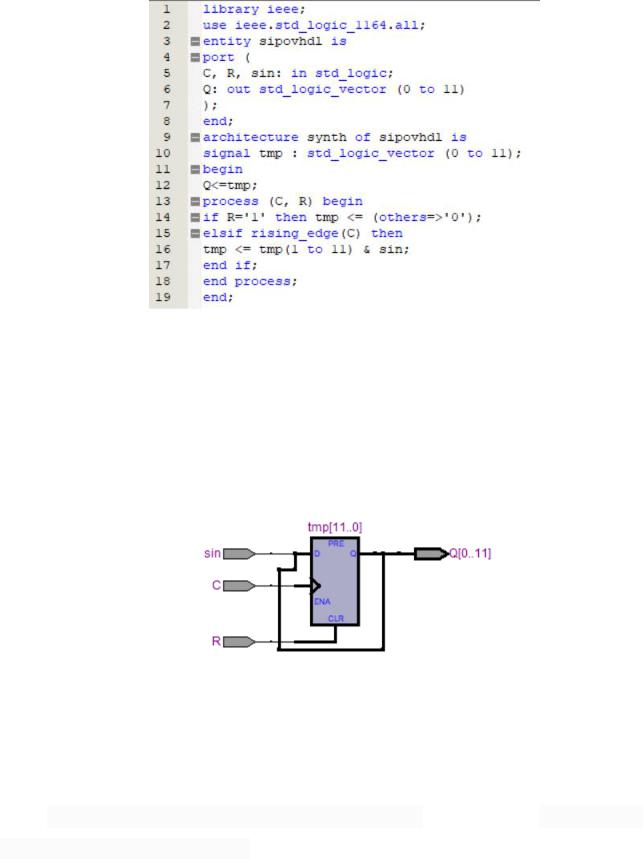

На рисунке 2.4 представлено описание регистра SIPO на VHDL.

9

Рисунок 2.4 – Описание регистра SIPO на VHDL

2.5Схема из RTL viewer для кода VHDL

На рисунке 2.5 представлена схема из RTL viewer для кода VHDL.

Рисунок 2.5 – Схема из RTL viewer для кода VHDL

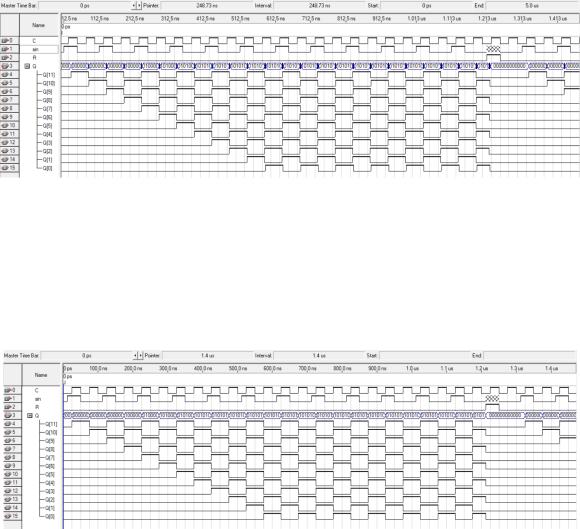

2.6Моделирование устройства, описанного кодом VHDL

На рисунке 2.6 представлено моделирование регистра SIPO, описанного кодом VHDL в режиме Timing.

10