Таблица 3.1 – Таблица истинности

|

Вход |

|

|

Выходы |

|

|

№ сигнала |

|

|

sin_out |

|

|

|

|

|

|

|

|

||

|

CLR |

4 |

3 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

0 |

1 |

1 |

1 |

1 |

16 |

0 |

1 |

0 |

0 |

0 |

0 |

17 |

0 |

1 |

0 |

0 |

0 |

1 |

18 |

0 |

1 |

0 |

0 |

1 |

0 |

19 |

0 |

1 |

0 |

0 |

1 |

1 |

20 |

0 |

1 |

0 |

1 |

0 |

0 |

21 |

0 |

1 |

0 |

1 |

0 |

1 |

22 |

0 |

1 |

0 |

1 |

1 |

0 |

23 |

0 |

1 |

0 |

1 |

1 |

1 |

24 |

0 |

1 |

1 |

0 |

0 |

0 |

25 |

0 |

1 |

1 |

0 |

0 |

1 |

26 |

0 |

1 |

1 |

0 |

1 |

0 |

27 |

0 |

1 |

1 |

0 |

1 |

1 |

28 |

0 |

1 |

1 |

1 |

0 |

0 |

29 |

0 |

1 |

1 |

1 |

0 |

1 |

30 |

0 |

1 |

1 |

1 |

1 |

0 |

31 |

0 |

0 |

0 |

0 |

0 |

0 |

32 |

0 |

0 |

0 |

0 |

0 |

1 |

33 |

1 |

0 |

0 |

0 |

0 |

0 |

34 |

0 |

0 |

0 |

0 |

0 |

1 |

11

3.2Функциональная схема

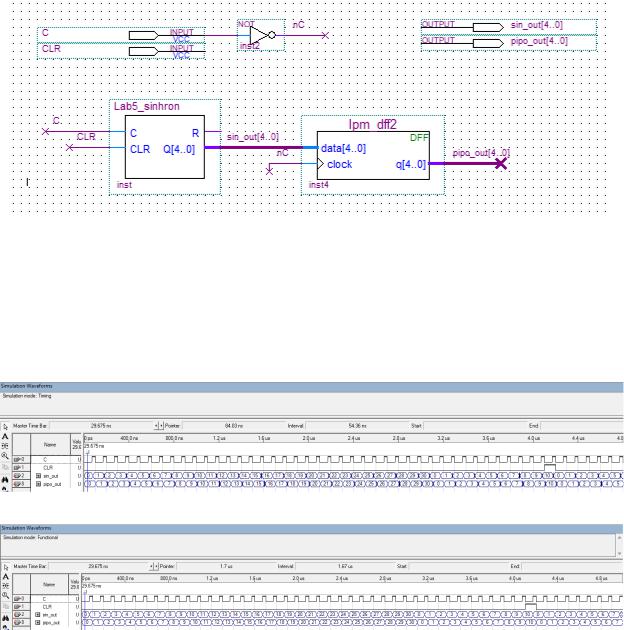

На рисунке 3.1 представлена функциональная схема.

Рисунок 3.1 - Схема синхронного счётчика

3.2Моделирование функциональной схемы

На рисунках 3.2–3.3 представлены результат моделирования в двух режимах.

Рисунок 3.2 - Результат моделирования (Timing)

Рисунок 3.3 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы истинности, представленной в таблице 3.1.

3.3Код на HDL

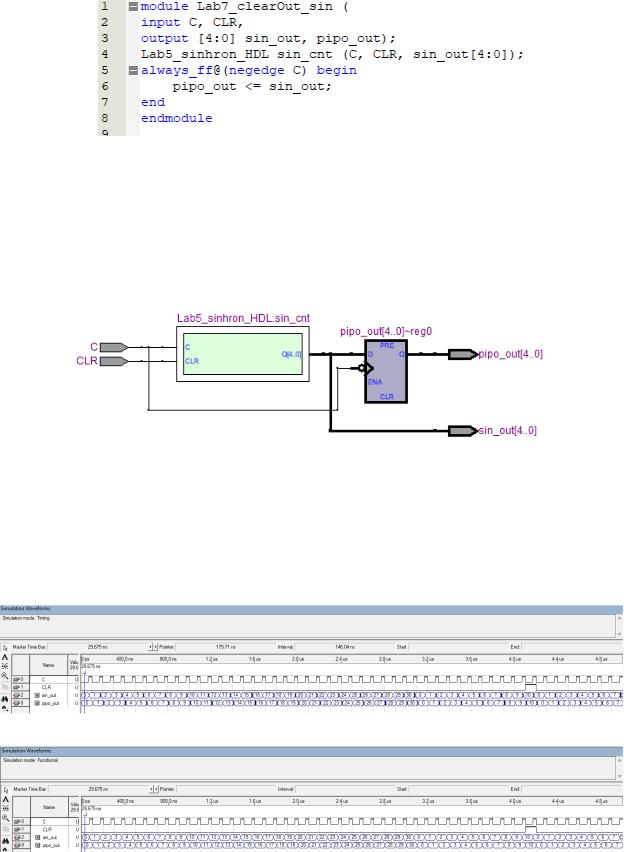

На рисунке 3.4 представлен код описания на System Verilog.

12

Рисунок 3.4 – Код описания устройства на System Verilog

3.4Схема из RTL viewer для кода HDL

На рисунке 3.5 представлена схема из RTL Viewer для кода,

написанном на System Verilog.

Рисунок 3.5 – Схема из RTL viewer

3.5Моделирование устройства, описанного кодом HDL

На рисунках 3.6–3.7 представлены результаты моделирования асинхронного счётчика, описанного на System Verilog.

Рисунок 3.6 - Результат моделирования (Timing)

Рисунок 3.7 - Результат моделирования (Functional)

Результат моделирования совпадает со значениями из таблицы истинности, представленной в таблице 3.1.

13

ВЫВОДЫ

В ходе данной работы были освоены навыки совместного использования регистров и счётчиков.

Были составлены таблицы истинности для заданных устройств согласно варианту.

Были собраны на холстах .bdf и промоделированы в двух режимах

(timing и functional) схемы вычислителя функций и счётчиков из ЛР5.

С помощью System Verilog были описаны а также промоделированы те же устройства.

Результаты моделирования каждой схемы соответствует её таблице истинности.

14