- •Введение

- •1. Физическая верификация. Характеризация топологии. Цели и задачи. Этапы верификации (drc, lvs, rcx). Моделирование с учетом паразитных элементов

- •2. Паразитные элементы. Механизмы возникновения паразитных элементов, их типы. Паразитные эффекты в топологии аналоговых устройств, их физическая сущность

- •3. Обзор программ верификации. Программы верификации Diva, Assura, Calibre

- •4. Программа верификации Diva. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •5. Программа верификации Assura. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •6. Программа верификации Calibre. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров

- •7. Моделирование с учетом паразитных элементов. Создание файла конфигураций моделирования и его настройка. Моделирование

- •8. Подготовка к производству. Правила передачи топологии. Понятие gds файла. Подготовка управляющего файла в формате gdsii

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

5. Программа верификации Assura. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

Общие сведения о приложении Assura. Assura – это программный инструмент, предназначенный для проведения полного цикла верификации, как отдельных блоков, так и ИС любого размера, независимо от типа технологии. Приложение обычно входит в пакет прикладных программ САПР Cadence. С помощью Assura проводится проверка топологии на соответствие нормам конструкторско-технологических требований (КТТ) – проверка DRC (Design Rule Checking), верификация ИС на соответствие электрической схемы разработанной топологии – LVS (Layout Versus Schematic), извлечение из топологии списка электрических связей с паразитными элементами.

На данный момент Assura является одним из наиболее распространенных и используемых инструментов для проведения.

Преимущества Assura:

- полный цикл физической проверки ИС;

- работа с большими проектами;

- высокая скорость выполнения проверок и операций;

- быстрое и удобное исправление ошибок с использованием графического пользовательского интерфейса (GUI).

Assura очень быстро выполняет иерархическую проверку (в случае многоуровневого проекта), при этом каждую ячейку анализирует только один раз, тем самым сокращая время верификации проекта. Результаты верификации отображаются в графическом пользовательском интерфейсе и не требуют какой-либо трансляции.

Запуск приложения Assura осуществляется из топологического редактора Virtuoso в одноименном меню. Здесь можно увидеть три команды, отражающие этапы верификации: «Run DRC» – проверка проектных норм, «Run LVS» – проверка соответствие топологи электрической схеме и «Run RCX» – извлечение списка электрических связей и устройств с паразитными элементами. Если топология не прошла проверку LVS, команда «Run RCX» неактивна. Как только проект пройдет процесс проверки проектных норм и верификации топологии с электрической схемой, данная команда становится активной.

При первом запуске Assura необходимо вызвать процесс из меню «Assura/Run DRC», «Assura/Run LVS» или «Assura/Run RCX». При запуске происходит следующая последовательность действий. Assura считывает run-specific file (RSF), из которого извлекает следующую информацию: название топологии, название файла проверки, имя процесса (run name), рабочую директорию, а также тип операции (DRC, LVS, RCX). Посмотреть содержимое файла run-specific file можно нажав кнопку «View RSF» в главном окне «Run Assura DRC», «Run Assura LVS», «Run Assura RCX». Сам файл RSF определятся используемым технологическим процессом, который выбирается в меню «Assura/Technology» файлом *.lib. Названия требуемых топологических слоев Assura получает из файла проверки drc.rul, а данные об этих слоях при чтении источника топологии (Design Framework II или поток GDS II).

Проверка норм проектирования (DRC). Для того чтобы выполнить проверку проектных норм в программе Assura, необходимо вызвать процесс «Assura/Run DRC» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 5.1.

Рис. 5.1. Интерфейс программы Assura DRC

В общем случае для проведения проверки проектных норм необходимо ввести/получить следующие данные:

- название топологической ячейки (Cell). При запуске Assura из редактора топологии название ячейки определяется автоматически. Однако есть возможность выбора другой ячейки через команду «Browse», где с помощью менеджера библиотек (Library Manager) выбирается файл иной требуемой ячейки в представлении layout;

- Run Name – имя процесса. Здесь необходимо ввести имя текущего процесса. Обычно при установке библиотеки (Design Kit) название процесса автоматически определяется как название топологии с приставкой _DRC;

- Run Directory – рабочая директория, где будет сохраняться текущий выполняемый процесс (по умолчанию Assura DRC);

- технологический процесс (Technology). При установленной библиотеке сведения о технологическом процессе считываются из RSF-файла, откуда Assura также считывает и название файла проверок drc.rul. Технологический процесс и технологический файл можно выбрать вручную в выпадающем меню. Если технологический процесс не определен, т.е. указан как «undefined», то необходимо ввести название файла проверки через меню «Browse».

Для того чтобы не вводить необходимые данные при каждом новом запуске Assura в программе реализована возможность сохранения текущего состояния. Сохранение текущего состояния осуществляется в меню «Assura/Save State», где в поле Name ввести название сохраняемого состояния. При следующем вызове программы можно вызвать сохраненное состояние выполнив последовательность команд «Assura/Load State», где в поле Name ввести название сохраненного состояния.

Дополнительные параметры Assura DRC. Кроме перечисленных данных, существует возможность настройки дополнительных параметров, которые могут потребоваться при проведении проверки проектных норм.

1. «Area To Be Checked». Существует возможность проводить проверку проектных норм не всей топологии, а лишь выделенной части. Для этого необходимо в поле «Area To Be Checked» выбрать «Specify Area» (по умолчанию стоит установка Full – вся топология). В результате появится дополнительное поле, где можно указать координаты того участка топологии, который нужно проверить, либо указать эти координаты выделением участка топологии, нажав кнопку «Select Area» и с помощью левой кнопки мыши выделить прямоугольную область топологии. При этом координаты области автоматически введутся в поле «Coordinates».

2. «Switch Names». При проведении проверки проектных норм существует возможность пропускать некоторые правила проверки, определенные переключателем «Switch Names». Они должны быть определены в файле проверки drc.rul. Чтобы указать, какие правила нужно пропустить, необходимо вызвать в меню «Set Switches» окна Run Assura DRC, затем, в появившемся окне «Set Switches» выбрать правило из списка.

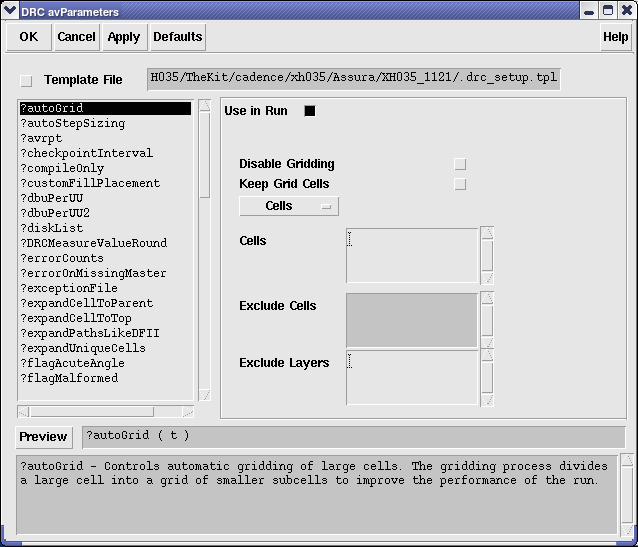

3. «avParameters». В Assura DRC существует возможность установки дополнительных правил проверки в виде avParameters.

Чтобы настроить avParameters, необходимо нажать кнопку «Modify avParameters», в результате чего откроется окно DRC avParameters, представленное на рис. 5.2.

Рис. 5.2. Окно установки дополнительных параметров проверки

В поле слева перечислены параметры, которые можно выбрать. Для активации параметра необходимо выбрать его из списка, установить флажок «Use in Run» (использовать при выполнении) и выбрать возможные варианты настойки для каждого пункта. При установке флажка «View avParameters» в окне «Run Assura DRC» открывается список установленных параметров. Ниже перечислены наиболее часто используемые параметры:

- ?expandCellToTop – вынос ячейки на верхний уровень;

- ?flagOfGrid – проверка на соответствие ячеек сетке (можно задать другую рабочую сетку);

- ?ignoreCell – указание ячеек, которые проверять не нужно (игнорирование);

- ?joinPins – указание терминалов, которые необходимо связать (в случае, если топология не является единым целым – незаконченный проект).

В состоянии по умолчанию дополнительных параметров не установлено. Выбранные параметры и их настройки также сохраняются при сохранении состояния и подгружаются при восстановлении выбранного состояния.

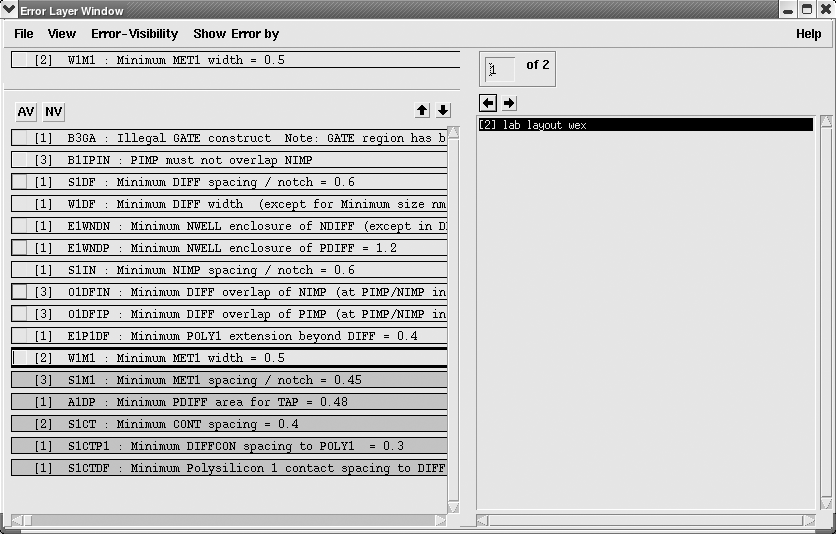

Исправление ошибок с помощью Error Layer Window (ELW). После того как все необходимые параметры указаны и проведена проверка проектных норм Assura выведет результаты проверки в окне Error Layer Window. Графический интерфейс Error Layer Window позволяет увидеть:

- слои, не соответствующие нормам КТТ технологического процесса;

- слои, находящиеся не в сетке топологического шаблона;

- нарушенные правила проектирования;

- количество нарушений по каждому правилу;

- места нарушения правил проектирования.

В ELW внизу слева перечислены правила проектирования в виде списка, которые были нарушены (обнаруженные ошибки). В каждой строке сначала указывается цвет, которым будет подсвечена ошибка данного правила, затем в квадратных скобках указано число подобных ошибок и название правила, которое описано в файле drc.rul. Обычно, в названии правила также указывается необходимая величина (в мкм.) расстояния между слоями, зазора внутри слоя или перекрытия слоев. Вверху слева указывается текущее правило проектирования и его название. Справа в поле для текущего правила указывается топологическая ячейка, в которой эта ошибка найдена. С помощью стрелок вправо / влево осуществляется переход к следующей/предыдущей ошибке, которая будет подсвечена в топологии в виде цветного полигона.

Рис. 5.3. Окно поиска и исправления ошибок Error Layer Window

Дополнительные возможности:

- с помощью кнопок «AV» (показать все) и «NV» (скрыть все) можно показать/скрыть все подсвеченные ошибки;

- правой кнопкой мыши можно изменять цвет подсветки ошибок;

- если для какого-то правила проектирования много ошибок, то их можно выбирать, вводя число в правой верхней части окна в поле «numbers». Здесь же указывается текущий номер ошибки для конкретного правила.

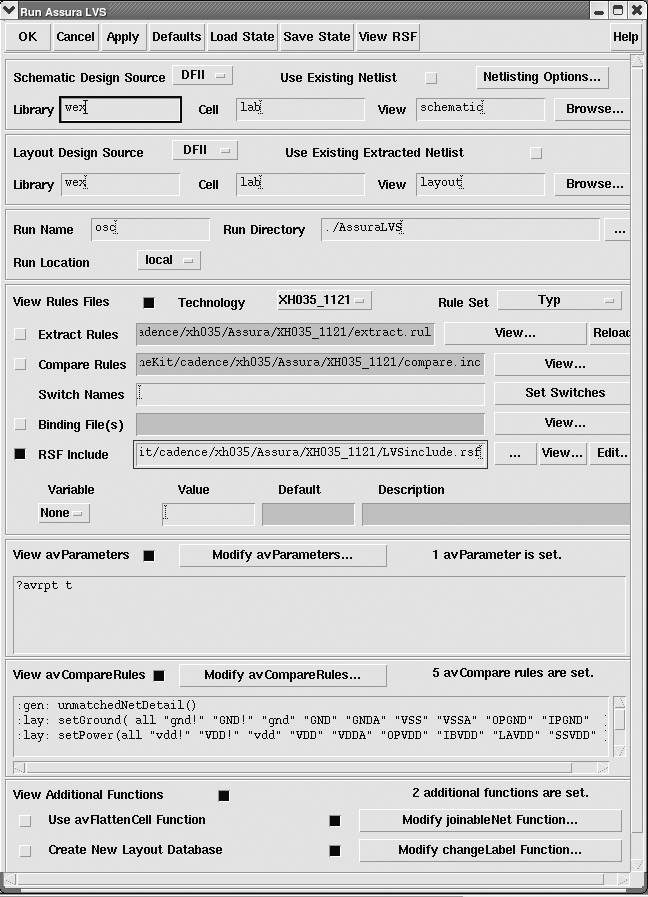

Верификация. Для того чтобы осуществить верификацию топологии и электрической схемы в программе Assura, необходимо вызвать процесс «Assura/Run LVS» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рис. 5.4.

При первом запуске «Assura/Run LVS» Assura выполняет ту же последовательность действий, что и при запуске «Assura/Run DRC». Считанные данные размещаются в базе данных (VDB). Это бинарный файл, названный <runName>.dat. В последующих операциях Assura будет работать с этой базой данных, выполняя экстрагирование списка электрических связей и проверку соответствия топологии электрической схеме.

Рабочая область Assura включает:

- название схемотехнической ячейки и библиотека ячейки

- название топологической ячейки и библиотека ячейки

- файл извлечения списка электрических связей (extract.rul);

- файл сравнения списков электрических связей топологии и схемы (compare.rul).

Рис. 5.4. Интерфейс Assura LVS

При установленной библиотеке технологического процесса все перечисленные пункты устанавливаются автоматически при вызове Assura LVS из меню окна редактора топологии ячейки Virtuoso. Так же как и в Assura DRC присутствует возможность выбора топологии и электрической схемы вручную с помощью кнопки «browse». Перечисленных параметров достаточно для запуска процесса верификации. Для того чтобы не требовалось настраивать эти пункты можно сохранить текущее состояние, выбрав в окне Run Assura LVS «Save State». Для восстановления требуемого состояния необходимо запустить из окна Run Assura LVS команду «Load State».

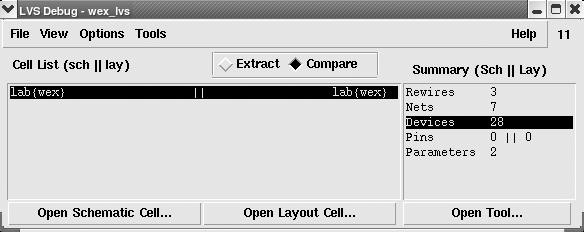

После извлечения электрической схемы из топологии автоматически запускается процесс верификации. После окончания верификации на экран будет выведен файл отчета. В случае нахождения ошибок Assura LVS сразу после закрытия окна отчета выводит на экран графический интерфейс отладки LVS Debug, показанный на рис. 5.5.

Рис. 5.5. Интерфейс отладки LVS Debug

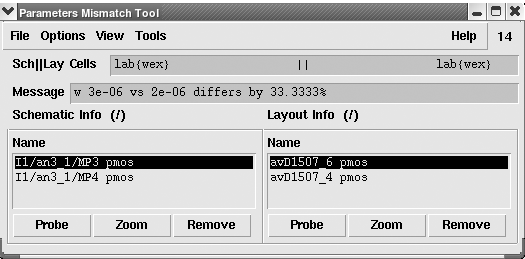

В правой части окна указаны все ошибочные приборы, сети и терминалы. Для того чтобы посмотреть ошибки необходимо выбрать тип ошибок, которые будут выведены «Rewires», «Nets», «Devices», «Pins», «Parameters» и нажать на клавишу «Open Tool». После выполнения этих действий на экран выводится окно ошибок выбранного типа. Пример такого окна, Parameters Mismatch Tool (параметрические ошибки), представлен на рис. 5.6.

Рис. 5.6. Окно параметрических ошибок Parameters Mismatch Tool

В верхней строке окна указаны названия ячеек (директорий) схемы и топологии. Строка ниже содержит информацию о расхождении параметров. Нижняя половина окна разбита на две части: информация о приборах топологии и информация о приборах схемы. При нахождении соответствия между приборами в топологии и схеме, но не соответствия их размеров Assura LVS указывает эти приборы и их тип в частях информации схемы и топологии. При выделении, например, прибора схемы выделяется соответствующий ему прибор топологии. Ошибочный прибор можно найти независимо в каждом из видов представления (схема и топология). При нажатии на клавишу «Probe» в выбранном представлении выделяется ошибочный прибор. Нажатие на клавишу «Zoom» увеличивает выделенное место до размера окна, а нажатие на клавишу «Remove» отменяет выделение прибора.

При рассмотрении ошибок Assura читает оригинальные топологические данные и данные из файла ошибок для конкретного имени процесса, и отображает ошибочные данные в топологии в виде подсвеченных фигур. Assura не изменяет базу данных топологии.

Извлечение электрической схемы с паразитными элементами. После того как проведена верификация устройства (DRC, LVS) и исправлены ошибки, необходимо провести моделирование с учетом паразитных элементов, которые обусловлены размещением слоев в топологии и их характеристиками (длина, толщина). Перед моделированием необходимо получить список электрических связей и устройств, содержащий паразитные элементы. Процесс извлечения заключается в настройке приложения Assura RCX (необходимо определить параметры экстракции паразитных элементов, их фильтрации, а также параметры входных данных) и собственно получения списка электрических связей и устройств, содержащего паразитные элементы.

Перед проведением процесса RCX необходимо провести верификацию (LVS) для того чтобы Assura обновила (получила) базу данных списка электрических цепей и устройств. В том случае если верификация не проводилась, RCX-процесс будет недоступен.

Для получения нетлиста с паразитными элементами необходимо запустить приложение экстракции из меню «Assura/Run RCX» окна редактора топологии Virtuoso. В результате выполнения команды откроется интерфейс Assura Parasitic Extraction Run Form. В структуре окна Assura RCX присутствуют пять закладок:

- Setup – определяется технологическая библиотека, выходной формат данных и ограничение правил извлечения паразитных элементов;

- Extraction – определяется тип извлекаемых паразитных элементов (R, C, RC) и область извлечения (вся топология, определенные шины);

- Filtering – определяется фильтрация паразитных элементов и шин (ограничение извлечения паразитных элементов, исключение определенных шин);

- Netlisting – определяются модели извлекаемых паразитных элементов (R, C, RC) и дополнительные возможности;

- Run Details – определяется вся информация, связанная с проведением RCX (название и директория процесса, log-файл) и машинные ресурсы (мультипроцессорность, удаленные вычисления и т.д.)

Как и в приложениях Assura DRC и Assura LVS, в Assura RCX есть кнопки (команды) для просмотра RSF-файла (View RSF), сохранения текущих настроек (Save State) и загрузки сохраненных состояний (Load State).

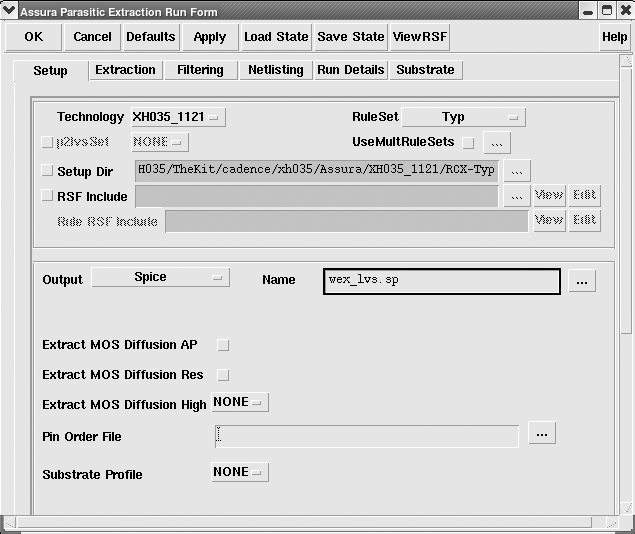

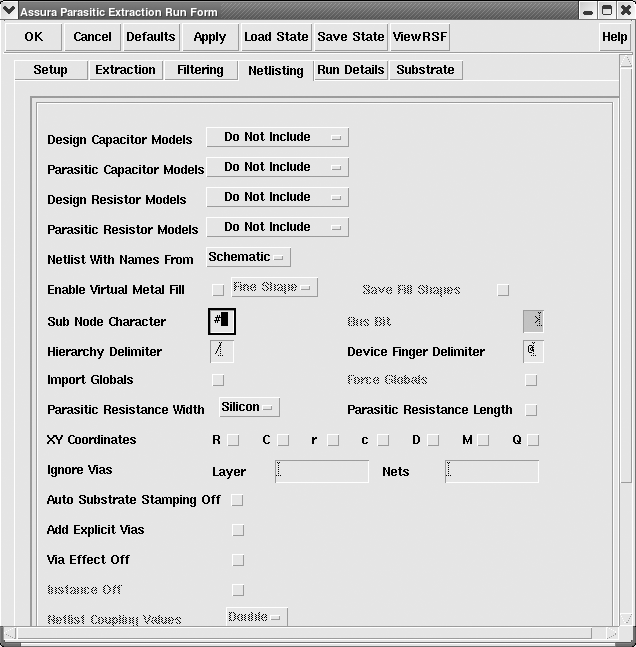

Закладка Setup показана на рис. 5.7.

Рис. 5.7. Закладка Setup приложения Assura RCX

Основные настройки окна Setup:

- Technology - выбор технологической библиотеки из списка доступных, либо указание техфайла вручную;

- Rule Set (Typical, Min, Max) - настройка правил извлечения паразитных элементов, связанная с величиной разброса параметров слоев;

- Output (Spice, Spectra, Extracted View) - указание формата выходных данных, который обычно выбирается в зависимости от используемой программы моделирования;

- Extract MOS Diffusion AP - извлечение паразитных элементов диффузионных областей MOP – транзисторов (выбирается в случае отсутствия модели);

- Extract MOS Diffusion Res - извлечение диффузионных резисторов MOP – транзистора между затвором и контактом к стоку/истоку (выбирается в случае отсутствия модели);

- Pin Order File - выбор файла, содержащего список терминалов, отличный от списка терминалов в электрической схеме и топологии;

- Substrate Profile - выбор профиля подложки, если она имеет специфическую форму.

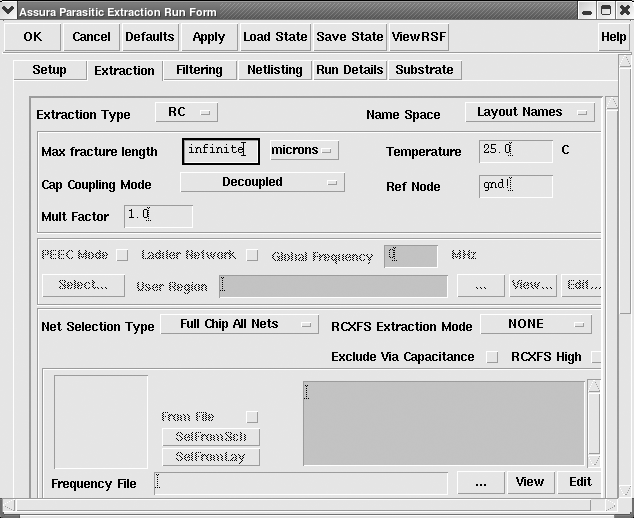

Настройки закладки Extraction показаны на рисунке 5.8.

Рис. 5.8. Закладка Extraction приложения Assura RCX

Основные настройки окна Extraction:

- Extraction Mode - метод извлечения паразитных элементов (RC – сопротивление/емкость, R – только сопротивление, C – только емкость, RLC – сопротивление \индуктивность \ емкость);

- Name Space - источник названий элементов (электрическая схема, топология);

- Ref Node - выбор нулевого потенциала (gnd);

- Max Fracture Length - сегментирование резисторов в микронах или квадратах (рисунок 6A). Сегментирование резисторов необходимо в том случае, если требуется высокая точность определения задержек при моделировании;

- Cap Extraction Mode - метод извлечения паразитных емкостей (decoupled – несвязанные емкости, coupled – связанные емкости, decoupled to substrate – несвязанные емкости, извлеченные относительно подложки). Связанные емкости используются при моделировании радиочастотных схем; извлечение паразитных емкостей относительно подложки требуется в случае, если подложка не подключена к шине земли;

- Режимы экстракции:

- Full Chip All Net – извлечение паразитных элементов для всей ИС;

- Selected Nets Proper – только для шин с определенными свойствами (аналоговые,

цифровые);

- Selected Paths – указать путь к файлу, содержащему набор шин, либо указать

шины в электрической схеме;

- Excluded Net – исключая указанные шины.

- Exclude Via Capacitance - не учитывать емкость межслойных контактов.

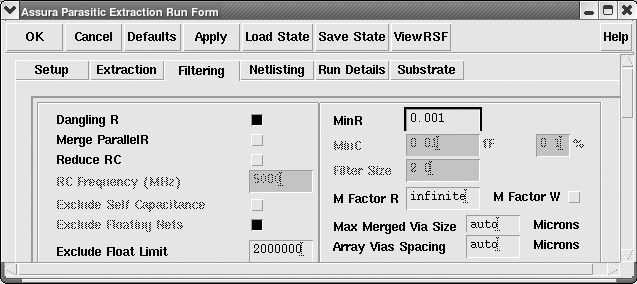

На рис. 5.9 показана закладка Filtering.

Все настройки этой закладки предназначены для задания ограничений на извлечение паразитных элементов.

Рис. 5.9. Закладка Filtering приложения Assura RCX

Основные настройки окна Filtering:

- Dangling R - не учитывать сопротивление участков шин, оставшихся неподключенными;

- Merge Parallel R - соединять резисторы;

- Reduce RC - соединять емкости;

- Exclude Floating Net - исключать неподключенные шины (noConn);

- Min R - не учитывать сопротивления, имеющие величину меньше указанной;

- Min C - не учитывать емкости, имеющие величину меньше указанной;

- M Factor R - предел, больше которого нельзя соединять параллельные сопротивления;

- M Factor W - не соединять параллельные транзисторы.

Закладка Netlisting представлена на рис. 5.10.

Рис. 5.10. Закладка Netlisting приложения Assura RCX

Все настройки этой закладки связаны с использованием моделей и отображением информации в нетлисте.

Основные настройки окна Netlisting:

- Design Capacitor Models, Parasitic Capacitor Models, Design Resistor Models, Parasitic Resistor Models - выбор моделей извлекаемых элементов;

- Netlist With Names From - источник названий элементов для нетлиста;

- Enable Virtual Metall Fill - виртуальное заполнение металлом и вычисление полученной паразитной емкости;

- XY Coordinates - вывод координат назначенных элементов в нетлисте;

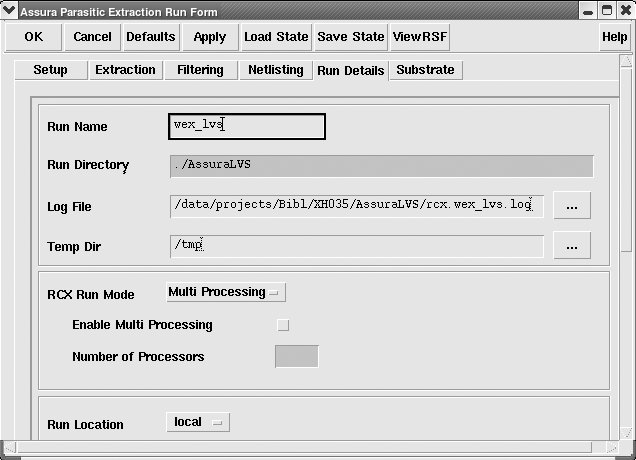

Закладка Run Details показана на рис. 5.11.

Рис. 5.11. Закладка Run Details приложения Assura RCX

Все настройки этой закладки предназначены для настройки процесса экстракции и мультипроцессорного режима экстракции.

Основные настройки окна Run Details:

- Run Name - название текущего процесса;

- Run Directory - библиотека сохранения процесса;

- Log File - расположение файла отчета результатов RCX;

- RCX Run Mode - метод выполнения процесса RCX (многопроцессорный режим, использование нескольких машин).

Запуск экстракции осуществляется после нажатия кнопку «Apply» или «OK». После окончания извлечения электрической схемы на экран будет выведено сообщение Assura RCX Run об окончании процесса. Сообщение должно содержать запись об успешном завершении процесса экстракции Assura RCX и путь расположения выходного файла.