- •Введение

- •1. Физическая верификация. Характеризация топологии. Цели и задачи. Этапы верификации (drc, lvs, rcx). Моделирование с учетом паразитных элементов

- •2. Паразитные элементы. Механизмы возникновения паразитных элементов, их типы. Паразитные эффекты в топологии аналоговых устройств, их физическая сущность

- •3. Обзор программ верификации. Программы верификации Diva, Assura, Calibre

- •4. Программа верификации Diva. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •5. Программа верификации Assura. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •6. Программа верификации Calibre. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров

- •7. Моделирование с учетом паразитных элементов. Создание файла конфигураций моделирования и его настройка. Моделирование

- •8. Подготовка к производству. Правила передачи топологии. Понятие gds файла. Подготовка управляющего файла в формате gdsii

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

3. Обзор программ верификации. Программы верификации Diva, Assura, Calibre

Этап физической верификация является важным этапом разработки аналоговых блоков, выполняемых по технологии 90 нм. Основная цель физической верификации – контроль над соблюдением правил проектирования и проверка соответствия разработанной топологии электрической схеме устройств полупроводниковой микроэлектроники.

Этапы верификации и основные требования:

1) DRC – проверка проектных норм.

На данном этапе проверяются топологические слои на соответствие конструкторско-технологическим нормам технологического процесса. Нормы КТТ определены в управляющем файле проверки DRC. Данный файл предоставляется заводом-изготовителем либо разрабатывается самостоятельно при условии знания технологического процесса и наличии требований к параметрам топологических слоев.

2) EXT - извлечение списка электрических связей и устройств (extract netlist).

Это промежуточный этап, использующийся в качестве подготовительной операции перед процессом сравнения топологии и электрической схемы. Для облегчения работы программы-верификатора в топологии расставляются терминалы (pin) для обозначения шин питания и земли, шин синхронизации, а также зеркальных и других ветвей. Кроме того, при наличии неполной топологии расстановкой терминалов, имеющих одинаковое название, обеспечивается электрическая связь не соединенных проводниками линий. На этом этапе из топологии с помощью управляющего файла экстракции извлекается электрическая схема, которая затем будет верифицироваться с принципиальной электрической схемой проекта. Управляющий файл задает правила экстракции и поставляется вместе с библиотекой элементов.

3) LVS – проверка соответствия топологии электрической схеме.

Конечный этап верификации. Сразу же после извлечения списка связей Assura запускает процесс верификации, сравнение осуществляется по правилам, описанным управляющем файле.

4) RCX – извлечение электрических связей и устройств с паразитными элементами.

Извлечение из топологии электрической схемы с паразитными параметрами производят после успешного завершения верификации. Далее производится моделирование электрической схемы с учетом паразитных элементов с целью подтверждения работоспособности разработанного блока.

Современные программные комплексы физической верификации обеспечивают выполнение перечисленных выше проверок, поддерживая при этом особенности субмикронных технологий, таких как, например, 90 нм КМОП-технологии.

УБИС, разрабатываемые с использованием 90 нм КМОП-технологий, имеют в своем составе, как правило, огромное количество структурных приборов, или, как принято, говорить вентилей. Поэтому при выполнении физической верификации таких схем крайне важным показателем является скорость выполнения проверок, особенно актуальными в этом плане являются требования для выполнения иерархического анализа.

Перечисленные выше требования предопределяют развитие современных средств физической верификации.

Основными программами, пользующимися наибольшим спросом разработчиков УБИС, являются приложения Diva и Assura, относящиеся к САПР Cadence, и Calibre компании Mentor Graphics.

Программа физической верификации Diva. Приложение Diva появилась одной из первых на рынке САПР ИС и постепенно приобрела популярность среди разработчиков. Основным достоинством данной программы является простота ее использования, минимальное количество настроек, требуемых для успешного осуществления полного цикла физической верификации больших и сложных проектов, выполненных, в том числе, с применением технологий 90 нм, поддержка всех требуемых проверок, входящих в состав комплекса верификации, приемлемая скорость выполнения проверок, удобный интерфейс поиска ошибок, простые и понятные файлы отчета о процессе и результатах проверок.

Приложения Diva поддерживают работу как с одноуровневыми, так и с иерархическими проектами, а также верификацию аналоговых, цифровых и смешанных схем, выполненных по технологии 90 нм.

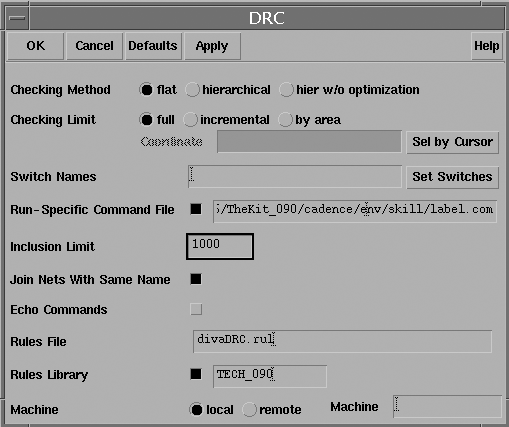

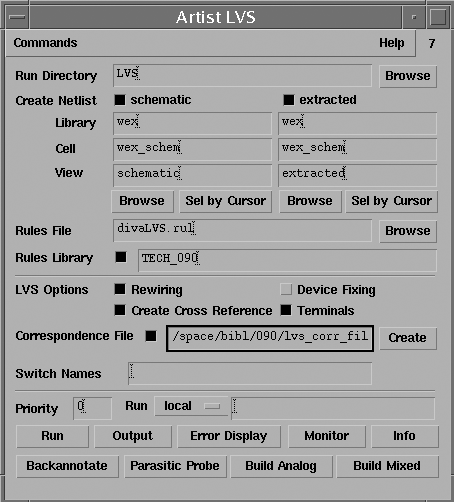

На рис. 3.1, 3.2 представлены основные окна настройки и выполнения проверок DRC и LVS соответственно.

Рис. 3.1. Приложение Diva DRC

Рис. 3.2. Приложение Diva LVS

Как видно из рис. 3.1 и 3.2, приложение Diva обладает минимальным количеством настроек и понятным интерфейсом.

Программы Diva DRC, Diva Extractor и Diva LVS вызываются из меню окна редактора топологии Virtuoso, поэтому не требуется дополнительно указывать пути и названия проверяемых файлов.

Основные настройки сводятся к указанию файлов управления проверок divaDRC.rul, divaEXT.rul и divaLVS.rul для каждого из типов проверок, технологических библиотек и установке нескольких специфических условий проверки для соответствующих проверок. После осуществления проверки DRC в окне icfb отображаются результаты выполнения. Приложение поиска ошибок DRC имеет интуитивно понятный и удобный интерфейс с минимальным количеством настроек.

Приложение экстракции обеспечивает извлечение электрической схемы из топологии, в том числе экстракцию схемы с паразитными элементами.

Верификатор Diva LVS обеспечивает сравнение схемы, экстрактированной топологии, с электрической схемой, причем образцом для сравнения может выступать как схема, так и экстракт.

Приложение поиска ошибок LVS также имеет удобный интерфейс и широкие функциональные возможности поиска и устранения ошибок.

В целом программу Diva можно охарактеризовать как одну из наиболее удобных средств физической верификации. Основным недостатком программы является ее относительно невысокое быстродействие при работе с очень большими проектами.

Приложение физической верификации Assura. Комплекс физической верификации Assura является еще одним программным продуктом компании Cadence. Приложение Assura представляет собой развитие комплекса верификации Diva и, вобрав в себя все самое лучшее из последнего продукта, также обеспечивает полномасштабную и всестороннюю проверку разработанной топологии.

Основные преимущества Assura:

- полный цикл физической проверки ИС, начиная от проверки правил проектирования и заканчивая экстракцией электрической схемы с паразитными элементами;

- высокая скорость выполнения проверок и операций;

- быстрый и удобный поиск и исправление ошибок с использованием графического пользовательского интерфейса (GUI).

- проверка как аналоговых, так и смешанных и цифровых проектов, заказных и специализированных схем, ячеек памяти.

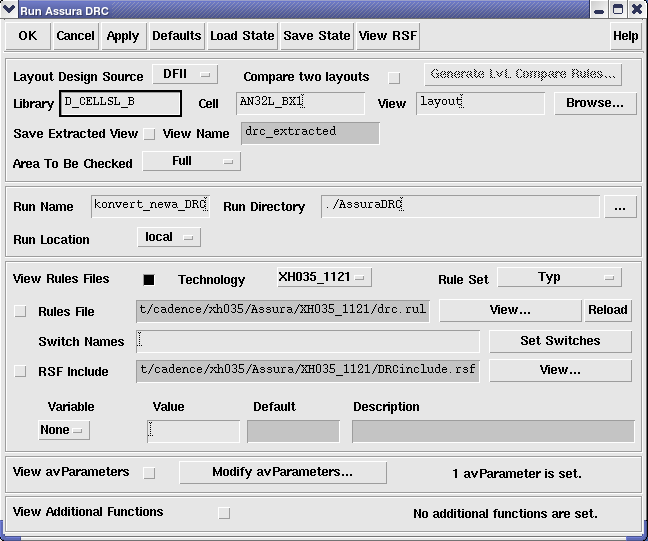

Рис. 3.3. Приложение Assura DRC

В случае запуска приложения Assura DRC пути к месту расположения и названиям проверяемых файлов устанавливаются автоматически.

Основные настройки программы:

- название топологической ячейки;

- имя процесса (DRC);

- технологический процесс;

- управляющий файл;

- av-параметры – дополнительные параметры проверки КТТ.

Assura имеет удобный графический интерфейс поиска и устранения ошибок Error Layer Window. Все найденные ошибки четко структурированы по правилам проверок и мгновенно доступны без их перебора, в отличие от Diva.

Приложение Assura LVS перед выполнением процесса верификации запускает автоматически процесс экстракции электрической схемы из топологии и выполняет его под управлением файла экстракции ext.rul. После завершения экстракции автоматически запускается непосредственно верификация проекта на основе извлеченной схемы. Поиск ошибок LVS в приложении Assura также выполняется в удобном графическом интерфейсе LVS Debug, где все ошибки четко структурированы. Кроме того Assura поддерживает обнаружение мест короткого замыкания шин и может предлагать пользователю варианты исправления некоторых ошибок.

Assura поддерживает как одноуровневые, так и иерархические проекты. Благодаря новой технологии верификации Assura не проверяет одну и ту же базовую ячейку дважды, за счет чего существенно сокращается время выполнения любых проверок.

Приложение Assura обеспечивает экстракцию электрической схемы с паразитными элементами в требуемом формате программы-симулятора.

Программа физической верификации Calibre. Calibre – это еще один программный инструмент, предназначенный для проведения полного цикла верификации, как отдельных блоков, так и ИС любого размера, независимо от типа технологии. Производителем приложения Calibre является компания Mentor Graphics. Продукт Calibre является одним из самых успешных проектов компании.

В настоящее время система верификации Calibre занимает самую значительную долю рынка среди всех популярных систем. Такое положение на рынке САПР пакет Calibre смог занять благодаря мощному и быстрому алгоритму проверок, позволяющему работать с любыми технологиями, в том числе субмикронными 90 нм. С помощью Calibre проводится проверка топологии на соответствие нормам конструкторско-технологических требований (КТТ) – проверка DRC, верификация ИС на соответствие электрической схемы разработанной топологии – LVS, извлечение из топологии списка электрических связей с паразитными элементами.

Платформа Calibre отвечает всем основным современным требованиям, реализуя комплексный подход к задаче подготовки проекта к производству. Поддержка всех основных форматов и баз данных проектирования СБИС позволяет легко встраивать средства платформы в существующие маршруты проектирования. Такой набор характеристик обеспечил системе Calibre широкое распространение и коммерческий успех.

Преимущества Calibre:

- полный цикл физической проверки ИС;

- работа с большими и ультрабольшими проектами;

- высокая скорость выполнения проверок;

- быстрое и удобное исправление ошибок с использованием графического пользовательского интерфейса;

- автоматическая генерация данных для фотошаблонов.

Calibre является одной из самых быстрых систем физической верификации, применяемых для иерархической проверки топологии. Быстродействие обеспечивается благодаря применению новой технологии распознавания неявных иерархических структур и учета повторяемости блоков, а также механизму, анализирующему повторяемости полигонов. Результаты верификации отображаются в графическом пользовательском интерфейсе и не требуют какой-либо трансляции.

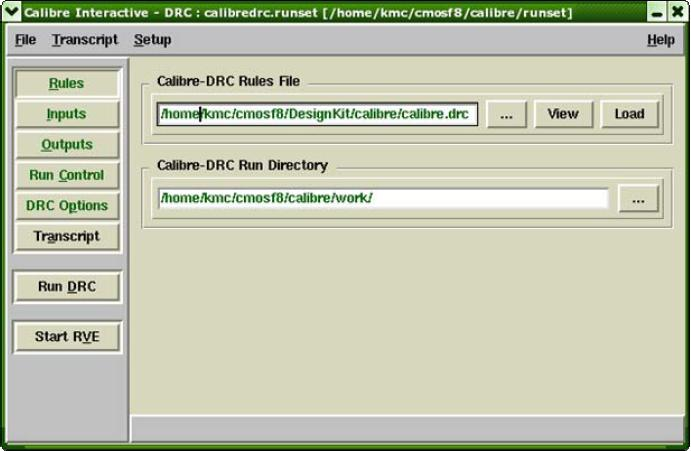

Рис. 3.4. Интерфейс программы Calibre DRC

Перед началом проверки правил проектирования необходимо указать путь к файлу правил проектирования, рабочий каталог, название файла верхнего уровня, название файла отчета, а также выбрать из списка правил проверки требуемые правила или группы правил.

При обнаружении ошибок будет доступен их анализ с помощью интерактивного приложения Calibre RVE, в котором все ошибки четко структурированы по правилам и доступны независимо друг от друга.

Форма настройки проверки LVS похожа на приложение Calibre DRC. Кроме перечисленных настроек здесь присутствуют настройки типа проверок:

- иерархическая или одноуровневая;

- верификация топология-нетлист, нетлист-нетлист.

Поиск и исправление ошибок LVS также выполняется в интерактивном интерфейсе RVE.

Экстракция паразитных элементов осуществляется в приложении Calibre PEX. Возможны как синтез нетлиста требуемого формата, так и электрической схемы с паразитными элементами. Опции экстракции выбираются в основном окне PEX.

При работе с топологией приложение Calibre конвертирует ее в автоматическом режиме в формат GDSII с помощью библиотечного map-файла и, в дальнейшем, работает с этим форматом. GDS-файл, созданный верификатором во время последней удачной LVS-проверки, одновременно является выходным управляющим файлом, передаваемым изготовителю кристаллов.