- •Запоминающие устройства

- •Запоминающие устройства

- •Классификация ЗУ

- •Классификация ЗУ

- •Условные обозначения типов БИС ЗУ

- •Основные параметры ЗУ

- •Примеры обозначения микросхем ЗУ

- •Организация ОЗУ

- •Структура ЗУ со словарной организацией

- •Особенности ЗУ со словарной организацией

- •Структура ЗУ с матричной организацией

- •Особенности ЗУ с матричной организацией

- •Структура ЗУ с комбинированной выборкой

- •Функционирование ЗУ с комбинированной выборкой

- •Элементы памяти ОЗУ статического типа

- •Элементы памяти ОЗУ статического типа

- •Элемент памяти динамического типа на МДП-транзисторах

- •Постоянные запоминающие устройства. Классификация

- •Виды постоянных запоминающих устройств

- •ПЗУ матричного типа. Схема матрицы

- •ПЗУ матричного типа. Топология матрицы

- •Структура МНОП-транзистора

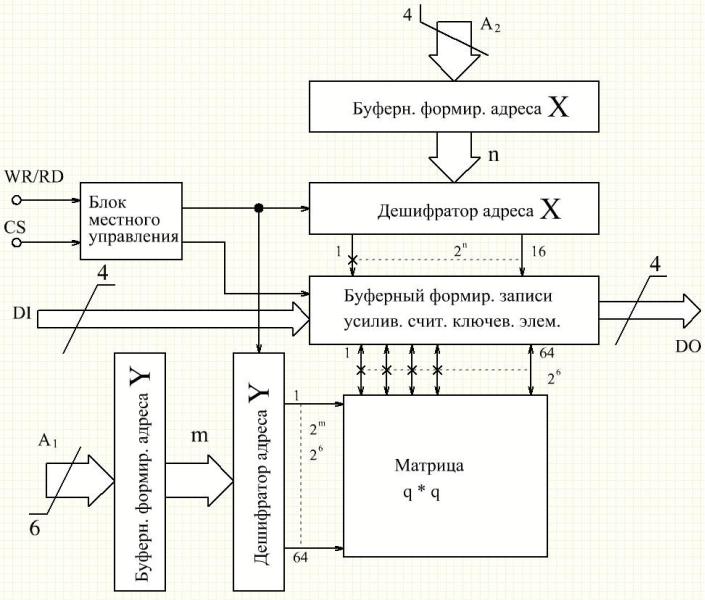

Структура ЗУ с комбинированной выборкой

МИЭМ НИУ ВШЭ. Сафонов С.Н.

Функционирование ЗУ с комбинированной выборкой

При обращении к ЗУ выходы четырех формирователей записи с помощью ключевых элементов подключается к 4 из 64 столбцов матрицы. При этом производится запись в 4 элемента памяти той строки матрицы, которая активизирована дешифратором Х . Остальные ячейки данной строки находятся в состоянии хранения информации.

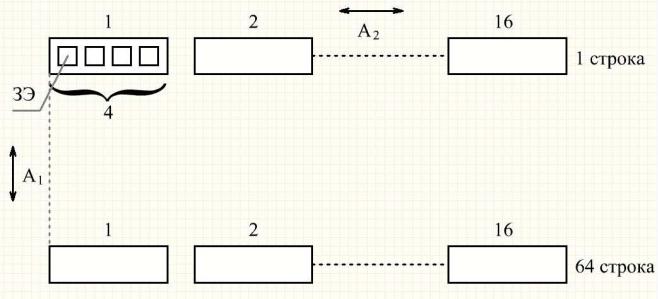

Организация матрицы запоминающих элементов

МИЭМ НИУ ВШЭ. Сафонов С.Н.

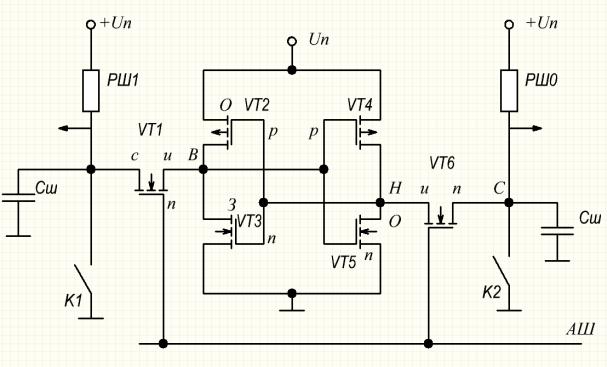

Элементы памяти ОЗУ статического типа

Элемент памяти на КМДП-транзисторах (К132РУ4)

VT1, VT6 – двунаправленные ключи ввода-вывода. В режиме хранения они закрыты. В режиме записи и считывания – открыты сигналом на адресной (словарной) шине.

VT2 и VT4 активные нагрузки транзисторов VT3 и VT5, которые образуют триггер.

МИЭМ НИУ ВШЭ. Сафонов С.Н.

Элементы памяти ОЗУ статического типа

Считывание

Перед считыванием на разрядные шины РШ0 и РШ1 подается напряжение источника питания, емкости Cш предварительно заряжаются до высокого уровня (ключи разомкнуты). На АШ подается высокий потенциал. Один из ключей VT1 или VT6 на стоке/истоке которого низкий уровень напряжения, открывается и подключает плечо триггера к соответствующей РШ. В цепи возникает ток, разряжающий емкость РШ и являющийся признаком считанной «1». Триггер при считывании не переключается.

Хранение

На АШ низкий уровень напряжения, VT1 и VT6 закрыты и изолируют триггер от разрядных шин.

Может происходить считывание из других элементов памяти через РШ0 и РШ1.

Запись

На РШ1 и РШ0 подаются противофазные напряжения через ключи К1 и К2. С некоторой задержкой возбуждается адресная шина, и открываются транзисторы VT1 и VT6, затворы которых имеют более положительный потенциал по сравнению с их стоками/истоками. Затвор VT3 и сток VT5 триггера подключаются к РШ.

Преимущества Имеют максимальное быстродействие Недостатки

•Значительное сложность схемы, малая степень интеграции микросхем ЗУ

•Область применения

Встроенная память процессоров, кэш-память функциональных узлов и контроллеров

МИЭМ НИУ ВШЭ. Сафонов С.Н.