- •CONTENTS FOR VOLUME 2A AND 2B

- •1.2 Overview of Volume 2A and 2B: Instruction Set Reference

- •1.3 NOTATIONAL CONVENTIONS

- •1.3.1 Bit and Byte Order

- •1.3.2 Reserved Bits and Software Compatibility

- •1.3.3 Instruction Operands

- •1.3.4 Hexadecimal and Binary Numbers

- •1.3.5 Segmented Addressing

- •1.3.6 Exceptions

- •1.3.7 A New Syntax for CPUID, CR, and MSR Values

- •1.4 Related Literature

- •2.1.1 Instruction Prefixes

- •2.1.2 Opcodes

- •2.1.3 ModR/M and SIB Bytes

- •2.1.4 Displacement and Immediate Bytes

- •2.2.1 REX Prefixes

- •2.2.1.1 Encoding

- •2.2.1.2 More on REX Prefix Fields

- •2.2.1.3 Displacement

- •2.2.1.5 Immediates

- •2.2.2 Additional Encodings for Control and Debug Registers

- •CHAPTER 3 Instruction Set Reference, A-M

- •3.1 Interpreting the Instruction Reference Pages

- •3.1.1 Instruction Format

- •3.1.1.1 Opcode Column in the Instruction Summary Table

- •3.1.1.2 Instruction Column in the Opcode Summary Table

- •3.1.1.4 Compatibility/Legacy Mode Column in the Instruction Summary Table

- •3.1.1.5 Description Column in the Instruction Summary Table

- •3.1.1.6 Description Section

- •3.1.1.7 Operation Section

- •3.1.1.9 Flags Affected Section

- •3.1.1.10 FPU Flags Affected Section

- •3.1.1.11 Protected Mode Exceptions Section

- •3.1.1.16 Compatibility Mode Exceptions Section

- •ADDSUBPD: Packed Double-FP Add/Subtract

- •ADDSUBPS: Packed Single-FP Add/Subtract

- •FISTTP: Store Integer with Truncation

- •HADDPD: Packed Double-FP Horizontal Add

- •HADDPS: Packed Single-FP Horizontal Add

- •HSUBPD: Packed Double-FP Horizontal Subtract

- •HSUBPS: Packed Single-FP Horizontal Subtract

- •LDDQU: Load Unaligned Integer 128 Bits

- •MONITOR: Setup Monitor Address

- •MOVDDUP: Move One Double-FP and Duplicate

- •MOVSHDUP: Move Packed Single-FP High and Duplicate

- •MOVSLDUP: Move Packed Single-FP Low and Duplicate

- •MWAIT: Monitor Wait

- •INTEL SALES OFFICES

INSTRUCTION SET REFERENCE, A-M

HADDPD: Packed Double-FP Horizontal Add

|

|

64-Bit |

Compat/ |

|

Opcode |

Instruction |

Mode |

Leg Mode |

Description |

66 0F 7C /r |

HADDPD xmm1, |

Valid |

Valid |

Horizontal add packed double- |

|

xmm2/m128 |

|

|

precision floating-point values |

|

|

|

|

from xmm2/m128 to xmm1. |

|

|

|

|

|

Description

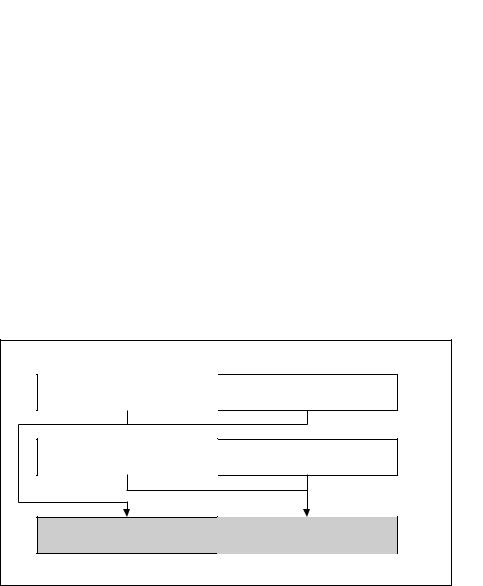

Adds the double-precision floating-point values in the high and low quadwords of the destination operand and stores the result in the low quadword of the destination operand.

Adds the double-precision floating-point values in the high and low quadwords of the source operand and stores the result in the high quadword of the destination operand. See Figure 3-10.

+$''3' [PP [PP P |

|

|

|

|

[PP |

> @ |

> @ |

|

|

|

P |

> @ |

> @ |

[PP |

[PP P > @ |

|

5HVXOW |

|

[PP > @ [PP > @ |

|

[PP P > @ |

|

[PP |

> @ |

> @ |

|

|

|

20 |

Figure 3-10. HADDPD: Packed Double-FP Horizontal Add

In 64-bit mode, use of the REX.R prefix permits this instruction to access additional registers (XMM8-XMM15).

3-422 Vol. 2A |

HADDPD: Packed Double-FP Horizontal Add |

INSTRUCTION SET REFERENCE, A-M

Operation

xmm1[63:0] = xmm1[63:0] + xmm1[127:64]; xmm1[127:64] = xmm2/m128[63:0] + xmm2/m128[127:64];

Intel C/C++ Compiler Intrinsic Equivalent

HADDPD __m128d _mm_hadd_pd(__m128d a, __m128d b)

Exceptions

When the source operand is a memory operand, the operand must be aligned on a 16-byte boundary or a general-protection exception (#GP) will be generated.

Numeric Exceptions

Overflow, Underflow, Invalid, Precision, Denormal.

Protected Mode Exceptions

#GP(0) |

For an illegal memory operand effective address in the CS, DS, ES, FS or |

|

GS segments. |

|

If a memory operand is not aligned on a 16-byte boundary, regardless of |

|

segment. |

#SS(0) |

For an illegal address in the SS segment. |

#PF(fault-code) |

For a page fault. |

#NM |

If CR0.TS[bit 3] = 1. |

#XM |

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 1). |

#UD |

If CR0.EM[bit 2] = 1. |

|

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 0). |

|

If CR4.OSFXSR[bit 9] = 0. |

|

If CPUID.01H:ECX.SSE3[bit 0] = 0. |

Real Address Mode Exceptions |

|

GP(0) |

If any part of the operand would lie outside of the effective address space |

|

from 0 to 0FFFFH. |

|

If a memory operand is not aligned on a 16-byte boundary, regardless of |

|

segment. |

#NM |

If CR0.TS[bit 3] = 1. |

HADDPD: Packed Double-FP Horizontal Add |

Vol. 2A 3-423 |

INSTRUCTION SET REFERENCE, A-M

#XM |

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 1). |

#UD |

If CR0.EM[bit 2] = 1. |

|

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 0). |

|

If CR4.OSFXSR[bit 9] = 0. |

|

If CPUID.01H:ECX.SSE3[bit 0] = 0. |

Virtual 8086 Mode Exceptions

GP(0) |

If any part of the operand would lie outside of the effective address space |

|

from 0 to 0FFFFH. |

|

If a memory operand is not aligned on a 16-byte boundary, regardless of |

|

segment. |

#NM |

If CR0.TS[bit 3] = 1. |

#XM |

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 1). |

#UD |

If CR0.EM[bit 2] = 1. |

|

For an unmasked Streaming SIMD Extensions numeric exception |

|

(CR4.OSXMMEXCPT[bit 10] = 0). |

|

If CR4.OSFXSR[bit 9] = 0. |

|

If CPUID.01H:ECX.SSE3[bit 0] = 0. |

#PF(fault-code) |

For a page fault. |

Compatibility Mode Exceptions

Same exceptions as in Protected Mode.

64-Bit Mode Exceptions

#SS(0) |

If a memory address referencing the SS segment is in a non-canonical |

|

form. |

#GP(0) |

If the memory address is in a non-canonical form. |

|

If memory operand is not aligned on a 16-byte boundary, regardless of |

|

segment. |

#PF(fault-code) |

For a page fault. |

#NM |

If CR0.TS[bit 3] = 1. |

#XM |

If an unmasked SIMD floating-point exception and CR4.OSXM- |

|

MEXCPT[bit 10] = 1. |

3-424 Vol. 2A |

HADDPD: Packed Double-FP Horizontal Add |

|

INSTRUCTION SET REFERENCE, A-M |

#UD |

If an unmasked SIMD floating-point exception and CR4.OSXM- |

|

MEXCPT[bit 10] = 0. |

|

If CR0.EM[bit 2] = 1. |

|

If CR4.OSFXSR[bit 9] = 0. |

|

If CPUID feature flag SSE3 is 0. |

HADDPD: Packed Double-FP Horizontal Add |

Vol. 2A 3-425 |