- •Физические основы электроники Электрофизические методы исследования полупроводников и полупроводниковых приборов

- •Введение в настоящем пособии излагаются основные темы дисциплин, связанных с основами работы полупроводниковых приборов.

- •Требования к подготовке, выполнению и защите работ

- •Тема 1. Приборы, используемые для проведения исследований полупроводниковых приборов

- •1.1. Автоматические мосты переменного тока

- •1.2. Осциллографы

- •1.3. Генераторы

- •Тема 2. Проводимость полупроводников и металлов лабораторная работа № 2.1

- •2.1. Терморезисторы: термисторы и позисторы

- •Подготовка к работе

- •Измерения и обработка результатов

- •Отчетные материалы

- •Лабораторная работа № 2.2

- •2.2. Общие сведения

- •Подготовка к работе

- •Измерения и обработка результатов

- •1. Подготовка к работе

- •2. Исследование вольтамперной характеристики варистора

- •7. Исследование зависимости сопротивления от температуры

- •Отчетные материалы

- •Лабораторная работа № 2.3

- •2.3. Определение типа носителей в полупроводниках

- •2.3.1. Метод термозонда

- •2.3.2. Метод Холла

- •2.3.3. Определение концентрации и подвижности носителей

- •Подготовка к работе

- •Измерения и обработка результатов

- •1. Определение типа носителей с помощью метода термозонда

- •1.1. Подготовка к работе

- •1.2. Определение типа носителей разных кристаллов

- •2. Исследования по методу Холла

- •2.1. Определение типа основных носителей в датчике Холла

- •2.3. Исследование вольтамперной характеристики датчика

- •2.4. Определение микропараметров кристалла датчика Холла

- •2.6. Определение зависимости эдс Холла от величины тока

- •2.9. Определение зависимости эдс Холла величины индукции в

- •Отчетные материалы

- •Тема 3. Полупродниковые диоды Лабораторная работа №3.1 ″Исследование полупроводниковых диодов″

- •3.1. Характеристики полупроводниковых диодов

- •Подготовка к работе

- •Измерения и обработка результатов

- •1. Начальные установки

- •2. Исследование вольтамперной характеристики диода при t0

- •2.1. Исследование прямой ветви вах диода д2

- •2.2. Исследование обратной ветви вах диода д2

- •3*. Исследование вах диодов различных типов

- •4. Исследование зависимости обратного тока диода от температуры

- •Отчетные материалы

- •Лабораторная работа № 3.2

- •3.2. Полупроводниковые стабилитроны и стабисторы

- •3.3. Описание стенда

- •Измерения и обработка результатов

- •2. Исследование вольтамперной характеристики стабилитрона при комнатной температуре

- •5. Исследование влияния температуры на напряжение Uст

- •Отчетные материалы

- •Лабораторная работа №3.3

- •3.4. Характеристики светодиодов

- •3.4.1. Управляемые источника света. Светодиоды

- •3.4.2. Строение светодиодов

- •3.4.3. Общие сведения об обозначении светодиодов

- •3.4.4. Особенности лабораторной установки

- •Отчетные материалы

- •Лабораторная работа № 3.4

- •3.5. Общие сведения о фотоприемниках

- •3.5.2. Параметры и характеристики фоторезистора

- •3.5.3. Особенности работы фотодиодов

- •3.5.4. Описание установки

- •Подготовка к работе

- •Измерения и обработка результатов

- •3. Исследование параметров электрического сигнала от генератора

- •6. Определение параметров импульса эдс от облучаемого фотодиода

- •10. Определение параметров импульса в цепи фоторезистора

- •11. Оценка параметров сигнала от резистора Rизм

- •16*. Исследование величины светового потока от светодиода

- •Отчетные материалы

- •Тема 4. Биполярные транзисторы Лабораторная работа №4.1

- •4.1. Характеристики биполярных транзисторов

- •4.1.1. Схемы включения биполярных транзисторов

- •4.1.2. Схема с общей базой

- •4.1.3. Схема с общим эмиттером

- •4.1.4. Описание установки

- •Подготовка к работе

- •Измерения и обработка результатов

- •1. Исследование схемы с общей базой

- •1.2. Исследование входных характеристик транзистора в схеме об

- •1.6. Исследование выходных характеристик транзистора в схеме об

- •1.12*. Исследование характеристики обратной связи в схеме об

- •1.14. Исследование характеристик передачи тока в схеме об

- •2. Исследование схемы с общим эмиттером

- •2.2. Исследование входных характеристик транзистора в схеме оэ

- •2.6. Исследование выходных характеристик транзистора в схеме оэ

- •2.11*. Исследование характеристики обратной связи в схеме оэ

- •2.13. Исследование характеристики передачи тока в схеме оэ

- •Отчетные материалы

- •Тема 5. Полевые транзисторы Лабораторная работа № 5.1

- •5.1. Характеристики полевого транзистора

- •5.1.1. Полевой транзистор с управляющим p-n-переходом

- •5.1.2. Полевой транзистор с изолированным затвором

- •5.1.3. Особенности схемы измерения

- •Подготовка к работе

- •Измерения и обработка результатов

- •2. Исследование стоковой (выходной) характеристики

- •Отчетные материалы

- •Тема 6. Элементы технологии производства имс Лабораторная работа № 6.1

- •6.1. Элементы технологии изготовления имс

- •6.1.1. Классификация имс

- •6.1.2. Понятие о технологическом цикле производства имс

- •6.1.3. Производство планарного биполярного транзистора

- •6.1.4. Производство планарного полевого транзистора

- •6.1.5. Структура транзисторов статических микросхем памяти

- •6.1.6. Общие сведения о топологии микросхем памяти

- •6.1.7. Описание установки и процедуры испытаний

- •Подготовка к работе

- •Измерения и обработка результатов

- •1. Исследование элементов технологии гибридных имс

- •1.4. Исследование сопротивления резисторов на бгис

- •2. Исследование элементов технологии твердотельных имс

- •2.4. Градуировка окуляров с помощью дифракционной решетки

- •3. Исследование твердотельных микросхем на установке "мим"

- •4. Анализ топологии и параметров микросхемы памяти

- •Отчетные материалы

- •Задачи по темам Аналоговая и Цифровая Электроника

- •П2. Диоды и тиристоры

- •П3. Источники вторичного напряжения

- •П4. Транзисторы

- •П5. Аналоговые устройства

- •П6. Операционные усилители и схемы на их основе

- •П7. Преобразовательные устройства и генераторы

- •П8. Стабилизаторы

- •П9. Логические микросхемы

- •П10. Логические схемы

- •П11. Схемы на лэ

- •П12. Триггеры

- •П13. Регистры и счетчики

- •П14. Преобразователи кодов

- •П15. Мультиплексоры, демультиплексоры, сумматоры

- •П16. Цифро-аналоговые преобразователи

- •П17. Микросхемы (технология и устройство)

- •Рекомендуемая литература Основная литература

- •Дополнительная

6.1.3. Производство планарного биполярного транзистора

Упрощенное представление этапов процесса производства кремниевого планарного биполярного p-n-p-транзистора, формируемого на поверхности кристаллической подложки кремния, показана на рис. 6.1, 6.2.

Рис. 6.1. Структура поперечного сечения пластины (а-е) и УГО транзистора (ж)

Из слитков кремния (рис. 6.1, а) изготавливают тонкие пластины (подложки), одна их поверхностей которых полируется, а затем окисляется во влажной среде. Вследствие этого на подложке образуется изоляционный слой двуокиси кремния (SiO2). Поверх окисла наносится слой светочувствительного полимерного материала – фоторезиста, который под действием облучения светом изменяет свои химические свойства. Например, негативный фоторезист под действием ультрафиолета так полимеризуется, что не растворяется и не удаляется специальными растворителями с засвеченных участков подложки. Напротив, позитивный фоторезист – растворяется и удаляется после облучения, а на необлученных участках не удаляется химикатами, для этой цели используют другие травители (ультразвук и т. п.).

К покрытой фоторезистом подложке прижимается контактным способом стеклянный фотошаблон (фотомаска), на котором имеются прозрачные и непрозрачные участки в зависимости от топологии микросхемы и свойств выбранного фоторезиста.

При фотолитографии фоторезист облучается ультрафиолетом, при ретнгенолучевой литографии – рентгеновским излучением, при электронографии – потоком электронов, что, как отмечено выше, позволяет уменьшить минимальные размеры элементов структуры и, соответственно, увеличить степень интеграции K.

Следует отметить, что с помощью стеклянного фотошаблона на поверхности плоской подложки одновременно формируются сотни одинаковых структур будущих транзисторов, количество которых ограничивается диаметром подложки кремния (диаметром исходного слитка) и размерами одной микросхемы.

Пластина (рис. 6.1, б) с засвеченным, например, позитивным фоторезистом погружается в травитель, который растворяет участки фоторезиста, на которые попадали кванты света, а также слои окисла под засвеченными участками. В результате травления (проявления фоторезиста) на подложке образуются участки чистой поверхности кремния окна. Затем в другом травителе, растворяющем незасвеченный фоторезист, но не растворяющим пленку SiO2, удаляется оставшийся фоторезист. В результате этой операции на подложке имеются многочисленные открытые окна, разделенные слоями окисла.

Через маску (специальную пластину с необходимыми отверстиями) в подложку через окна вводят ионы, например, бора (диффузией, облучением ионными пучками и т. п.), вследствие чего под окном образуется карман – р-область (рис. 6.1, в).

Путем последующих итераций технологического процесса (рис. 6.1, г, д) на пластине формируется n-область в р-кармане (например, диффузией донорной примеси в объем) и, наконец, р-область, выступающая в качестве будущего эмиттера биполярного транзистора p-n-p-типа.

После формирования базы, эмиттера и коллектора транзистора (рис. 6.1, е) на поверхности создаются металлические контакты (например, из алюминия). Для устранения дополнительных p-n-переходов, непосредственно примыкающих к металлическим контактам, на соответствующих контактах создаются так называемые сильно легированные области n+– и p+ –типа.

При современных технологиях размеры микротранзистора (интегральный транзистор), включая эмиттер, базу, коллектор, составляют не более 5–10 мкм.

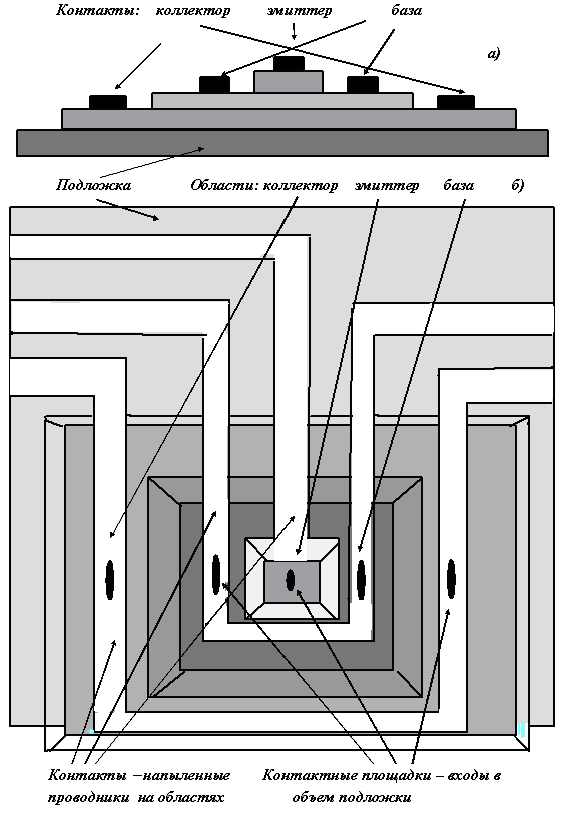

Топология микросхем – определенная конфигурация и расположение элементов на поверхности кристалла (рис. 6.2, 6.3). Первоначально топология создается специальной программой ЭВМ, на основе которой конструируются специальные фотошаблоны. Впоследствии методами фотолитографии разработанная топология воплощается в кристалле.

Рис. 6.2. Топология планарного биполярного транзистора: а – вид сбоку; б – вид сверху

Минимальные поверхностные размеры отдельного эмиттера, базы, коллектора, очевидно, ограничивает суммарное количество транзисторов (степени интеграции) в конструкции с подобной топологией.

На одной пластине (подложка кремния толщиной до 100 мкм) формируется одновременно несколько сотен микросхем. На рис. 6.3, б пунктиром обозначена область, занимаемая одним биполярным транзистором. Например, если площадь, занимаемая одним транзистором равна примерно 50х30 мкм2, то на пластине размером 1х1 мм2 можно разместить не более 1 мм2/1500·10–6 мм2 = 666 элементов. Таким образом, микросхема, изготовленная на основе устаревшей технологии, имеет степень интеграции не более К = 3.

Рис. 6.3. Топология планарных биполярных транзисторов в микросхеме: а – вид сбоку; б – вид сверху (пунктиром ограничена область одного транзистора); в – электрическая схема двух планарных транзисторов

Как правило, в состав микросхемы входят многочисленные транзисторы, которые, в частности, могут соединяться по схемам ОБ, ОЭ, ОК, объединяться параллельно с целью увеличения тока (мощности) и т. п.

Топология нескольких биполярных транзисторов в твердотельной микросхеме представлена на рис. 6.3, где приведены два планарных биполярных p-n-p-транзистора, имеющих объединенные (общие) коллекторы, эмиттеры, но индивидуальные входы баз. Минимальные линейные размеры элементов, подобных ИС, не превышают 2,5 мкм.

Рис. 6.4. Процесс формирования планарного (а-в) и применение (г) КМОП-транзистора