- •1 Combination Circuits

- •1.1 Circuitry ttl-elements with Shottky diodes

- •Levels of Integration

- •Typical Set of ttl iCs

- •Transistor-transistor logic (ttl)

- •1.2 Element with the open collector Open-collector outputs

- •Tristate outputs

- •1.3 Emitter-coupled logic (ecl)

- •Emitter-coupled Schmitt trigger

- •Emitter-coupled multivibrator

- •1.4 Decoder

- •Priority decoder

- •Binary Decoders

- •Decoder Networks

- •1.5 Coder units Encoder Networks

- •Binary Encoders

- •Priority Encoders

- •1.6 Multiplexers (Selectors)

- •1.7 Multiplexer Trees

- •Demultiplexer Networks

- •Encoder Networks

- •1.8 Demultiplexers (Distributors)

- •1.9 Applicanion of multiplexer

- •1.10 Code converters

- •1.11 Shifters

- •Shifter Networks

- •Barrel Shifter

- •1.12 Comparators

- •Window comparator

- •Digital comparators

- •2 Sequentional Circuits

- •2.1 Circuritry of flips

- •Sequential logic systems

- •Integrated flip-flops

- •Transparent flip-flops

- •Clocked rs flip-flop

- •Clocked d flip-flop

- •Flip-flops with intermediate storage

- •2.2 Flips types Single-edge-triggered flip-flops

- •2.3 Statik registers

- •2.4 Shift register Combinatorial shift register (barrel shifter)

- •Shift Registers

- •2.5 Counters

- •Asynchronous straight binary counter

- •Counters

- •Ripple Counters

- •Asynchronous bcd counter

- •2.6 Synchronous reversal counters

- •Synchronous straight binary counters

- •Synchronous bcd counter

- •Synchronous one-shot

- •Synchronous edge detector

- •Synchronous clock switch

- •2.7 Schmitt flip-flops Schmitt trigger

- •Inverting Schmitt trigger

- •Precision Schmitt trigger

- •3 Memory Devices

- •3.1 Circuitri of memori element Semiconductor memories

- •3.2 Mask-type lic of the rom

- •RaMs as shift registers

- •First-In-First-Out Memories (fifOs)

- •Fifo implementation using standard raMs

- •Error detection and correction

- •Parity bit

- •Hamming code

- •3.3 Rom with singl programming Read-only memories (roMs)

- •Mask-programmed roMs (mroMs)

- •Programmable roMs (proMs)

- •3.4 Memori element with electrical erase Electrically erasable proMs (eeproMs)

- •3.5 Static ram

- •Timing considerations

- •3.6 Dynamic raMs

- •Dynamic ram controllers

- •3.7 Devices programmed

- •Programmable logic array (pal)

1.9 Applicanion of multiplexer

A gate-network implementation of a 4-input multiplexer is illustrated in Figure 1.47.a. The corresponding pass-transistor network is shown in Figure 1.47.b.

Fig.1.47 - A 4-input multiplexer implementation (a) with gates and (b) with pass transistor.

1.10 Code converters

A simple method of binary-to-BCD conversion consists of having a straight binary counter and a decimal counter operating in parallel. If the two counters are started at zero and then stopped when the binary number to be converted is reached, the corresponding BCD number will be available at the output of the decimal counter. The disadvantage of this method is that up to 2N counting steps have to be executed in order to convert an N-digit binary number. The method described below, on the other hand, requires only N computing steps.

For arithmetic operations in BCD code, results may arise containing the decimal "digits" 10dec. to 15dec. Such unintended digits are called pseudo-tetrads (pseudo combinations). To correct for them, they must be reduced by 10dec = 10102 and the next higher tetrad increased by 1. This correction can also be achieved by adding 6 = 01102 to the pseudo-tetrad, as shown by the following example:

|

Tens |

units |

|

|

tens |

units |

pseudo 13 : |

0000 |

1101 |

|

|

0000 |

1101 |

– 10 dec : |

0000 |

1010 |

|

+ 6 : |

0000 |

0110 |

+ 10 dec : |

0001 |

0000 |

|

|

|

|

correct 13 : |

0001 |

0011 |

|

|

0001 |

0011 |

The above example illustrates the rule for converting a 4-bit straight binary number to a BCD number.

Numbers up to and including 9 remain unchanged.

Numbers over 9 must undergo the pseudo-tetrad correction.

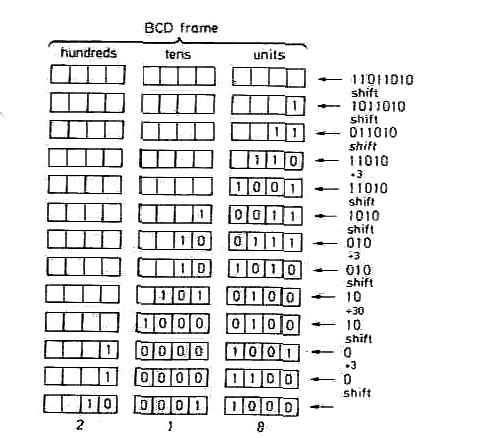

Binary numbers of more than 4 bits are treated accordingly: beginning with the most significant bit (MSB), the straight binary number is shifted from right to left into a BCD "frame", as shown in Fig. 1.48. If a 1 crosses the boundary between the units- and the tens-column, an error is incurred. This is because, for the straight binary number, the weighting changes due to the shift from 8 to 16, whereas for the BCD number it changes only from 8 to 10. After such a shift, the BCD number has become too small by 6. To allow for this, a 6 must be added whenever a 1 crosses the boundary. Similarly, a 6 must be added in the tens-column when a 1 is transferred to the hundreds-column. The resulting BCD number then has the correct value but may still contain pseudo-tetrads. To avoid this, any pseudo-tetrads that do occur are immediately corrected after every shift by adding 6 to the decade in question and carrying 1 to the next decade. Both corrections require the same arithmetic operation, that is the addition of 6.

Fig. 1.48. - Straight binary-to-BCD conversion; 218 dec as an example.

Instead of adding 6 after the shift, one can equally well add 3 beforehand, since it can be ascertained before the shift whether or not a correction will be necessary: if the value of a tetrad is smaller than or equal to 4 = 01002, the subsequent shift will result neither in a I crossing the column boundary nor in a pseudo-tetrad. The tetrad can therefore be shifted to the left unchanged. If the value of the tetrad before the shift is 5, 6 or 7, there again is no boundary crossing, as the most significant bit is zero. However, the pseudo-tetrads ten, twelve, fourteen, or eleven, thirteen, fifteen may arise depending on whether the next bit entering the frame is 0 or 1. In these cases a pseudo-tetrad correction is necessary, i.e. 3 must be added before the shift.

If the value of the tetrad before the shift is 8 or 9, the "boundary crossing of the 1 must be corrected, giving the correct tetrads six or seven, or eight or nine, after the shift. Because of the immediate pseudo-tetrad correction, values higher than nine cannot arise. All possibilities are now taken care of, and we obtain the correction table in Fig. 1.49.

The conversion of a straight binary to the corresponding BCD number can be implemented by left shifting the straight binary into a shift register divided into 4-bit blocks (decades). A correction circuit is connected to each decade, which alters the contents of the register according to the truth table in Fig. 1.49. before the next shift is carried out.

Instead of a solution involving sequential logic circuits, combinatorial logic circuitry can be employed if the shift operation is performed by appropriate wiring. This possibility is shown in Fig. 1.50. Rather than shifting the number from right to left, the BCD frame may be shifted from left to right and each tetrad corrected according to the table in Fig.1.49. In order to be able to hard-wire the frame shift, an individual correction

Fig. 1.49 - Correction system for the straight binary-to-BCD conversion.

Fig. 1.50 - Straight binary-to-BCD conversion using correction networks.

The values shown refer to the example of 218 decnetwork is necessary for each decade and each shifting "step". The total circuit may be simplified by omitting a correction network whenever fewer than 3 bits are applied at the input, as in this case a correction is definitely not required. Figure 1.50 shows the combinatorial logic circuit for the conversion of an 8-bit binary number, where the omitted elements are drawn with dashed lines. The circuit can be extended to deal with larger numbers by expanding its characteristic pattern. The numbers in the diagram apply to the example of Fig. 1.48 and illustrate the conversion procedure.

The correction network is available as a manufacturer-programmed, 256-byte ROM (SN 74 S 485). Five networks are combined to form a block, as in Fig. 1.51. As comparison with Fig. 1.50 shows, an 8-digit binary number can be converted using two ICs. A 16-digit binary number requires eight ICs.

Fig. 1.51 - Functional diagram of binary-to-BCD converter SN74S4RS.

Conversion of BCD to straight binary code

In many cases the BCD code can be generated directly in a simple way, e.g. using BCD counters. As will be discussed later, many arithmetic operations can also be performed in BCD code, but sometimes conversion to straight binary numbers is necessary. This can be achieved by a repeated division by 2. To begin with, the binary coded decimal number is divided by 2, and if it is an odd number, a remainder of 1 is obtained, i.e. the 20-bit has the value 1. The quotient is again divided by 2. If the remainder is 0, the 21-bit is 0, and if the remainder is 1, the 21-bit has the value 1. The more significant bits of the straight binary number are obtained accordingly.

The division of a BCD number by 2 can be

carried out simply by shifting it one place to the right, since the

individual decades are already straight-binary coded. In each

case, the remainder is the bit which has been "pushed out"

of the BCD frame. If, during shifting, a 1 crosses the boundary

between two columns, an error is incurred: when crossing from the

tens to the units, the bit weighting of the shifted 1 must be halved

from 10 to 5. However, for a straight binary number, the assigned

weighting would be 8 so that, for a correction, 3 must be subtracted.

Therefore the following correction rule applies: If the MSB of a

column (decade) after shifting is 1, a subtraction of 3 is required

in this particular decade. The truth table of the

correction network in Fig. 1.52

can

The division of a BCD number by 2 can be

carried out simply by shifting it one place to the right, since the

individual decades are already straight-binary coded. In each

case, the remainder is the bit which has been "pushed out"

of the BCD frame. If, during shifting, a 1 crosses the boundary

between two columns, an error is incurred: when crossing from the

tens to the units, the bit weighting of the shifted 1 must be halved

from 10 to 5. However, for a straight binary number, the assigned

weighting would be 8 so that, for a correction, 3 must be subtracted.

Therefore the following correction rule applies: If the MSB of a

column (decade) after shifting is 1, a subtraction of 3 is required

in this particular decade. The truth table of the

correction network in Fig. 1.52

can

Fig, 1.52 - Correction system for SCD-to-straight binary conversion.

Fig. 1.53 - BCD-to-straight binary conversion by correction networks.

The

values entered refer to the example

of 218dec

thus be directly determined.

The conversion is complete when the BCD number has

been entirely "pushed out" of the frame. Figure

1.53 shows a combinatorial logic system

for the conversion of a

2![]() -digit

BCD number. In analogy to Fig.

1.10

shifting of the BCD frame is achieved by hard-wiring identical

correction networks. To

illustrate the basic structure,

all three correction networks required for each shift are shown. If

the MSB is not used, no correction

is necessary as can be seen in Fig.

1.52. and the correspondingcorrection

networks can be omitted. In Fig. 1.53, they are shown

by dashed lines.

-digit

BCD number. In analogy to Fig.

1.10

shifting of the BCD frame is achieved by hard-wiring identical

correction networks. To

illustrate the basic structure,

all three correction networks required for each shift are shown. If

the MSB is not used, no correction

is necessary as can be seen in Fig.

1.52. and the correspondingcorrection

networks can be omitted. In Fig. 1.53, they are shown

by dashed lines.

The correction networks are available as blocks of five in the form of manufacturer-programmed 256-byte ROM (SN 74 S 484). To convert two BCD decades, one 1C is required. Four BCD decades require five ICs.