- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

2.6. Центральный процессор

Внутреннее устройство тракта данных типичного Фон-неймановского МП иллюстрирует рис. 21. Тракт данных состоит из регистров (обычно от 1 до 32), арифметико-логического устройства (АЛУ) и нескольких соединительных шин. Содержимое регистров поступает во входные регистры АЛУ, которые чаще всего обозначены буквами А и В. В них находятся входные данные АЛУ, пока АЛУ производит вычисления.

Рис. 21. Тракт данных фон-неймановского микропроцессора

АЛУ выполняет сложение, вычитание и другие простые операции над входными данными и помещает результат в выходной регистр (аккумулятор). Содержимое этого выходного регистра может записываться обратно в один из регистров или сохранятся в памяти, если это необходимо.

Центральный процессор выполняет каждую команду за несколько шагов:

– вызывает следующую команду из памяти и переносит ее в регистр команд;

– меняет положение счетчика команд, который после этого указывает на следующую команду;

– определяет тип вызванной команды;

– если команда использует слово из памяти, определяет, где находится это слово;

– переносит слово, если это необходимо, в регистр центрального процессора;

– выполняет команду;

– переходит к шагу 1, чтобы начать выполнение следующей команды.

Такая последовательность шагов (выборка – декодирование – выполнение) является основой работы всех процессоров.

При использовании конвейера команда обрабатывается уже не за два, а за большее количество шагов, каждый из которых реализуется определенным аппаратным компонентом, причем все эти компоненты могут работать параллельно.

Для счета и указания следующей команды выполняемой программы используется программный счетчик. Реализация этой функции значительно осложняется, когда необходимо сохранить содержимое программного счетчика при вызове подпрограмм и обработке запросов прерывания или обеспечить ветвление программы. На рис. 22 показано функционирование программного счетчика в процессоре с Принстонской архитектурой.

Рис. 22. Программный счетчик

Программный счетчик представляет собой счетчик с параллельным вводом-выводом. В МП этого типа содержимое программного счетчика поступает по шине данных в схему управления памятью, указывая адрес считываемой команды. Часто программный счетчик входит в состав схемы управления памятью – это позволяет избежать, передачи адреса по внутренней шине данных. Важные особенности функционирования программного счетчика – параллельная загрузка нового содержимого, поступающего с шины данных, возможность сброса, реализация инкремента. Сигналы, обеспечивающие выполнение этих операций, формируются дешифратором команд, который управляет последовательностью действий МП.

2.7. Суперскалярный конвейер

Для организации вычислений в современных процессорах и контроллерах с целью ускорения выполнения инструкций (увеличения числа инструкций, выполняемых в единицу времени) используется конвейер.

Идея заключается в том, чтобы разделить обработку процессорных инструкций на последовательность независимых шагов, с сохранением результатов в конце каждого шага. Это позволяет управляющим цепям компьютера получать инструкции со скоростью самого медленного шага обработки.

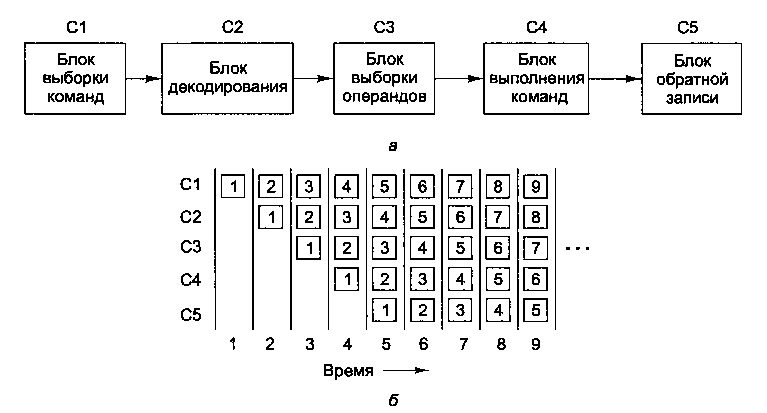

На рис. 23, а изображен конвейер из пяти блоков, которые называются ступенями. Первая ступень (блок С1) вызывает команду из памяти и помещает ее в буфер, где она хранится до тех пор, пока не потребуется. Вторая ступень (блок С2) декодирует эту команду, определяя ее тип и тип ее операндов. Третья ступень (блок СЗ) определяет местонахождение операндов и вызывает их из регистров или из памяти.

Рис. 23. Пятиступенчатый конвейер (а); состояние каждой ступени в зависимости от количества пройденных циклов (б). Показано 9 циклов

Четвертая ступень (блок С4) выполняет команду, обычно проводя операнды через тракт данных (рис. 23). И наконец, блок С5 записывает результат, обратно, в нужный регистр.

На рис. 23 б мы видим, как действует конвейер во времени. Во время цикла 1 блок С1 обрабатывает команду 1, вызывая ее из памяти. Во время цикла 2 блок С2 декодирует команду 1, в то время как блок С1 вызывает из памяти команду 2. Во время цикла 3 блок С3 вызывает операнды для команды 1, блок С2 декодирует команду 2, а блок С1 вызывает команду 3. Во время цикла 4 блок С4 выполняет команду 1, С3 вызывает операнды для команды 2, С2 декодирует команду 3, а С1 вызывает команду 4. Наконец, во время цикла 5 блок С5 записывает результат выполнения команды 1 обратно в регистр, тогда как другие ступени конвейера обрабатывают следующие команды.

Предположим, что время цикла у этой машины – 2 нс. Тогда для того, чтобы одна команда прошла через весь конвейер, требуется 10 нс. На первый взгляд может показаться, что такой компьютер будет выполнять 100 млн. команд в секунду, в действительности же скорость его работы гораздо выше. В течение каждого цикла (2 нс) завершается выполнение одной новой команды, поэтому машина выполняет не 100, а 500 млн. команд в секунду.

Конвейеры позволяют добиться компромисса между временем запаздывания (время выполнения одной команды) и пропускной способностью процессора (количество команд, выполняемых процессором в секунду). Если время обращения составляет Т нс, а конвейер имеет n ступеней, время запаздывания составит n*Т нс.

Поскольку одна команда выполняется за одно обращение, а за одну секунду таких обращений набирается 109/Т, количество команд в секунду также составляет 109/Т. Скажем, если Т = 2 нс, то каждую секунду выполняется 500 млн. команд. Для того чтобы получить значение MIPS, нужно разделить скорость выполнения команд на 1 миллион; таким образом, (109/Т)/106 = 1000/Т MIPS. В принципе, скорость выполнения команд можно измерять и в миллиардах операций в секунду (Billion Instructions Per Second, BIPS), но так никто не делает, и мы не будем.

При использовании конвейера процессор приобретает следующие достоинства:

- время цикла процессора уменьшается, таким образом, увеличивая скорость обработки инструкций;

- некоторые комбинационные логические элементы, такие как сумматоры или умножители могут быть ускорены путем увеличения количества логических элементов.

На основе вышеизложенного можно отметить достоинства беcконвейерного процессора в сравнении с конвейерным:

- процессор исполняет только одну инструкцию за раз. Это предотвращает задержки веток инструкций, и возникают проблемы, связанные с последовательными инструкциями, которые исполняются параллельно;

- задержка инструкций в беcконвейерном процессоре слегка ниже, чем в конвейерном эквиваленте. Это происходит из-за того, что в конвейерный процессор должны быть добавлены дополнительные триггеры.

- у беcконвейерного процессора скорость обработки инструкций стабильна. Производительность конвейерного процессора предсказать намного сложнее, и она может значительно различаться в разных программах.

Один конвейер – хорошо, а два – еще лучше. Одна из возможных схем микропроцессора с двумя конвейерами показана на рис. 20.

Рис. 20. Сдвоенный пятиступенчатый конвейер с

общим блоком выборки команд

Здесь общий блок выборки команд вызывает из памяти сразу по две команды и помещает каждую из них в один из конвейеров. Каждый конвейер содержит АЛУ для параллельных операций. Чтобы выполнять параллельно две команды ни одна из них не должна зависеть от результата выполнения другой.

Основная идея – один конвейер с большим количеством функциональных блоков, как показано на рис. 21. В 1987 году для обозначения этого подхода был введен термин суперскалярная архитектура.

Со временем значение понятия «суперскалярный» несколько изменилось. Теперь суперскалярными называют процессоры, способные запускать несколько команд за один тактовый цикл. Для того чтобы передавать все эти команды, в суперскалярном процессоре должно быть несколько функциональных блоков.

Рис. 21. Суперскалярный процессор с пятью функциональными блоками

Мультискалярные процессоры обеспечивают параллельную обработку информации. Здесь программа разбивается на части с помощью аппаратных и программных средств. В состав мультискалярного процессора входят много процессоров, каждый из которых работает параллельно.