- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

12.5. Старшее подсемейство picMicro

Старшие модели микроконтроллеров PICMicro используют 16-битные команды и могут адресовать 64 Кбайта памяти. Так как каждое слово содержит 16 бит, го старшие модели серии 17Схх могут фактически адресовать по 128 Кбайт памяти программ и памяти данных.

Для обеспечения чтения/записи памяти программ в серии 17Схх используется модифицированное ядро центрального процессора. Это ядро позволяет различным командам обращаться ко всем регистрам процессора (в младших и средних моделях нельзя использовать любой регистр в качестве аккумулятора, что возможно в серии 17Схх). Это повышает гибкость микроконтроллера и позволяет использовать команды в широком спектре приложений. В то время как в микроконтроллерах среднего уровня используется только один вектор прерывания, в старших моделях PICMicro имеется несколько векторов прерываний.

Старшие модели PICMicro разрабатывались, в основном, для взаимодействия с другими цифровыми устройствами, По этой причине в микроконтроллерах серии 17С4х нет АЦП и устройств, обеспечивающих непосредственное подключение датчиков, которые имеются в моделях среднего уровня.

Обозначение |

Характеристики |

PIC 16F87X |

Среднее подсемейство. Корпуса с 28/40 выводами, 14-разрядное процессорное ядро, 10-разрядный АЦП (5-8_каналов), два таймера (TMR1 и TMR2), варианты с интерфейсами USART, I2C, SPI и PSP |

PIC 16С92х |

Среднее подсемейство. Корпуса с 64 выводами, 14-разрядное процессорное ядро. Варианты с 8-разрядным АЦП, TMR1 и TMR2, ЖКИ контроллером |

PIC 17С4х |

Старшее подсемейство. Корпуса с 40 выводами, 16-разрядное процессорное ядро, аппаратный умножитель, USART |

PIC 17С5х |

Старшее подсемейство. Корпус с 68 выводами, 16-разрядное процессорное ядро, аппаратный умножитель, 10-разрядный АЦП, варианты с интерфейсами USART и I2C |

PIC17C6X |

Старшее подсемейство. Корпус с 84 выводами, 16-разрядное процессорное ядро, аппаратный умножитель, 12-разрядный АЦП, USART, I2C и SPI |

PIC 18Сххх |

Старшее подсемейство. Корпуса с 28/40 выводами, 16-разрядное усовершенствованное процессорное ядро, 10-разрядный АЦП, варианты с интерфейсами USART, I2C и SPI |

12.6 Архитектура микроконтроллеров старшего подсемейства

Это подсемейство имеет целый ряд особенностей по сравнению с другими подсемействами PIC-микроконтроллеров, в частности:

- возможность работы с внешним запоминающим устройством (внешней памятью);

- использование до семи портов ввода/вывода данных;

- встроенный блок умножения 8-разрядных чисел;

- большая оперативная память, которая содержит до 902 регистров, соответствующих 16 различным банкам;

- большой объем программной памяти (до 64 Кб);

- возможность записи в программное запоминающее устройство и считывания из него;

- наличие нескольких векторов прерывания.

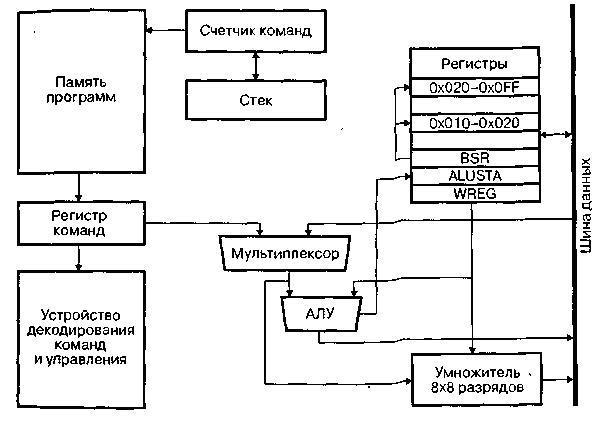

Структурная схема процессора, который применяется в микроконтроллерах старшего семейства, показана на рис. 42.

Существенные отличия архитектуры этого процессора от процессоров, используемых в микроконтроллерах младшего и среднего подсемейств, состоят в следующем:

- обращения к регистру-аккумулятору WREG (иначе-рабочему регистру) может осуществляться через адресное пространство регистров;

- функции регистров STATUS и OPTION распределяются между несколькими регистрами;

- счетчик программ здесь функционирует несколько иначе, чем в других вышеупомянутых архитектурах;

- доступ, к регистрам может обеспечиваться и без обращения к регистру WREG.

Рис. 42 Архитектура процессора старшего подсемейства

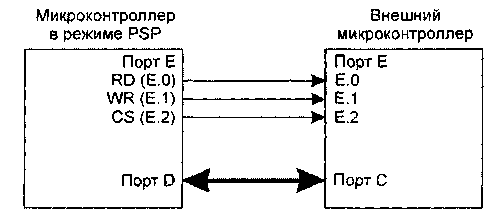

В микроконтроллерах PIC серии 18Сх порт D может работать в режиме управляемого параллельного порта PSP (Parallel Slave Port). Это означает, что он действует как регистр, который может быть подключен к шине другого микроконтроллера, обмениваясь с ним данными. В режиме PSP, как и в случае обмена данными с любым периферийным устройством, используются сигналы RD (чтение), WR (запись) и CS (выбор кристалла) – разряды 0-2 порта Е (рис. 43).

Рис. 43. Пример подключения внешнего микроконтроллера PIC в режиме PSP