- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

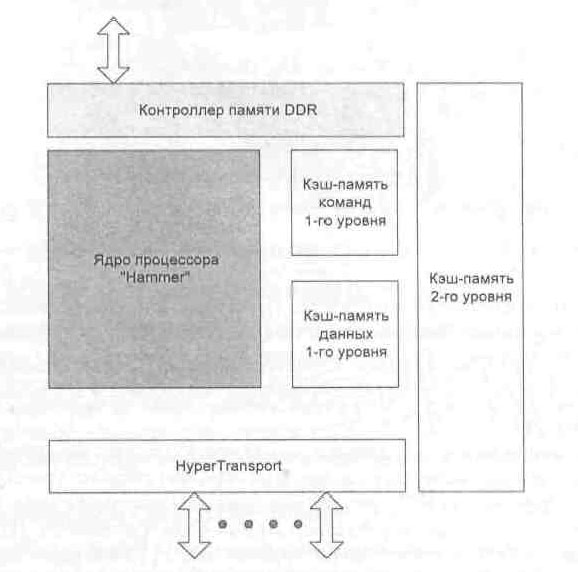

5.2. Микропроцессоры семейства Hammer

Микропроцессоры данного семейства являются 64-разрядными, однако в отличие от архитектуры IA-64 Intel, обеспечивают совместимость с системой команд х86, в связи с чем архитектура получила название х86-64.

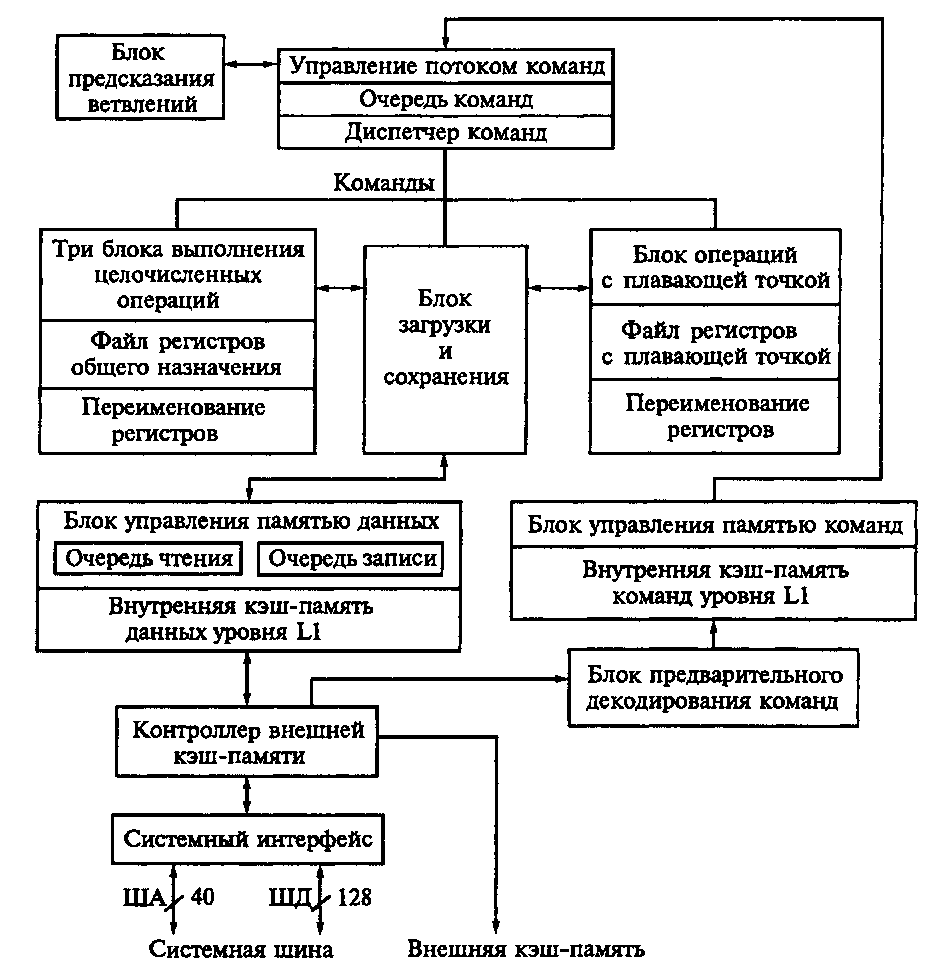

Упрощенная структура микропроцессора Hammer показана на рис. 30.

Основные преимущества архитектуры x86-64 следующие: обратная совместимость с инструкциями х86; 64-битные версии регистров общего назначения; 8 новых РОН (general purpose registers, GPRs), доступных только для 64-битных приложений; поддержка SSE и SSE2, добавлено 8 новых регистров SSE2; увеличен объем адресуемой памяти; высокая производительность 32-битных приложений, поддержка 64-битных приложений, увеличена длина вычислительных конвейеров: целочисленного конвейера до 12 стадий, с плавающей точкой до 17 стадий; встроен контроллер памяти; усовершенствован блок предсказания ветвлений; встроен когерентный интерфейс.

Рис. 30.Упрощенная структура микропроцессора Hammer

Встроенный когерентный интерфейс обеспечивает возможность использования Hammer в мультипроцессорной конфигурации.

Улучшение блока предсказания ветвлений заключается в выявлении и учете информации о типе ветвлений: статическое ветвление, т. е. адрес перехода не изменяется, или динамическое.

Микропроцессоры c архитектурой power pc и arm

6.1. Микропроцессоры с архитектурой power

Архитектура POWER во многих отношениях представляет собой традиционную RISC-архитектуру. Она придерживается наиболее важных отличительных особенностей RISC: фиксированной длины команд, архитектуры регистр-регистр, простых способов адресации, простых (не требующих интерпретации) команд, большого регистрового файла и трехоперандного (неразрушительного) формата команд. Однако архитектура POWER имеет также несколько дополнительных свойств, которые отличают ее от других RISC-архитектур.

Во-первых, набор команд был основан на идее суперскалярной обработки. В базовой архитектуре команды распределяются по трем независимым исполнительным устройствам: устройству переходов, устройству с фиксированной точкой и устройству с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, где они могут выполняться одновременно и заканчиваться не в порядке поступления.

Во-вторых, архитектура POWER расширена несколькими "смешанными" командами для сокращения времен выполнения. Возможно единственным недостатком технологии RISC по сравнению с CISC, является то, что иногда она использует большее количество команд для выполнения одного и того же задания. Было обнаружено, что во многих случаях увеличения размера кода можно избежать путем небольшого расширения набора команд, которое вовсе не означает возврат к сложным командам, подобным командам CISC. Это было сделано с помощью косвенной адресации посредством таблицы содержания, которая модифицируется во время загрузки.

Архитектура POWER обеспечивает также несколько других способов сокращения времени выполнения команд такие как: обширный набор команд для манипуляции битовыми полями, смешанные команды умножения-сложения с плавающей точкой, установку регистра условий в качестве побочного эффекта нормального выполнения команды и команды загрузки и записи строк.

Третьим фактором, который отличает архитектуру POWER от многих других RISC-архитектур, является отсутствие механизма "задержанных переходов". Обычно этот механизм обеспечивает выполнение команды, следующей за командой условного перехода, перед выполнением самого перехода. В архитектуре переходов POWER была организована поддержка методики "предварительного просмотра условных переходов" и методики "свертывания переходов".

Архитектура POWER вместо того, чтобы исправлять проблемы, связанные с традиционным подходом к регистру условий, предлагает наличие специального бита в коде операции каждой команды, что делает модификацию регистра условий дополнительной возможностью и тем самым восстанавливает способность компилятора реорганизовать код. Так же предлагается несколько (восемь) регистров условий для того, чтобы обойти проблему единственного ресурса и обеспечить большее число имен регистра условий так, что бы компилятор мог разместить и распределить ресурсы регистра условий, как он это делает для универсальных регистров.

6.2. Микропроцессоры с архитектурой PowerPC

В однокристальных микропроцессоры семейства PowerPC сохранены свойства архитектуры микропроцессоров POWER и усовершенствован процесс параллельного выполнения команд. Семейство представлено несколькими процессорами: микропроцессоры PowerPC 601, PowerPC 603, PowerPC 604, PowerPC 620, PowerPC 750, PowerPC G4, PowerPC G5 и некоторыми другими. Младшие модели суперскалярных процессоров семейства (PowerPC 601, PowerPC 603, PowerPC 604) являются 32-разрядными, а старшие модели (PowerPC 620) – 64-разрядными. Микропроцессор PowerPC содержат в своем составе несколько исполнительных блоков: блок целочисленных вычислений, блок операций с плавающей точкой и блок обработки переходов. Все блоки конвейеризированы. Микропроцессоры PowerPC допускают внеочередное исполнение команд и обеспечивают одновременную выдачу на исполнение до четырех команд. В каждом такте работы микропроцессоров PowerPC 601 и PowerPC 603 могут завершать исполнение до трех команд, а процессор PowerPC 604 – до шести команд.

Суперскалярный процессор PowerPC 620 стал первой 64-разрядной реализацией архитектуры PowerPC. Он предназначен для построения высокопроизводительных ВМ, серверов и мультипроцессорных систем. Микропроцессор PowerPC 620 совместим по коду с ранними моделями процессоров PowerPC. Благодаря этому он может выполнять не только новые, специально разработанные для него 64-битовые программы, но и ранее созданные 32-битовые программы микропроцессоров PowerPC.

Структурная схема суперскалярного процессора PowerPC 620 представлен рис. 31, которая содержит шесть независимых исполнительных блоков, высокоскоростной интерфейс, раздельные кэш команд и кэш данных 1-го уровня емкостью 32 Кбайт каждый, контроллер внешней кэш-памяти. За такт процессор может выполнять до четырех команд. Для поддержания эффективной загрузки исполнительных блоков в процессоре применяется динамическое предсказание переходов и спекулятивное исполнение команд.