- •Введение

- •Список сокращений

- •1. Архитектура современных микропроцессоров

- •1.1. Термины и определения

- •1.2. Микропроцессорные системы управления

- •1.3. Архитектурные особенности микропроцессоров

- •1.3.1. Гарвардская и принстонская архитектура

- •1.3.2. Архитектура системы команд (cisc и risc)

- •1.4. Корпус микропроцессоров

- •1.5. Технология изготовления кристаллов

- •1.6. Общие положения об обозначении импортных цифровых микросхем

- •1.6.1. Система обозначений микросхем производства Atmel

- •2. Структура микропроцессорной системы

- •2.1. Модуль питания

- •2.2. Модуль сброса и синхронизации

- •2.2.1. Сторожевой таймер

- •2.2.2. Тактирование системы

- •2.3. Модуль памяти

- •2.3.1. Супервизор напряжения

- •2.3.2. Память микропроцессорного устройства

- •2.4. Контроллер прерываний

- •2.5. Терминал

- •2.6. Центральный процессор

- •2.7. Суперскалярный конвейер

- •3. Программирование микропроцессорных устройств

- •3.1. Основные этапы проектирования и отладки программного обеспечения

- •3.2. Языки высокого уровня

- •3.3. Язык Ассемблера

- •3.3.1. Способы адресации на языке ассемблера

- •3.4. Алгоритм выполнения команды

- •3.5. Типы данных микропроцессора

- •4. Микропроцессоры с архитектурой х86

- •4.1. Микропроцессор Pentium

- •4.2. Микропроцессор Pentium 4

- •4.3. Микропроцессоры компании amd

- •4.4. Микропроцессор к7

- •5. Микропроцессоры с архитектурой x64

- •5.1.Микропроцессор Itanium ia-64

- •Отличия архитектур процессоров х86 и ia-64

- •5.2. Микропроцессоры семейства Hammer

- •Микропроцессоры c архитектурой power pc и arm

- •6.1. Микропроцессоры с архитектурой power

- •Процессоры arm

- •6.2. Микропроцессоры с архитектурой arm

- •4. Микроконтроллеры семейства mcs-51

- •4.1. Структура микроконтроллеров семейства mcs-51

- •4.2 Способы адресации и система команд микроконтроллеров семейства mcs-51

- •4.3. Функции выводов

- •5. Микроконтроллеры семейства Motorola

- •5.1. Общая структура микроконтроллеров семейства 68нс05/705/08

- •4.2.2. Регистровая модель микроконтроллеров семейства 68нс05/705/08

- •4.2.3. Способы адресации и система команд микроконтроллеров семейства 68нс05/705/08

- •6. Микроконтроллеры avr компании Atmel

- •5.1. Архитектура микроконтроллеров avr

- •5.2. Процессор микроконтроллера avr

- •5.3. Запоминающее устройство FlashRom

- •5.4. Периферийные устройства

- •Микроконтроллеры семейства piCmicro

- •12.1. Младшие подсемейства picMicro

- •Основные характеристики микроконтроллеров младшего подсемейства

- •12.2. Архитектура микроконтроллеров младшего подсемейства

- •Стандартный набор операций алу микроконтроллеров PlCmicro

- •12.3. Среднее подсемейство picMicro

- •12.5. Старшее подсемейство picMicro

- •12.6 Архитектура микроконтроллеров старшего подсемейства

- •Ввод-вывод данных микропроцессорной системы

- •6.1 Аналоговый ввод/вывод микропроцессорной системы

- •6.2. Таймеры микропроцессорной системы

- •6.3. Параллельный ввод-вывод данных

- •6.2.2. Асинхронный последовательный обмен

- •6.2.3 Синхронный последовательный обмен

- •6.3. Микроконтроллерная сеть

- •6.3.1 Протокол i2c

- •6.3.2. Протокол can

- •Характеристика протокола can

- •Выбор скорости передачи данных исходя из расстояния

- •6.3.3. Протокол rs-485 и rs-422

- •Стандартные параметры интерфейсов rs-422 и rs-485

- •Лекция 7 Микропроцессорные системы управления

- •7.1. Подключение светодиодов

- •7.2. Подключение 7-сегментных светодиодных индикаторов

- •7.3. Ввод с матричной клавиатуры

- •7.4. Управление жидкокристаллическим индикатором

- •7.5. Управление соленоидом и реле

- •7.6. Управление электродвигателем

- •6.5.1. Управление шаговым двигателем

- •7.6. Управление мощной нагрузкой

- •Лекция 8 Цифровая обработка сигналов

- •8.1. Типовые задачи решаемые цос

- •8.2. Способы реализации алгоритмов цос

- •8.3. Структура процессора цифровой обработки сигналов

- •8.4. Пцос с фиксированной и плавающей точкой

- •8.5. Гибридные процессоры

- •Библиографический список

- •Фирмы-производители 8-, 16- и 32-разрядных микроконтроллеров

- •Высокопроизводительные 8-разрядные risc микроконтроллеры семейства avr

- •1.6.2. Система обозначений микросхем производства

- •1.6.3. Система обозначений микросхем производства Motorola

- •1.6.4. Система обозначений микросхем производства

4.2. Микропроцессор Pentium 4

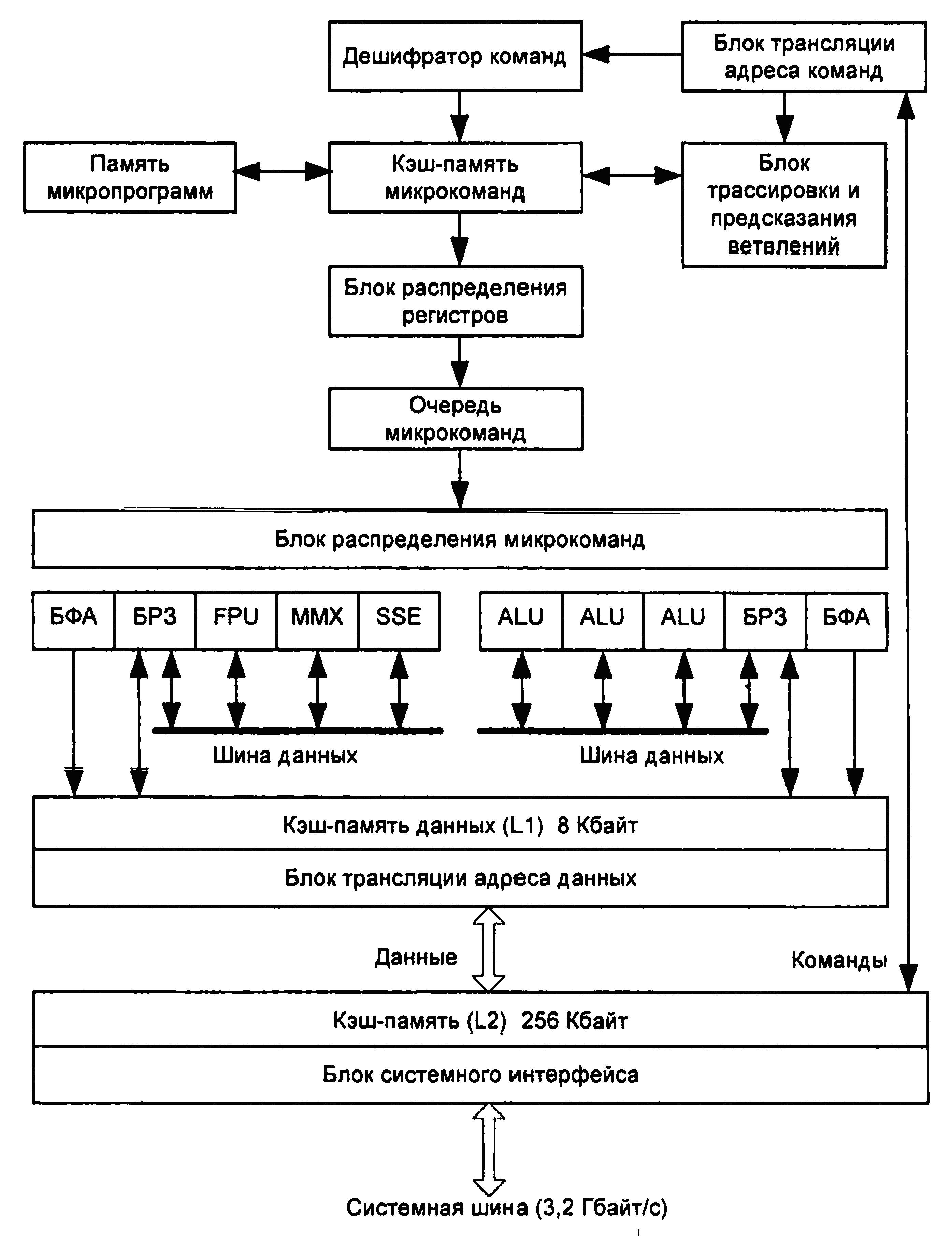

Микропроцессор Pentium 4, выпущенный Intel в июне 2000 года, с одной стороны, являет собой продолжение линии микропроцессоров с архитектурой х86. Микропроцессор содержит 42 млн. транзисторов и производится по технологии КМОП 0,18 мкм (ядро Willamette) для тактовых частот от 1,4 до 1,7 ГГц и 0,13 мкм (ядро Northwood) с 6-слойной металлизацией для тактовых частот от 2 до 3,06 ГГц. Структура микропроцессора показана на рис. 26.

Рис. 26. Структура микропроцессора Pentium 4

Как и в других микропроцессорах шестого поколения, в Pentium 4 реализованы: гарвардская архитектура внутренней памяти с разделением потоков команд и данных; суперскалярная архитектура, обеспечивающая одновременное выполнение нескольких команд в параллельно работающих исполнительных устройствах; динамическое изменение последовательности команд; конвейерное исполнение команд; предсказание переходов.

К основным нововведениями архитектуры Pentium 4 можно отнести: работу с системной шиной, имеющей эффективную частоту 400 МГц; удвоение частоты работы блоков АЛУ микропроцессора; значительное увеличение длины исполнительного конвейера; использование кэш трассы команд в качестве кэш-памяти команд первого уровня; размещение кэш-памяти второго уровня на кристалле.

Раздельные потоки команд и данных поступают от системной шины через блок системного интерфейса и размещенную на кристалле процессора 8-входовую множественно-ассоциативную общую кэш-память второго уровня с обратной записью. Блок системного интерфейса реализует обмен процессора с системной шиной, включающей 64-разрядную двунаправленную шину данных и 41-разрядную шину адреса. Процессор может адресовать до 64 Гбайт внешней памяти.

Четырехкратная передача данных по шине за такт при частоте тактирования 100 МГц обеспечивает эффективную частоту работы шины 400 МГц и скорость передачи данных 3,2 Гбайт/с.

Дешифратор команд, совместно с памятью микропрограмм, осуществляет преобразование х86-команды в последовательность микрокоманд, помещаемых в кэш-память микрокоманд. Порядок размещения команд в этой памяти емкостью 12 000 микрокоманд соответствует последовательности их выполнения, с учетом предсказанных переходов.

Блок распределения регистров выполняет назначение каждому из логических регистров микрокоманд одного из 128 физических регистров, входящих в состав блоков регистров замещения (БРЗ).

Адреса выбираемых из памяти операндов вычисляются блоком формирования адреса данных (БФА), который реализует интерфейс с кэш-памятью данных первого уровня.

БФА формирует 48 адресов для загрузки операндов из памяти в регистр БРЗ и 24 адреса для записи из регистра в память для команд, еще не выбранных на выполнение. При обращении к памяти БФА выдает сразу два адреса: один для загрузки операнда в заданный регистр БРЗ, второй – для пересылки результата из БРЗ в память.

Суперскалярное ядро микропроцессора содержит конвейеризированные исполнительные блоки: ALU, FPU, ММХ. Причем целочисленные АЛУ работают на удвоенной частоте ядра процессора.

В Pentium 4 используется гиперконвейерная технология выполнения команд – число ступеней конвейера достигает 20. Благодаря разбиению цикла выполнения каждой команды на более мелкие этапы, каждый из которых может выполняться быстрее.

Блок SSE (Streaming SIMD Extensions – потоковое SIMD-расширение процессора, где SIMD (single instruction, multiple data – одиночный поток команд, множественный поток данных) – принцип компьютерных вычислений) позволяющий обеспечить параллелизм на уровне данных, реализует 144 новые команды, обеспечивающих одновременное выполнение операций над несколькими операндами, которые располагаются в памяти. В регистрах могут храниться и одновременно обрабатываться 2 числа в формате с плавающей точкой двойной точности (64 разряда) или 4 числа в формате одинарной точности (32 разряда).