- •1. 5 Поколений схемотехники эвм и их влияние на параметры эвм.

- •2. Классификация интегральных микросхем

- •3. Параметры и характеристики им

- •13. Триггер Шмидта. Методика синтеза. Комбинационные схемы

- •4. Классификация триггерных устройств

- •12. Динамические триггеры.

- •14. Назначение, классификация, функции и операции выполняемые регистрами.

- •15. Регистры приема и выдачи кода. Парафазная передача кода.

- •16. Регистры, выполняющие логические операции «и» и «или».

- •17. Регистр, выполняющий логическую операцию по модулю 2.

- •18. Регистры сдвига. Методика синтеза синхронных регистров сдвига.

- •19. Преобразование кодов с помощью rg.

- •20. Демультиплексоры

- •21. Мультиплексоры

- •22. Классификация, основные параметры дешифраторов. Линейные дешифратор.

- •23. Пирамидальный дешифратор. Шифраторы.

- •24. Многоступенчатый дешифратор. На примере 2-х ступенчатого.

- •25. Назначение и классификация счетчиков. Основные параметры счетчиков. Уго.

- •26. Асинхронные суммирующие счетчики.

- •27. Асинхронные вычитающие счетчики.

- •28. Счетчики с произвольным коэффициентом пересчета. Методы обнуления и дешифрации.

- •29. Счетчики с произвольным коэффициентом пересчета. Метод ос.

- •30. Синхронные счетчики. Счетчики с цепью группового переноса.

- •31. Схемотехника счетчиков с цепями переноса.

- •32 Ттл с нагрузочным транзистором

- •33 Ттл с нагрузочным резистором

- •34. Ттлш (транзистор Шоттки)

- •35. Эмиттерно-связная логика (эсл)

- •36. Интегрально-инжекционная логика.

- •37. Моп логика.

- •38. Кмоп логика.

- •39. Монтажная логика.

- •47. Зу с последовательной выборкой. Стек.

- •40. Тристабильный элемент.

- •41. Зу, иерархия, основные параметры

- •42. Классификация зу.

- •54. Перепрограммируемое пзу.

- •55. Ассоциативное Запоминающее устройство.

- •56. Программируемая логическая матрица.

- •57. Специализированные большие интегральные схемы (классификация методов проектирования сбис).

- •58. Особенности конструкций бмк.

- •59. Основные параметры и характеристики бмк. Основные направления бмк. Развитие бмк.

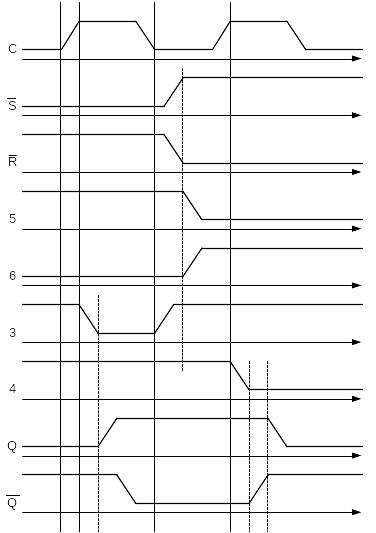

12. Динамические триггеры.

Синхронный триггер с динамическим управлением

1.С=0 Входная информация инвертируется эл. 5 и 6

2. Синхро с 0 на 1. Элементы 5 и 3 или 6 и 4 образуют вспомогательный триггер, который запирает 4 и 5 (если 0 на выходе 3) или 3 и 6 (если 0 на выходе 4).

3. Сигнал 0 вспмогательный триггер переключает RS-триггер на элементах 1 и 2.

4. Синхро = 0. Элемент 3 и 4 закрыв., элементы 5 и 6 инвертируют вход. инф-ию.

14. Назначение, классификация, функции и операции выполняемые регистрами.

Регистр - упорядоченная последовательность триггеров, предназначенная для хранения слов и выполнения микроопераций над ними. Микрооперация - элементарное машинное действие, в результате которого изменяется значение слова или осуществляется его пересылка.

Различают синхронные и асинхронные регистры. В синхронных регистрах микрооперации выполняются по тактирующему сигналу Т. Настройка регистра на соответствующую микрооперацию осуществляется предварительной установкой на управляющих входах кода микрооперации S1, S2, …Sm. Число разрядов в коде определяется из соотношения, m ≥ log2k

где k - количество микроопераций. В асинхронных регистрах тактирующий вход Т отсутствует. Каждая i-я микрооперация выполняется под действием собственного управляющего сигнала yi. Количество таких сигналов равно числу микроопераций k, т. е. в общем случае больше, чем разрядов в коде микрооперации S1, S2, …Sm синхронного регистра. Наиболее часто на регистрах выполняют микрооперации занесения (приема, записи) слова параллельным кодом, сдвига слова, а также установки исходного (обычно нулевого) состояния. Занесение слова осуществляется через информационные входы Di (i=1,…,n). Для i-го разряда регистра можно записать Qn+1=Dn, т. е. при выполнении этой микрооперации в i-й разряд регистра записывается значение сигнала на входе Di.

Регистры,

на которых выполняются микрооперации

сдвига, называются сдвиговыми. Сдвиг

слова может быть осуществлен влево (в

сторону старших разрядов) или вправо

(в сторону младших разрядов) на i разрядов

одновременно, где i=1,…,n-1. Регистры,

имеющие цепи как левого, так и правого

сдвига, называются реверсивными. Сдвиг

слова влево и вправо, например, на один

разряд можно описать соответственно

как

![]() и

и

![]() .

С помощью регистров можно выполнять и

другие преобразования информации,

например, поразрядные логические

операции: конъюнкция (

.

С помощью регистров можно выполнять и

другие преобразования информации,

например, поразрядные логические

операции: конъюнкция (![]() );

дизъюнкция (

);

дизъюнкция (![]() );

неравнозначность (

);

неравнозначность (![]() );

инвертирование разрядов (

);

инвертирование разрядов (![]() )

и т. д.

)

и т. д.

15. Регистры приема и выдачи кода. Парафазная передача кода.

Наиболее

часто на регистрах выполняют микрооперации

занесения (приема, записи) слова

параллельным кодом, сдвига слова, а

также установки исходного (обычно

нулевого) состояния. Занесение слова

осуществляется через информационные

входы Di (i=1,…,n). Для i-го разряда регистра

можно записать

![]() =

=![]() ,

т. е. при выполнении этой микрооперации

в i-й разряд регистра записывается

значение сигнала на входе Di. Выходами

регистра бывают непосредственно выходы

триггеров, но в ряде случаев КС (рис. 1)

включает элементы, которые осуществляют

выдачу информации. Выдача слова может

быть осуществлена в прямом коде, и

обратном коде или в парафазном коде.

Кроме того, регистр может иметь выходы

с тремя состояниями (состояние логического

нуля, логической единицы и высокоомное

состояние).

,

т. е. при выполнении этой микрооперации

в i-й разряд регистра записывается

значение сигнала на входе Di. Выходами

регистра бывают непосредственно выходы

триггеров, но в ряде случаев КС (рис. 1)

включает элементы, которые осуществляют

выдачу информации. Выдача слова может

быть осуществлена в прямом коде, и

обратном коде или в парафазном коде.

Кроме того, регистр может иметь выходы

с тремя состояниями (состояние логического

нуля, логической единицы и высокоомное

состояние).

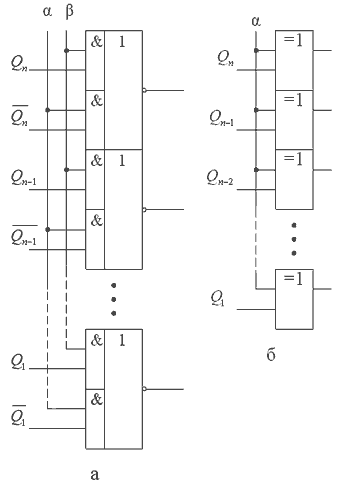

Для выдачи слова в прямом коде к выходам регистра подключают прямые выходы триггеров Qi; в обратном коде - инверсные выходы !Qi , а в парафазном коде - прямые и инверсные.

В качестве примера на рис., а показана организация цепей выдачи прямого и обратного кода на элементах И-ИЛИ-НЕ. Для выдачи прямого кода подается управляющий сигнал α, а для выдачи обратного -β. Если α=β=0 , то на всех выходах регистра будут присутствовать единицы. Цепи выдачи прямого и обратного кода можно реализовать и на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ (рис б). В этом случае при α=0 из регистра выдаются значения Qi, при α=1 - значения !Qi, a запрет выдачи информации не обеспечивается.