- •1. 5 Поколений схемотехники эвм и их влияние на параметры эвм.

- •2. Классификация интегральных микросхем

- •3. Параметры и характеристики им

- •13. Триггер Шмидта. Методика синтеза. Комбинационные схемы

- •4. Классификация триггерных устройств

- •12. Динамические триггеры.

- •14. Назначение, классификация, функции и операции выполняемые регистрами.

- •15. Регистры приема и выдачи кода. Парафазная передача кода.

- •16. Регистры, выполняющие логические операции «и» и «или».

- •17. Регистр, выполняющий логическую операцию по модулю 2.

- •18. Регистры сдвига. Методика синтеза синхронных регистров сдвига.

- •19. Преобразование кодов с помощью rg.

- •20. Демультиплексоры

- •21. Мультиплексоры

- •22. Классификация, основные параметры дешифраторов. Линейные дешифратор.

- •23. Пирамидальный дешифратор. Шифраторы.

- •24. Многоступенчатый дешифратор. На примере 2-х ступенчатого.

- •25. Назначение и классификация счетчиков. Основные параметры счетчиков. Уго.

- •26. Асинхронные суммирующие счетчики.

- •27. Асинхронные вычитающие счетчики.

- •28. Счетчики с произвольным коэффициентом пересчета. Методы обнуления и дешифрации.

- •29. Счетчики с произвольным коэффициентом пересчета. Метод ос.

- •30. Синхронные счетчики. Счетчики с цепью группового переноса.

- •31. Схемотехника счетчиков с цепями переноса.

- •32 Ттл с нагрузочным транзистором

- •33 Ттл с нагрузочным резистором

- •34. Ттлш (транзистор Шоттки)

- •35. Эмиттерно-связная логика (эсл)

- •36. Интегрально-инжекционная логика.

- •37. Моп логика.

- •38. Кмоп логика.

- •39. Монтажная логика.

- •47. Зу с последовательной выборкой. Стек.

- •40. Тристабильный элемент.

- •41. Зу, иерархия, основные параметры

- •42. Классификация зу.

- •54. Перепрограммируемое пзу.

- •55. Ассоциативное Запоминающее устройство.

- •56. Программируемая логическая матрица.

- •57. Специализированные большие интегральные схемы (классификация методов проектирования сбис).

- •58. Особенности конструкций бмк.

- •59. Основные параметры и характеристики бмк. Основные направления бмк. Развитие бмк.

54. Перепрограммируемое пзу.

2 стр-ры:

1) запись с пом. эл. сигн.

2) запись и стирание с пом. эл. сигн.

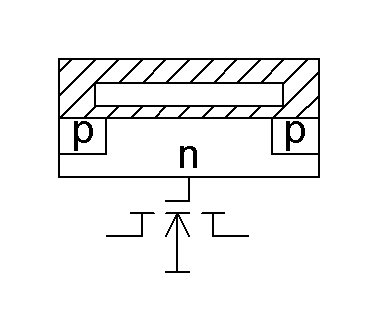

1)

|

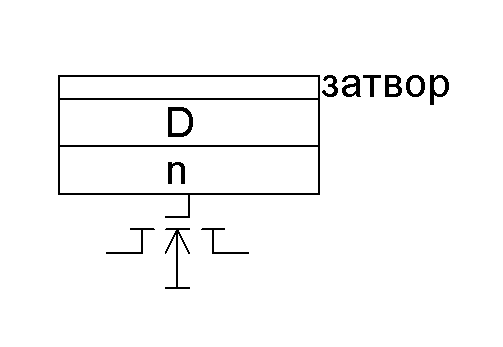

2) Тр-р сделан на основе эффекта Фаулера-Нордтейма

|

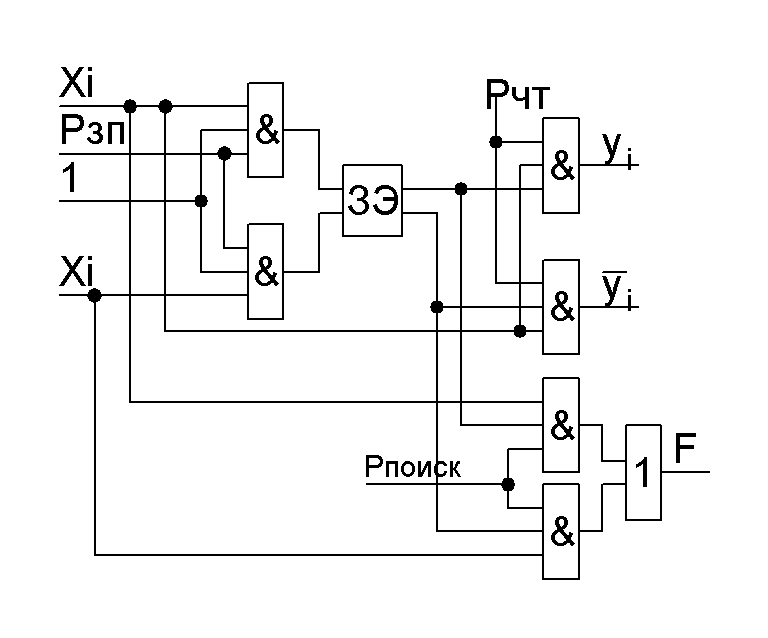

55. Ассоциативное Запоминающее устройство.

ЗУ в к-ых произв-ся поиск инф-ии не по адресу, а по признакам самост. инф-ии или по др. критериям, связанным с этой инф-ией наз. АЗУ.

Критерии поиска

- на рав-во

- наибол. по знач-ю число

- наим. числа, находящиеся в задан. Пределах

|

|

эл-т сложения по модулю 2

Методы ассоциатив. поиска

простые: пар-но по словам, посл-но по разрядам, полностью пар-но

сложные: упоряд. поиск идет по некот. алгоритму

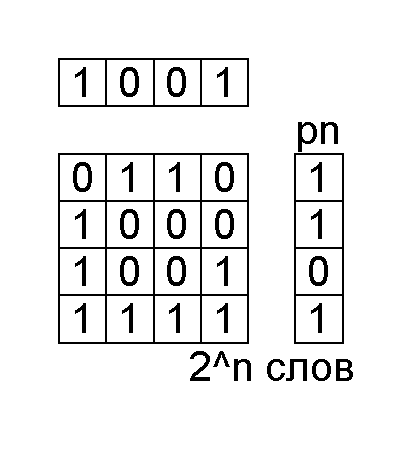

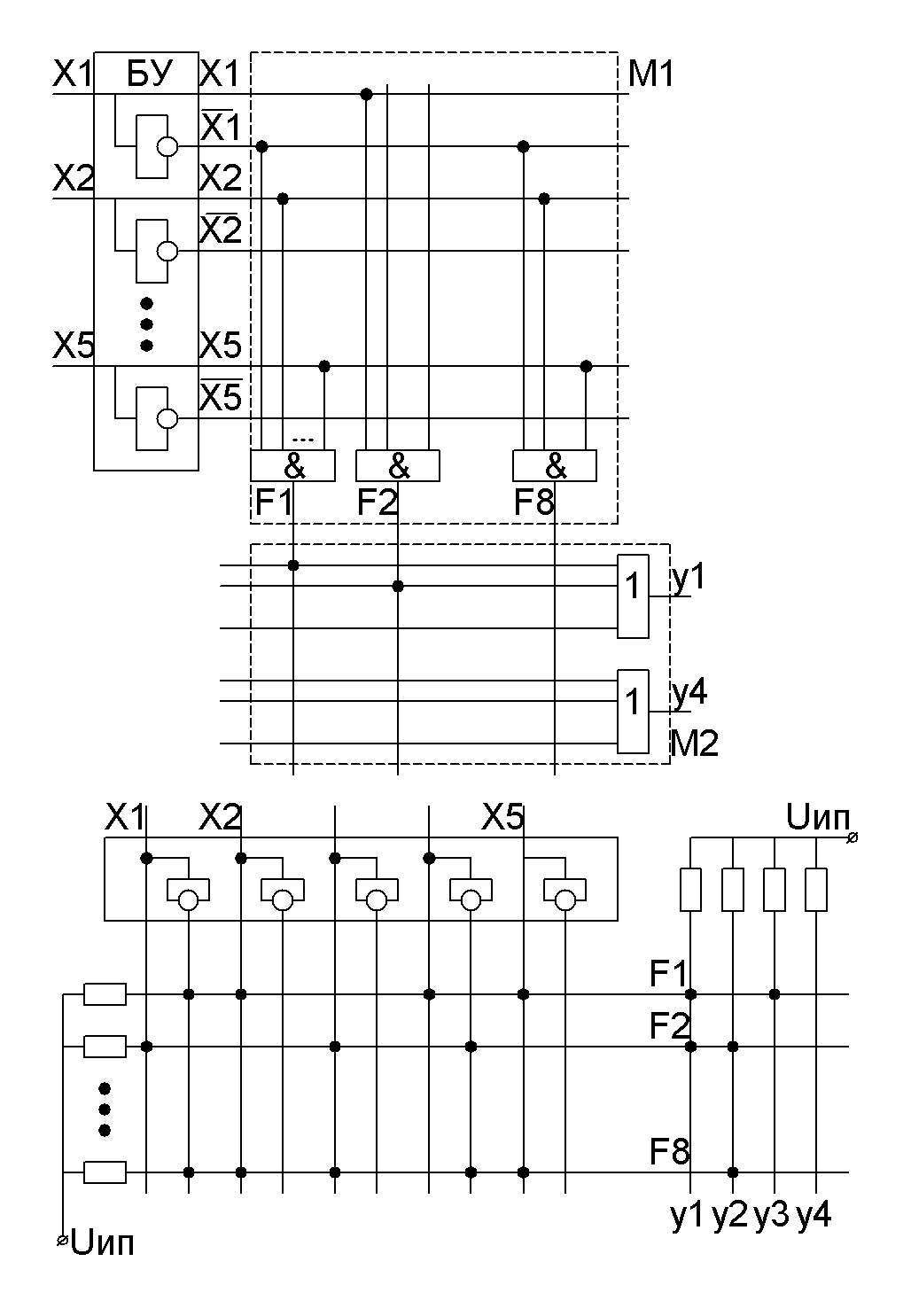

56. Программируемая логическая матрица.

ПЛМ - комб. схема, к-ую м. прогр-ть под себя: реализует схему булевых ф-ций, представленных в МДНФ

Пять входных, четыре выходных сигнала:

x1 |

x2 |

x3 |

x4 |

x5 |

F |

y1 |

y2 |

y3 |

y4 |

0 |

1 |

X |

1 |

1 |

F1 |

1 |

0 |

1 |

0 |

1 |

X |

1 |

0 |

X |

F2 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

F3 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

X |

X |

F4 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

F5 |

0 |

0 |

0 |

1 |

X |

0 |

0 |

1 |

0 |

F6 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

F7 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

F8 |

0 |

1 |

0 |

0 |

y4=F5+F6+F7=![]()

М1 содержит j эл-ов «И» n-входовых, М2 содержит m-выходовых j-входовых «1» эл-ов.

ПЛМ программируется также: в процессе изготовления, однократно по заявке заказчика и многократно (с возможностью перезаписи информации).

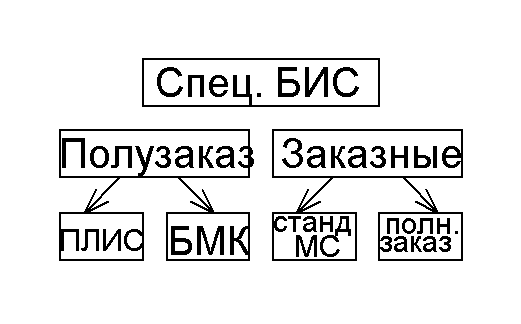

57. Специализированные большие интегральные схемы (классификация методов проектирования сбис).

Технология очень дорогая. Они имеют постоянную структуру на 50%. На самом последнем этапе, все делается под заказчика. Создание СБИС зависит от мастера.

58. Особенности конструкций бмк.

БМК - Базовый Матричный Кристалл. Базовый – т.к. все элементы, за искл. слоев коммутации, явл пост и не зависят от реализуемой схемы. Матричный – т.к. простейшие эл-ты расположены на кристалле в узлах прямоугольной решетки.

Конструкция:

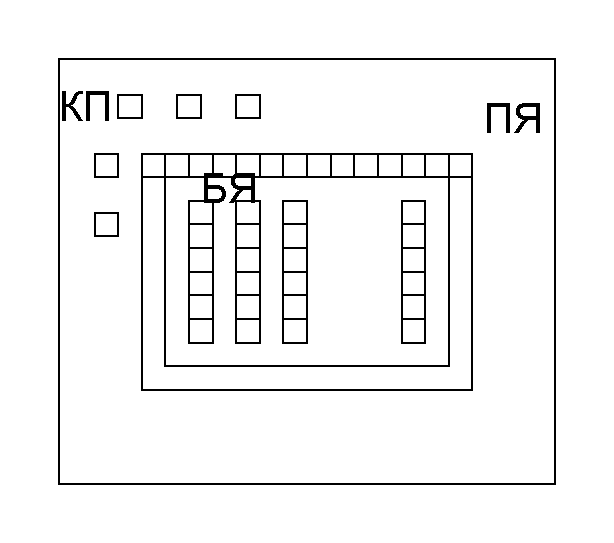

1. канальная структура: где м/у столбцами каналы для трассировки, ПЯ- периферийная ячейка, БЯ- базовая ячейка, КП – контактная площадка. Основной недостаток – 50-60% на каналы

2. бесканальная структура – плотноупакованная. Улучшено быстродействие, задержка на кристалле становится меньше.

3. с функционально-законченными эл-ми - явл компромиссом м/у канальной и бесканальной структурой, выделяется место для функциональных (постоянных эл-ов).