- •1. 5 Поколений схемотехники эвм и их влияние на параметры эвм.

- •2. Классификация интегральных микросхем

- •3. Параметры и характеристики им

- •13. Триггер Шмидта. Методика синтеза. Комбинационные схемы

- •4. Классификация триггерных устройств

- •12. Динамические триггеры.

- •14. Назначение, классификация, функции и операции выполняемые регистрами.

- •15. Регистры приема и выдачи кода. Парафазная передача кода.

- •16. Регистры, выполняющие логические операции «и» и «или».

- •17. Регистр, выполняющий логическую операцию по модулю 2.

- •18. Регистры сдвига. Методика синтеза синхронных регистров сдвига.

- •19. Преобразование кодов с помощью rg.

- •20. Демультиплексоры

- •21. Мультиплексоры

- •22. Классификация, основные параметры дешифраторов. Линейные дешифратор.

- •23. Пирамидальный дешифратор. Шифраторы.

- •24. Многоступенчатый дешифратор. На примере 2-х ступенчатого.

- •25. Назначение и классификация счетчиков. Основные параметры счетчиков. Уго.

- •26. Асинхронные суммирующие счетчики.

- •27. Асинхронные вычитающие счетчики.

- •28. Счетчики с произвольным коэффициентом пересчета. Методы обнуления и дешифрации.

- •29. Счетчики с произвольным коэффициентом пересчета. Метод ос.

- •30. Синхронные счетчики. Счетчики с цепью группового переноса.

- •31. Схемотехника счетчиков с цепями переноса.

- •32 Ттл с нагрузочным транзистором

- •33 Ттл с нагрузочным резистором

- •34. Ттлш (транзистор Шоттки)

- •35. Эмиттерно-связная логика (эсл)

- •36. Интегрально-инжекционная логика.

- •37. Моп логика.

- •38. Кмоп логика.

- •39. Монтажная логика.

- •47. Зу с последовательной выборкой. Стек.

- •40. Тристабильный элемент.

- •41. Зу, иерархия, основные параметры

- •42. Классификация зу.

- •54. Перепрограммируемое пзу.

- •55. Ассоциативное Запоминающее устройство.

- •56. Программируемая логическая матрица.

- •57. Специализированные большие интегральные схемы (классификация методов проектирования сбис).

- •58. Особенности конструкций бмк.

- •59. Основные параметры и характеристики бмк. Основные направления бмк. Развитие бмк.

1. 5 Поколений схемотехники эвм и их влияние на параметры эвм.

I поколение. Первая релейная машина 1944 год, США – «Марк1» (РВМ). Время сложения – 0,3 с, умножения – 5,7 с. Недостаток – низкая надежность реле.1947 год – «Марк2». Операция «+» - 0,125с, «*» - 0,25с.1956 год – РВМ1, первая в СССР релейная машина. Время «+» - 0,02с, «*» - 0,05с.1942-1946 года – США – разработана первая ЭВМ – ЭНИАК. Состояла из 18 тыс. ламп, 1.5 тыс. реле, мощность 180 кВт, время «+» - 0,2мс, «*» - 2,8мс. Джордж Фон Нейман – двоичная система счисления, которая хранилась в памяти.1949 год – Англия – «+» - 70 мкс, «*» - 5,8мс.1951 год – Лебедев – малая электронная счетная машина. 1952 – Большая счетная машина, 1000 операций в секунду. 1953 – Базелевский – «стрела». 1954 – Америк – «Урал». 1958 – «М20» - Брук – 2000 операций в секунду. Запоминающее устройство (ЗУ) выполняется на магнитных барабанах электронно-лучевых трубок (ЭЛТ) (память). Быстродействие 1мс, ρ=1эл*10см3. Решали узко специфические задачи. II поколение. 1955 год – Полупроводниковые приборы (п/п). 55-65 годы – на основе п/п элементов, техническая база – печатный монтаж. На магнитных сердечниках. Понизилась величина рабочего тока, снизилась потребляемая мощность, операция «+» - 1 мкс, ρ увеличилась в 6-8 раз, она стала равна 2-3эл/см3. III поколение Интегральные микросхемы – снижается масса, габариты, стоимость, повышается быстродействие.1972 год – ЕС 1010, ЕС 1012, ЕС 1018 … .с 65 по 70 года быстродействие 10 нс, ρ=10-12эл/см3.1970-1980 – БИС – ρ=1000эл/см3, быстродействие 1нс. Технологическая база – многослойный печатный монтаж. Память – на миниатюрных магнитных сердечниках, построение – на п/п элементах. IV поколение. С 1980 года СБИС. Ρ=1000000эл/см3. СССР – «Эльбрус» - быстродействие – 800 млн операций в секунду. Объем хранимой инфы – 1014 символов. ЗУ на ИС и п/п. Диалоговый режим работы с машиной.

V поколение. Создания и разработка эл-ов и схем на новых физ принципов в твердом теле. (свет). СБИС – специализированные БИС. Распараллеливание структур.

2. Классификация интегральных микросхем

1.по функциональному назначению:

- логические элементы – изменяют входной электронный сигнал, а следовательно изменяется сигнал на выходе, они бывают конденационного f1(t)=f(x1(t), x2(t), … , xn(t)) и последовательностного f1(t)=f(x1(t), x2(t), … , xn(t), z(t-1)) типов.

- запоминающие – хранят информацию, бывают активные (есть «0» и «1» - свой электрический уровень) и пассивные (запись и считывание информации связано с изменением физического состояния).

- вспомогательные – служат для обеспечения электрического и временного согласования работы логических и запоминающих эл-ов (усилители, преобразователи сигналов, генераторы).

2. по типу связи м/у ИС:

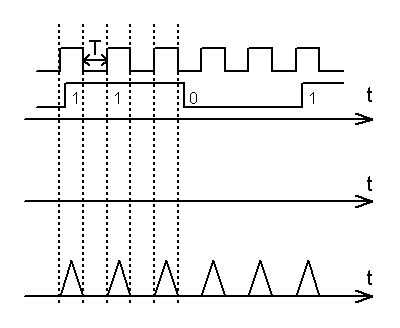

- потенциальные – лог «0» и «1» соответствует низкий и высокий уровни тока I и напряжения U. Сигнал остается неизменным, не менее одного периода синхроимпульса. ИС связаны м/у собой с помощью резисторов, диодов и транзисторов.

- импульсные – «1» равна синфазный импульс синхроимпульса.

- импульсно-потенциальные.

3. по физическому принципу работы. Эл-ты м.б. ламповые, п/п, магнитные, оптические, креагенные

4. по способу питания. Бывают со статическим и динамическим питанием.

5. по конструктивному оформлению и технологическому изготовлению

- дискретные – элементы самостоятельны.

- интегральные – функциональный узел.

Пленочные, монолитные, гибридные ИС.

Коэффициент степени интеграции: KИС=[lg(N+1)].