- •Тема 27. Використання мікросхем цап і ацп

- •27.1. Загальні поняття.

- •27.2. Застосування цап

- •Малюнок 27.4. Зменшення розрядності цап.

- •Малюнок 27.6. Генератор пилкоподібного аналогового сигналу

- •Малюнок 27.9. Аттенюатор аналогового сигналу на цап

- •27.3. Використання ацп

- •Малюнок 27.14. Компаратор напруги.

- •Малюнок 27.16. 3-розрядний ацп паралельного типу.

- •Малюнок 27.21. Включення буферної пам'яті для запам'ятовування кодів з виходів ацп.

Малюнок 27.16. 3-розрядний ацп паралельного типу.

Громіздкість структури паралельного АЦП призводить до того, що в деяких АЦП застосовується змішаний паралельно-послідовний принцип. Це дещо знижує швидкодію подібного АЦП в порівнянні із звичайним паралельним АЦП, та зате дозволяє одержати велике число розрядів, не збільшуючи кількість компараторів до 2п-1. Для того, щоб АЦП будь-якого типу працював з використанням всіх своїх можливостей, необхідно забезпечити узгодження діапазону зміни вхідного аналогового сигналу з допустимим діапазоном (динамічним діапазоном) вхідної напруги АЦП.

Малюнок

27.17. Співвідношення вхідного сигналу і

динамічного діапазону АЦП.

Малюнок

27.17. Співвідношення вхідного сигналу і

динамічного діапазону АЦП.

На малюнку 27.17 показано чотири можливі випадки співвідношення динамічного діапазону АЦП (від 0 до Uref або від Uref1 до Uref2) і вхідного сигналу. У випадках а і б вхідний сигнал менше динамічного діапазону, тому АЦП працюватиме правильно, але не використовуватиме всіх своїх можливостей. У випадку в вхідний сигнал дуже великий, тому частина його значень не буде перетворена. Тільки у разі г АЦП дійсно працювати як n-розрядний і перетворюватиме всі значення вхідного сигналу. Для узгодження вхідного сигналу з динамічним діапазоном АЦП можна застосовувати підсилювачі, аттенюатори, схеми зсуву. В деяких випадках узгодження може бути досягнуте простим вибором величин опорних напруг. Іноді необхідно зменшити кількість розрядів АЦП. В цьому випадку потрібна кількість молодших розрядів вихідного коду мікросхеми просто не використовується. На малюнку 27.18 показано використовування 10-розрядного АЦП як 8-розрядного.

Малюнок

27.18. Зменшення кількості розрядів

вихідного коду АЦП.

Малюнок

27.18. Зменшення кількості розрядів

вихідного коду АЦП.

Зворотна задача - збільшення розрядності АЦП - зустрічається частіше. Існує ряд типових рішень схемотехнік по об'єднанню декількох мікросхем АЦП для збільшення кількості розрядів вихідного коду, але більшість цих рішень вимагає складних розрахунків результуючих погрішностей перетворення і вживання аналогових вузлів. Ми не будемо їх тут розглядати. Відзначимо тільки, що при виникненні задачі збільшення розрядності треба перш за все спробувати знайти мікросхему з потрібною кількістю розрядів і тільки потім розглядати можливості об'єднання декількох мікросхем АЦП. Розглянемо декілька типових схем включення АЦП, що використовуються в аналого-цифрових системах.

Малюнок

27.19. Фіксатор перевищення вхідним

сигналом встановленого порогу

Малюнок

27.19. Фіксатор перевищення вхідним

сигналом встановленого порогу

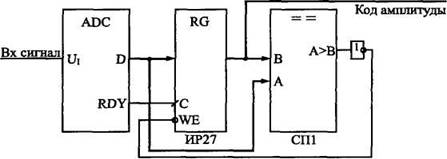

Перша схема (малюнок 27.19) призначена для фіксації моменту перевищення вхідним аналоговим сигналом заданої порогової напруги. Схема виробляє вихідний сигнал (позитивний фронт) тоді, коли вхідний аналоговий сигнал стає більше встановленого рівня, причому цей рівень задається цифровим кодом порогу. Код порогу порівнюється з вихідними кодами АЦП за допомогою мікросхеми компаратора кодів. Вихідний сигнал компаратора кодів записується в трігер по сигналу RDY з АЦП, що дозволяє виключити вплив коротких імпульсів, що виникають на виході компаратора у момент зміни вхідних кодів. Вживання цього трігера затримує вихідний сигнал на один такт. Може здатися, що вживання АЦП в даному випадку не виправдано, надмірно. Але треба враховувати, що в аналого-цифрових системах АЦП, перетворюючий вхідний сигнал в послідовність кодів, як правило, вже є, тому додаткового АЦП не потрібно, достатньо тільки включити компаратор кодів і трігер. АЦП також застосовується в схемах обчислення амплітуди вхідного аналогового сигналу Для такого обчислення можна використовувати вже розглянуту схему обчислювача екстремального значення вхідного коду. Як джерело послідовності вхідних кодів в даному випадку виступає АЦП (малюнок 27.20).

Малюнок

27.20. Обчислювач амплітуди аналогового

сигналу

Малюнок

27.20. Обчислювач амплітуди аналогового

сигналу

В регістр з входом дозволу запису записується код з виходу АЦП по сигналу RDY в тому випадку, якщо поточне значення коду більше значення коду, записаного раніше в регістр. В результаті вже після одного періоду вхідного сигналу в регістрі буде код амплітуди вхідного сигналу. За період перетворення АЦП повинні встигнути спрацювати компаратор кодів і регістр. Якщо такий обчислювач амплітуди вхідного сигналу використовується у складі складної аналого-цифрової системі, в якій вже присутній АЦП, безперервно перетворюючий вхідний сигнал в коди, то додатково потрібні тільки цифрові мікросхеми: компаратор кодів і регістр. Використовування АЦП, що часто зустрічається, - це перетворення вхідного сигналу в потік кодів, причому коди ці звичайно записуються в буферну пам'ять. В даному випадку самим відповідним є однонаправлений буфер з періодичним режимом роботи. Тобто спочатку в буферну пам'ять заноситься масив кодів вибірок вхідного сигналу, а потім цей масив читається для подальшої обробки Саме так наприклад, будується цифровий осцилограф, призначений для спостереження аналогових сигналів на екрані. Схема включення АЦП в цьому випадку показана на малюнку 27.21. Як строб запису в буферну пам'ять використовується сигнал RDY з АЦП. Докладніше організацію буфера ми вже розглядали в попередньому розділі. Звичайно, в реальних аналого-цифрових пристроях все набагато складніше, в них потрібні схеми синхронізації процесу запису з вхідним сигналом, схеми попередньої обробки аналогового сигналу, але суть залишається тією ж - буферна пам'ять, записуюча послідовність кодів з виходу АЦП. Чим більше об'єм пам'яті, тим більший фрагмент вхідного аналогового сигналу вона може запам'ятати. Наприклад, якщо пам'ять має організацію 64К X 8 і працює з 8-розрядним АЦП, то при частоті перетворення АЦП 10 Мгц буфер зможе берегти в собі фрагмент аналогового сигналу тривалістю 6,5536 мс. Нарешті, остання схема, яку ми розглянемо (малюнок 27.22), дозволяє удвічі підвищити швидкодію АЦП, точніше, підняти удвічі частоту запису кодів вибірок вхідного сигналу в буферну пам'ять.