- •Тема 27. Використання мікросхем цап і ацп

- •27.1. Загальні поняття.

- •27.2. Застосування цап

- •Малюнок 27.4. Зменшення розрядності цап.

- •Малюнок 27.6. Генератор пилкоподібного аналогового сигналу

- •Малюнок 27.9. Аттенюатор аналогового сигналу на цап

- •27.3. Використання ацп

- •Малюнок 27.14. Компаратор напруги.

- •Малюнок 27.16. 3-розрядний ацп паралельного типу.

- •Малюнок 27.21. Включення буферної пам'яті для запам'ятовування кодів з виходів ацп.

27.3. Використання ацп

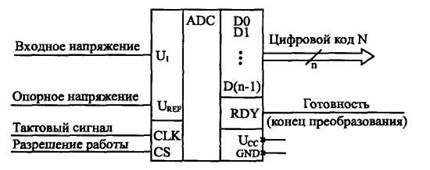

Мікросхеми АЦП виконують функцію, прямо протилежну функції ЦАП - перетворять вхідний аналоговий сигнал в послідовність цифрових кодів. В загальному випадку мікросхему АЦП можна представити у вигляді блоку, що має один аналоговий вхід, один або два входи для подачі опорної (зразкового) напруги, а також цифрові виходи для видачі коду, відповідного поточному значенню аналогового сигналу (малюнок 27.13).

Малюнок

27.13. Мікросхема АЦП.

Малюнок

27.13. Мікросхема АЦП.

Часто мікросхема АЦП має також входи для подачі тактового сигналу CLK, сигналу дозволу роботи CS і вихід для видачі сигналу RDY, вказуючого на готовність вихідного цифрового коду. На мікросхему подається одна або дві живлячі напруги. В цілому мікросхеми АЦП складніші, ніж мікросхеми ЦАП, їх різноманітність помітно більша, і тому сформулювати для них загальні принципи використання складніше. Опорна напруга АЦП задає діапазон вхідної напруги, в якій проводиться перетворення. Вона може бути постійною або ж допускати зміну в деяких межах. Іноді передбачається подача на АЦП двох опорних напруг з різними знаками, тоді АЦП здатний працювати як з позитивними, так і з негативними вхідними напругами. Вихідний цифровий код N (n-розрядний) однозначно відповідає рівню вхідної напруги. Код може приймати 2п значень, тобто АЦП може розрізняти 2п рівнів вхідної напруги. Кількість розрядів вихідного коду п є найважливішою характеристикою АЦП. У момент готовності вихідного коду видається сигнал закінчення перетворення RDY, по якому зовнішній пристрій може читати код N. Управляється робота АЦП тактовим сигналом CLK, який задає частоту перетворення, тобто частоту видачі вихідних кодів. Гранична тактова частота - другий найважливіший параметр АЦП. В деяких мікросхемах є вбудований генератор тактових сигналів, тому до їх виводів підключається кварцовий генератор або конденсатор, задаючий частоту перетворення. Сигнал CS дозволяє роботу мікросхеми. Випускається безліч найрізноманітніших мікросхем АЦП, що розрізняються швидкістю роботи (частота перетворення від сотень кілогерців до сотень мегагерц), розрядністю (від 6 до 24), допустимими діапазонами вхідного сигналу, величинами погрішностей, рівнями живлячих напруг, методами видачі вихідного коду (паралельний або послідовний), іншими параметрами. Звичайно мікросхеми з великою кількістю розрядів мають невисоку швидкодію, а самі швидкодійні мікросхеми мають невелике число розрядів. Область вживання будь-якої мікросхеми АЦП багато в чому визначається використаним в ній принципом перетворення, тому необхідно знати особливості цих принципів. Для вибору і використовування АЦП необхідно користуватися докладними довідковими даними від фірми-виробника.

Малюнок 27.14. Компаратор напруги.

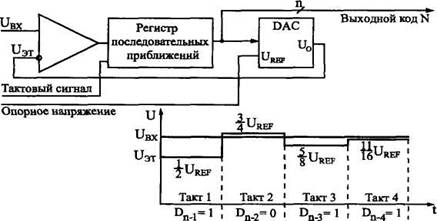

Як базовий елемент будь-кого АЦП використовується компаратор напруги (малюнок 27.14), який порівнює дві вхідні аналогові напруги і залежно від результату порівняння видає вихідний цифровий сигнал нуль або одиницю. Компаратор працює з великим діапазоном вхідних напруг і має високу швидкодію (затримка порядку одиниць наносекунд). Існує два основні принципи побудови АЦП: послідовний і паралельний. В послідовному АЦП вхідна напруга послідовно порівнюється одним єдиним компаратором з декількома еталонними рівнями напруги, і в залежності від результатів цього порівняння формується вихідний код. Найбільше поширення набули АЦП на основі так званого регістра послідовних наближень (малюнок 27.15).

Малюнок

27.15. АЦП послідовного типу.

Малюнок

27.15. АЦП послідовного типу.

Вхідна напруга подається на вхід компаратора, на інший вхід якого подається еталонна напруга, що східчасто змінюється в часі. Вихідний сигнал компаратора подається на вхід регістра послідовних наближень, тактованого зовнішнім тактовим сигналом. Вихідний код регістра послідовних наближень поступає на ЦАП, яке з опорної напруги формує змінну еталонну напругу. Регістр послідовних наближень працює так, що залежно від результату попереднього порівняння вибирається наступний рівень еталонної напруги по наступному алгоритму:

В першому такті вхідний сигнал порівнюється з половиною опорної напруги.

Якщо вхідний сигнал менше половини опорної напруги, то на наступному такті він порівнюється з четвертю опорної напруги (тобто половина опорної напруги зменшується на четверть). Одночасно в регістр послідовних наближень записується старший розряд вихідного коду, рівний нулю.

Якщо ж вхідний сигнал більше половини опорної напруги, то на другому такті він порівнюється з 3/4 опорної напруги (тобто половина збільшується на четверть). Одночасно в регістр послідовних наближень записується старший розряд вихідного коду, рівний одиниці.

Потім ця послідовність порівнянь повторюється потрібне число раз із зменшенням на кожному такті удвічі ступені зміни еталонної напруги (на третьому такті - 1/8 опорної напруги, на четвертому - 1/16 і т.д.). В результаті опорна напруга в кожному такті наближається до вхідної напруги. Всього перетворення займає п тактів. В останньому такті обчислюється молодший розряд

Зрозуміло, що цей процес досить повільний, вимагає декількох тактів, причому протягом кожного такту повинні встигнути спрацювати компаратор, регістр послідовних наближень і ЦАП з виходом по напрузі. Тому послідовні АЦП досить повільні, мають порівняно великий час перетворення і малу частоту перетворення. Другий тип АЦП, АЦП паралельного типу, працює за більш простим принципом. Всі розряди вихідного коду обчислюються в них одночасно (паралельно), тому вони набагато швидші, ніж послідовні АЦП. Правда, вони вимагають вживання великої кількості компараторів (2П - 1), що викликає чисто технологічні труднощі при великій кількості розрядів (наприклад, при 12-розрядному АЦП потрібні 4095 компараторів). Схема такого АЦП (малюнок 27.16) включає резистивный дільник з 2П однакових резисторів, який ділить опорну напругу на (2П- 1) рівнів. Вхідна напруга порівнюється за допомогою компараторів з рівнями, формованими дільником напруги. Вихідні сигнали компараторів за допомогою шифратора перетворяться в n-розрядний двійковий код. Шифратор видає на вихід номер останнього з компараторів, що спрацювали (тобто тих що видали сигнал логічної одиниці). Наприклад, у разі 3-розрядного АЦП (на малюнку) при величині вхідної напруги від 0 до 1/8 опорної напруги вихідний код буде 000, при вхідній напрузі від 1/8 до 2/8 опорної напруги спрацює перший компаратор, що дасть вихідний код 001, при вхідній напрузі від 2/8 до 3/8 опорної напруги спрацюють компаратори 1 і 2, що дасть вихідний код 010, і т.д. Процес перетворення відбувається в паралельному АЦП дуже швидко, тому частота перетворення може досягати сотень мегагерц. Для підвищення швидкодії в паралельному АЦП іноді застосовується конвейєрний принцип: вихідний код компараторів записується в (2П -1) -розрядний паралельний регістр, показаний на малюнку 27.16. Вихідний код шифратора також записується в n-разрядный паралельний регістр. Обидва регістри в цьому випадку тактуються одним і тим же тактовим сигналом. Це знижує вимоги до швидкодії компараторів і шифратора. Правда, вихідний код АЦП затримується через такі регістри на два періоди такої частоти.