- •Содержание

- •Введение

- •1.Описание применяемых элементов

- •1.1 Микропроцессор

- •1.2 Генератор тактовых импульсов (гти)

- •1.3 Системный контроллер кр580вк28(38)

- •1.4 Контроллер прерываний кр580вн59

- •1.5 Программируемый параллельный интерфейс кр580вв55

- •1.6 Программируемый последовательный интерфейс

- •1.7 Программируемый контроллер клавиатуры и дисплея кр580вв79

- •1.8 Программируемый интервальный таймер

- •1.11 Семисегментный индикатор

- •1.13 Дешифратор двоично – десятичного кода в семисегментный

- •2.1 Расчет архитектуры памяти. Расчет пзу и озу

- •2.2 Построение схем дешифрации адресов памяти

- •2.3 Построение схем дешифрации адресов устройств ввода-вывода

- •3. Структурная схема

- •3.1. Описание структурной схемы

- •4.Принципиальная схема.

- •4.1. Описание принципиальной схемы

- •Заключение

- •Список литературы

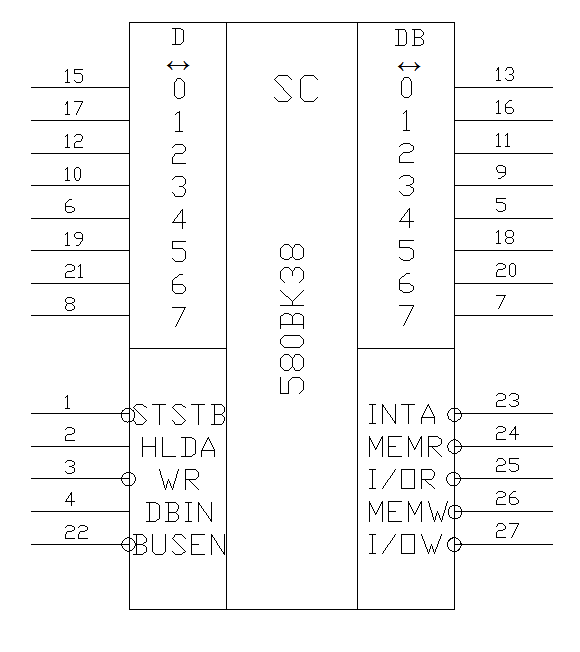

1.3 Системный контроллер кр580вк28(38)

Контроллер системной шины КР580ВК28(38) предназначен для фиксации слова состояния МП, выработки системных управляющих сигналов, буферизации шины данных МП и управления направлением передачи данных.

Рисунок 3. Условно – графическое изображение КР580ВК28

Таблица 3- Назначение выводов БИС КР580ВК28

Номер вывода |

Обозначение |

Назначение |

1 |

2 |

3 |

15,17,12,10,5,19,21,8 |

D0 - D7 |

информационные входы/выходы шинного формирователя |

13,16,11,9,5,18,20,7 |

DB0 - DB7 |

информационные входы/выходы шинного формирователя |

22 |

BUSEN |

если BUSEN=0, то информационные входы/выход переходят в третье состояние. |

26 |

WR |

входной сигнал “Запись” |

24 |

RD |

выходной сигнал “Чтение” |

2 |

HLDA |

входной сигнал “Подтверждение захвата шин” |

1 |

STB |

входной сигнал “Строб записи слова состояния” |

1 |

2 |

3 |

23 |

INTA |

выходной сигнал “Подтверждение прерывания” |

25 |

IORD |

выходной сигнал “Чтение УВВ” |

27 |

IOWR |

выходной сигнал “Запись в УВВ |

3 |

TR |

выдача информации |

4 |

RS |

прием информации. |

27 |

Ucc |

напряжение +5В. |

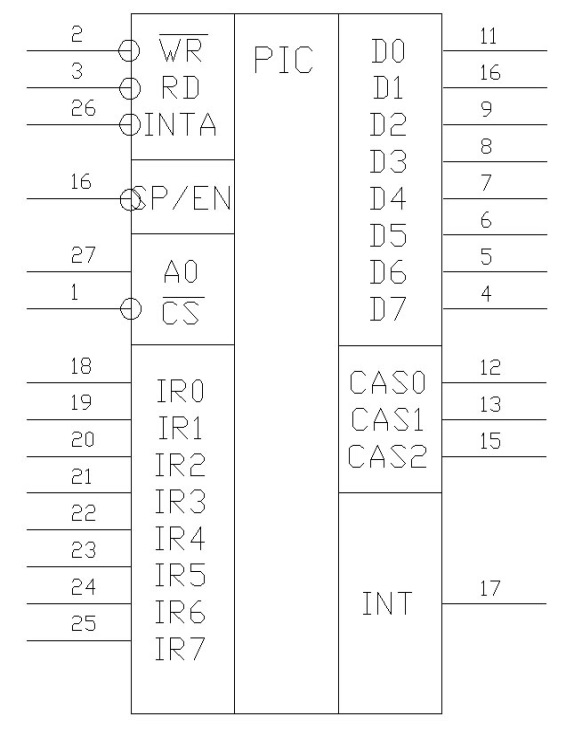

1.4 Контроллер прерываний кр580вн59

Микросхема КР580ВН59 - блок приоритетных прерываний (БПП), обслуживает до восьми запросов на прерывание микропроцессора, поступающих - от внешних устройств.

Микросхема позволяет сократить средства программного обеспечения и реальные затраты при выполнении прерываний в системах с приоритетами многих уровней. Алгоритм задания приоритета устанавливается программным путем.

В микросхеме предусмотрена возможность расширения числа обслуживаемых запросов до 64 путем каскадного соединения микросхем БПП.

Рисунок 4. Условное графическое обозначение КР580ВН59.

Таблица 4- Назначение вводов-выводов КР580ВН59

Номер вывода |

Обозначение |

Назначение |

1 |

2 |

3 |

1 |

CS |

Выбор микросхемы. |

2 |

WR |

Запись информации. |

3 |

RD |

Чтение информации. |

11-4 |

DB0-DB7 |

Канал данных магистрали МП. |

12,13,15 |

CAS0-CAS2 |

Шина каскадирования. |

14 |

GND |

Общий. |

16 |

SP |

Выбор ведомой микросхемы. |

Продолжение таблицы 4 |

||

1 |

2 |

3 |

17 |

INT |

Прерывание. |

18-25 |

IRQ0-IRQ7 |

Запрос прерывания. |

26 |

INTA |

Подтверждение прерывания от МП. |

27 |

A0 |

Адрес 0-го разряда. |

28 |

|

Напряжение питания +5В. |