- •Тема 9. Организация памяти вычислительных систем

- •1. Системы с общей и распределенной памятью

- •2. Многоуровневая организация общей памяти

- •3. Память с чередованием адресов

- •4. Симметричные (smp) многопроцессорные вс. Архитектура типа uma, coma, numa

- •5. Мультипроцессор Sun Enterprise 10000

- •Тема 10. Векторные и векторно-конвейерные вычислительные системы

- •1. Понятие вектора и размещение данных в памяти

- •2. Понятие векторного процессора

- •4. Структура векторного процессора

- •5. Структуры типа «память-память» и «регистр-регистр»

- •6. Обработка длинных векторов и матриц

- •Тема 11. Матричные вычислительные системы

- •1. Обобщенная модель матричной вс

- •2. Интерфейсная вм

- •3. Контроллер массива процессоров

- •4. Массив процессоров

- •5. Структура процессорного элемента

- •6. Подключение и отключение процессорных элементов

- •7. Сети взаимосвязей процессорных элементов

- •9. Ассоциативная память

- •10. Ассоциативные вс

- •11. Систолические структуры

- •Тема 12. Кластерные и mpp-системы

- •1. Понятие кластера. Преимущества и виды

- •2. Топологии кластеров

- •3. Примеры кластеров

- •4. Системы с массовым параллелизмом (mpp-системы)

- •Тема 13. Информационные технологии конечного пользователя

- •1. Общая классификация информационных технологий

- •2. Автоматизированное рабочее место – средство автоматизации работы конечного пользователя

- •3. Характеристика информационных технологий в экономике

- •3.1. Информационная технология поддержки принятия решений

- •3.2. Информационная технология экспертных систем

- •3.3. Информационные технологии управления

- •3.4. Автоматизация офиса

- •3.5. Аудио- и видеоконференции в автоматизации офиса

- •3.6. Технологии баз данных

- •Контрольные вопросы

10. Ассоциативные вс

Ассоциативный процессор (АП) – это ассоциативная память, допускающая параллельную запись во все ячейки, для которых было зафиксировано совпадение с ассоциативным признаком. Эта особенность АП, носящая название мультизаписи, является первым отличием ассоциативного процессора от традиционной ассоциативной памяти. Считывание и запись информации могут производиться по двум срезам запоминающего массива — либо это все разряды одного слова, либо один и тот же разряд всех слов. При необходимости выделения отдельных разрядов среза лишние позиции допустимо маскировать. Каждый разряд среза в АП снабжен собственным процессорным элементом, что позволяет между считыванием информации и ее записью производить необходимую обработку, то есть параллельно выполнять операции арифметического сложения, поиска, а также эмулировать многие черты матричных ВС.

Ассоциативные ВС – ВС класса SIMD, в основе которой лежит ассоциативный процессор. Таким образом, ассоциативные ВС представляют собой n процессорных элементов ПЭ (вертикальный разрядный срез памяти), как правило, последовательной поразрядной обработки для каждой из ячеек памяти. Операция осуществляется одновременно всеми n ПЭ. Все или часть элементарных последовательных ПЭ могут синхронно выполнять операции над всеми ячейками или над выбранным множеством слов ассоциативной памяти.

Пример ассоциативной ВС – система STARAN, разработанная Goodyear Aerospace Corporation в 1972 году.

11. Систолические структуры

В фон-неймановских машинах данные, считанные из памяти, однократно обрабатываются в процессорном элементе, после чего снова возвращаются в память. В систолических структурах данные на своем пути, от считывания из памяти до возвращения обратно, пропускаются через как можно большее число ПЭ.

Если провести параллель в физиологии, то систолы больше всего напоминают систему сосудов и сердце, которое постоянно посылает кровь во все артерии, сосуды и капилляры тела.

Систолические системы являются очень специализированными вычислителями и производятся в основном под конкретную задачу. Фактически, задача построения систолического вычислителя сводится к построению аппаратного конвейера, имеющего достаточно большое время получения результата (т.е. большое количество ступеней) но при этом сравнительно маленькое время между последовательной выдачей результатов, так как значительное количество промежуточных значений обрабатывается на разных ступенях конвейера.

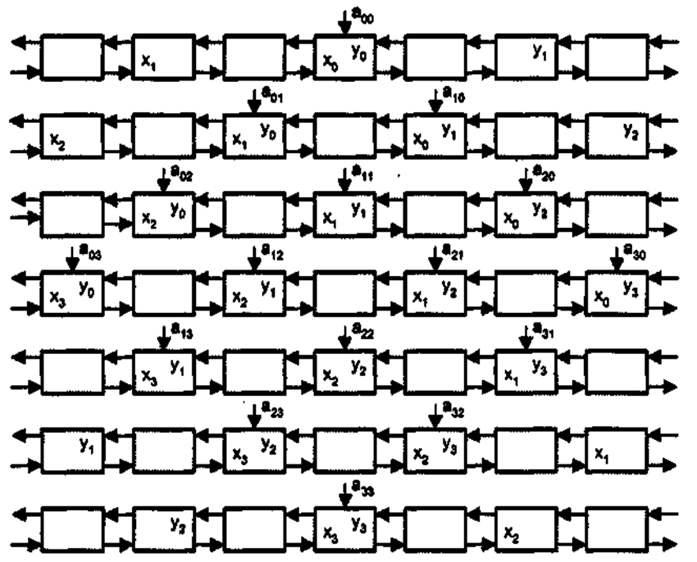

Рассмотрим в качестве примера систолическую структуру, выполняющую процесс векторного умножения матриц. В основе схемы лежит ритмическое прохождение двух потоков данных xi и уj навстречу друг другу. Последовательные элементы каждого потока разделены одним тактовым периодом, чтобы любой из них мог встретиться с любым элементом встречного потока. Вычисления выполняются параллельно в процессорных элементах, каждый из которых реализует один шаг в операции вычисления скалярного произведения (IPS, Inner Product Step) и носит название IPS-элемента.

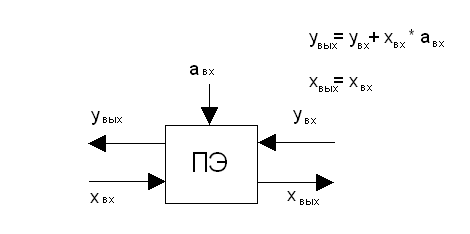

Значение увх, поступающее на вход ПЭ, суммируется с произведением входных значений xвх и авх. Результат выходит из ПЭ как увых. 3начение хвх, кроме того, для возможного последующего использования остальной частью массива транслируется через ПЭ без изменений и покидает его в виде xвых.

Рисунок Функциональная схема IPS-элемента

Рисунок Процесс векторного умножения матриц

Систолическая структура — это однородная вычислительная среда из процессорных элементов, совмещающая в себе свойства конвейерной и матричной обработки и обладающая следующими особенностями:

- вычислительный процесс в систолических структурах представляет собой непрерывную и регулярную передачу данных от одного ПЭ к другому без запоминания промежуточных результатов вычисления;

- каждый элемент входных данных выбирается из памяти однократно и используется столько раз, сколько необходимо по алгоритму, ввод данных осуществляется в крайние ПЭ матрицы;

- образующие систолическую структуру ПЭ однотипны и каждый из них может быть менее универсальным, чем процессоры обычных многопроцессорных систем;

- потоки данных и управляющих сигналов обладают регулярностью, что позволяет объединять ПЭ локальными связями минимальной длины;

- алгоритмы функционирования позволяют совместить параллелизм с конвейерной обработкой данных;

- производительность матрицы можно улучшить за счет добавления в нее определенного числа ПЭ, причем коэффициент повышения производительности при этом линеен.

В настоящее время достигнута производительность систолических процессоров порядка 1000 млрд операций/с.

Классификация систолических структур

Анализ различных типов систолических структур и тенденций их развития позволяет классифицировать эти структуры по нескольким признакам.

По степени гибкости систолические структуры могут быть сгруппированы на:

- специализированные;

- алгоритмически ориентированные;

- программируемые.

Специализированные структуры ориентированы на выполнение определенного алгоритма. Эта ориентация отражается не только в конкретной геометрии систолической структуры, статичности связей между ПЭ и числе ПЭ, но и в выборе типа операции, выполняемой всеми ПЭ. Примерами являются структуры, ориентированные на рекурсивную фильтрацию, быстрое преобразование Фурье для заданного количества точек, конкретные матричные преобразования.

Алгоритмически ориентированные структуры обладают возможностью программирования либо конфигурации связей в систолической матрице, либо самих ПЭ. Возможность программирования позволяет выполнять на таких структурах некоторое множество алгоритмов, сводимых к однотипным операциям над векторами, матрицами и другими числовыми множествами.

В программируемых систолических структурах имеется возможность программирования как самих ПЭ, так и конфигурации связей между ними. При этом ПЭ могут обладать локальной памятью программ, и хотя все они имеют одну и ту же организацию, в один и тот же момент времени допускается выполнение различных операций из некоторого набора. Команды или управляющие слова, хранящиеся в памяти программ таких ПЭ, могут изменять и направление передачи операндов.

По разрядности процессорных элементов систолические структуры делятся

- одноразрядные;

- многоразрядные.

В одноразрядных матрицах ПЭ в каждый момент времени выполняет операцию над одним двоичным разрядом; а в многоразрядных — над словами фиксированной длины.

По характеру локально-пространственных связей систолические структуры бывают:

- одномерные;

- двухмерные;

- трехмерные.

Выбор структуры зависит от вида обрабатываемой информации. Одномерные схемы применяются при обработке векторов, двухмерные - матриц, трехмерные - множеств иного типа.

Систолические структуры могут различаться по топологии связей между ПЭ

- линейные,

- квадратные,

- гексагональные,

- трехмерные и др.

Каждая конфигурация матрицы наиболее приспособлена для выполнения определенных функций, например линейная матрица оптимальна для реализации фильтров в реальном масштабе времени; гексагональная — для выполнения операций обращения матриц, а также действий над матрицами специального вида; трехмерная - для нахождения значений нелинейных дифференциальных уравнений в частных производных. Наиболее универсальными и наиболее распространенными, тем не менее, можно считать матрицы с линейной структурой.