- •Тема 9. Организация памяти вычислительных систем

- •1. Системы с общей и распределенной памятью

- •2. Многоуровневая организация общей памяти

- •3. Память с чередованием адресов

- •4. Симметричные (smp) многопроцессорные вс. Архитектура типа uma, coma, numa

- •5. Мультипроцессор Sun Enterprise 10000

- •Тема 10. Векторные и векторно-конвейерные вычислительные системы

- •1. Понятие вектора и размещение данных в памяти

- •2. Понятие векторного процессора

- •4. Структура векторного процессора

- •5. Структуры типа «память-память» и «регистр-регистр»

- •6. Обработка длинных векторов и матриц

- •Тема 11. Матричные вычислительные системы

- •1. Обобщенная модель матричной вс

- •2. Интерфейсная вм

- •3. Контроллер массива процессоров

- •4. Массив процессоров

- •5. Структура процессорного элемента

- •6. Подключение и отключение процессорных элементов

- •7. Сети взаимосвязей процессорных элементов

- •9. Ассоциативная память

- •10. Ассоциативные вс

- •11. Систолические структуры

- •Тема 12. Кластерные и mpp-системы

- •1. Понятие кластера. Преимущества и виды

- •2. Топологии кластеров

- •3. Примеры кластеров

- •4. Системы с массовым параллелизмом (mpp-системы)

- •Тема 13. Информационные технологии конечного пользователя

- •1. Общая классификация информационных технологий

- •2. Автоматизированное рабочее место – средство автоматизации работы конечного пользователя

- •3. Характеристика информационных технологий в экономике

- •3.1. Информационная технология поддержки принятия решений

- •3.2. Информационная технология экспертных систем

- •3.3. Информационные технологии управления

- •3.4. Автоматизация офиса

- •3.5. Аудио- и видеоконференции в автоматизации офиса

- •3.6. Технологии баз данных

- •Контрольные вопросы

6. Подключение и отключение процессорных элементов

В процессе вычислений в ряде операций должны участвовать только определенные ПЭ, в то время как остальные ПЭ остаются бездействующими. Разрешение и запрет работы ПЭ могут исходить от контроллера массива процессоров (глобальное маскирование) и реализуются с помощью схем маскирования ПЭ. В этом случае решение о необходимости маскирования принимается на этапе компиляции кода. Решение о маскировании может также приниматься во время выполнения программы (маскирование, определяемое данными), при этом опираются на хранящийся в ПЭ флаг разрешения маскирования F.

При маскировании, определяемом данными, каждый ПЭ самостоятельно объявляет свой статус «подключен/не подключен». В составе системы команд имеются наборы маскируемых и немаскируемых команд. Маскируемые команды выполняются в зависимости от состояния флага F, в то время как немаскируемые флаг просто игнорируют. Процедуру маскирования рассмотрим на примере предложения IF-THEN-ELSE, Пусть х - локальная переменная (хранящаяся в локальной памяти каждого ПЭ). Предположим, что процессорные элементы массива параллельно выполняют, ветвление:

if(х > 0) then <оператор А> else <оператор В>

и каждый ПЭ оценивает условие IF. Т.е. ПЭ, для которых условие х > 0 справедливо, установят свой флаг F в единицу, тогда как остальные ПЭ - в ноль. Далее КМП распределяет оператор А по всем ПЭ. Команды, реализующие этот оператор, должны быть маскируемыми. Оператор А будет выполнен только теми ПЭ, где флаг F установлен в единицу. Далее КМП передает во все ПЭ немаскируемую команду ELSE, которая заставит все ПЭ инвертировать состояние своего флага F. Затем КМП транслирует во все ПЭ оператор В, который также должен состоять из маскируемых команд. Оператор будет выполнен теми ПЭ, где флаг F после инвертирования был установлен в единицу, то есть где результат проверки условия х > 0 был отрицательным.

При использовании схемы глобального маскирования контроллер массива процессоров вместе с командами посылает во все ПЭ глобальную маску. Каждый ПЭ декодирует эту маску и по результату выясняет, должен ли он выполнять данную команду или нет. Глобальные и локальные схемы маскирования могут комбинироваться. В таком случае активность ПЭ в равной мере определяется как флагом F, так и глобальной маской.

7. Сети взаимосвязей процессорных элементов

Эффективность сетей взаимосвязей процессорных элементов во многом определяет возможную производительность всей матричной системы. Применение находят самые разнообразные топологии сетей.

Поскольку процессорные элементы в матричных системах функционируют синхронно, обмениваться информацией они также должны по согласованной схеме, причем необходимо обеспечить возможность синхронной передачи от нескольких ПЭ-источников к одному ПЭ-приемнику. Когда для передачи информации в сетевом интерфейсе задействуется только один регистр пересылки данных, это может привести к потере данных, поэтому в ряде ВС для предотвращения подобной ситуации предусмотрены специальные механизмы. Так, в системе СМ-2 используется оборудование, объединяющее сообщения, поступившие к одному ПЭ.

В некоторых SIMD-системах, например МР-1, имеется возможность записать одновременно пришедшие сообщения в разные ячейки локальной памяти.

Хотя пересылки данных по сети инициируются только активными ПЭ, пассивные процессорные элементы также вносят вклад в эти операции. Если активный ПЭ инициирует чтение из другого ПЭ, операция выполняется вне зависимости от статуса ПЭ, из которого считывается информация. То же самое происходит и при записи.

Наиболее распространенными топологиями в матричных системах являются решетчатые и гиперкубические. Так, в ILLIAC IV, МРР и СМ-2 каждый ПЭ соединен с четырьмя соседними. В МР-1 и МР-2 каждый ПЭ связан с восьмью смежными ПЭ. В ряде систем реализуются многоступенчатые динамические сети соединений (МР-1, МР-2, GF11).

8. ВС ILLIAC IV

Матричная система ILLIAC IV (ILLInois Automated Computer) создана Иллинойским университетом и корпорацией Бэрроуз (Burroughs Corporation). Она разрабатывалась с 1966 и в 1972 система эксплуатировалась в Научно-исследовательском центре НАСА (NASA – National Aeronautics and Space Administration – Национальное управление аэронавтики и космоса).

Количество процессоров в системе – 64; быстродействие – 2*108 опер./с; емкость оперативной памяти – 1 М байт; полезное время составляет 80-85% общего времени работы ILLIAC IV, стоимость 40 000 000 долл., вес 75 т, занимаемая площадь 930 м2.

Система ILLIAC IV была включена в вычислительную сеть ARPA (Advanced Research Projects Agency – Управление перспективных исследований и разработок Министерства обороны США) и успешно эксплуатировалось до 1981 г.

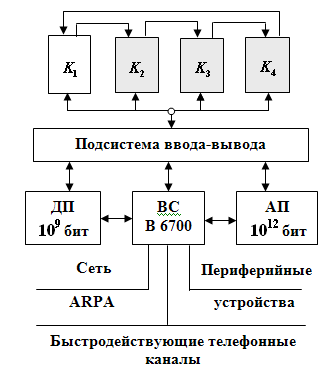

Рисунок Функциональная структура системы ILLIAC IV

Матричная вычислительная система ILLIAC IV должна была состоять из 4 квадрантов (К1–К4), подсистемы ввода-вывода информации, ведущей ВС B 6700 (или B 6500), дисковой памяти (ДП) и архивной памяти (АП). Планировалось, что ВС обеспечит быстродействие 109опер./с. В реализованном варианте ILLIAC IV содержался только один квадрант, что обеспечило быстродействие 2*108опер./с. При этом ILLIAC IV оставалась самой быстродействующей вычислительной системой вплоть до 80-х годов 20 столетия.

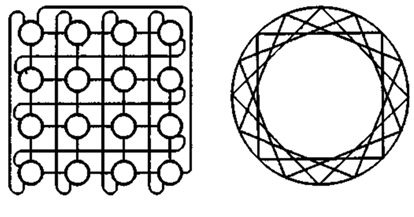

Квадрант – матричный процессор, включавший в себя устройство управления и 64 элементарных процессора. Устройство управления представляло собой специализированную ЭВМ, которая использовалась для выполнения операций над скалярами и формировала поток команд на матрицу ЭП. Элементарные процессоры матрицы регулярным образом были связаны друг с другом. Структура квадранта системы ILLIAC IV представлялась двумерной решеткой, в которой граничные ЭП были связаны по канонической схеме (циркулянтным графом), которую можно изобразить в виде плоской решетки, где узлы в каждом столбце замкнуты в кольцо, а узлы в последовательных рядах соединены в замкнутую спираль. Второй вариант представления – хордальное кольцо с шагом хорды равным 4.

Каждый ЭП имел:

- накапливающий сумматор (64 разряда),

- регистр второго операнда (64 разряда),

- регистр передаваемой информации (из данного ЭП в соседний ЭП) (64 разряда),

- регистр, использовавшийся как временная память (64 разряда),

- регистр модификации адресного поля команды (16 разрядов),

- регистр состояния данного ЭП (8 разрядов).

Рисунок Структура межпроцессорных связей в ILLIACIV

ЭП мог находиться в одном из двух состояний – активном или пассивном. В первом состоянии ему разрешалось, а во втором запрещалось выполнять команды, поступавшие из устройства управления. Состояние ЭП задавалось при помощи специальных команд. Накапливающий сумматор и все регистры ЭП были программно адресуемы.

Память каждого ЭП – 16 Кб. К каждой памяти непосредственный доступ имел собственный ЭП. Обмен информацией между памятями различных ЭП осуществляется по сети связи при помощи специальных команд пересылок.

Подсистема ввода-вывода состояла из устройства управления, буферного запоминающего устройства и коммутатора. Комплекс этих устройств обеспечивал обмен информацией между квадрантами ILLIAC IV и средствами ввода-вывода: ЭВМ В 6700, дисковой и архивной памятью, периферийными устройствами, сетью ARPA.

Ведущая ВС В 6700 – это мультипроцессорная система корпорации Burroughs, которая могла иметь в своем составе от 1 до 3 центральных процессоров и от 1 до 3 процессоров ввода-вывода информации и обладала быстродействием 1–3 млн. операций в секунду. Она использовалась для реализации функций операционной системы (включая ввод-вывод информации, операции по компиляции и компоновке программ, распределение аппаратных ресурсов, исполнение служебных программ и т.п.).

Дисковая память (ДП) состояла из двух дисков и обрамляющих электронных схем.

Эта память имела емкость порядка 109 бит и была снабжена двумя каналами, по каждому из которых можно было параллельно передавать и принимать информацию со скоростью 0,5*109бит/с. Среднее время обращения к диску 20 мс.

Архивная память (АП) – постоянная лазерная память с однократной записью, разработанная фирмой Precision Instrument Company.

В системе ILLIAC IV насчитывалось более 6*106электронных компонентов. Отказы компонентов или соединений могли происходить через несколько часов. По этой причине в систему была включена обширная библиотека контрольных и диагностических тестов.

Средства программирования ILLIAC IV включали язык ассемблера (Assembler Language) и три языка высокого уровня: Tranquil, Glynpir, FORTRAN. Языки высокого уровня в силу архитектурных особенностей ILLIAC IV отличались от соответствующих языков ЭВМ в части распределения двумерной памяти, операций над векторами и пересылок данных.