- •Тема 9. Организация памяти вычислительных систем

- •1. Системы с общей и распределенной памятью

- •2. Многоуровневая организация общей памяти

- •3. Память с чередованием адресов

- •4. Симметричные (smp) многопроцессорные вс. Архитектура типа uma, coma, numa

- •5. Мультипроцессор Sun Enterprise 10000

- •Тема 10. Векторные и векторно-конвейерные вычислительные системы

- •1. Понятие вектора и размещение данных в памяти

- •2. Понятие векторного процессора

- •4. Структура векторного процессора

- •5. Структуры типа «память-память» и «регистр-регистр»

- •6. Обработка длинных векторов и матриц

- •Тема 11. Матричные вычислительные системы

- •1. Обобщенная модель матричной вс

- •2. Интерфейсная вм

- •3. Контроллер массива процессоров

- •4. Массив процессоров

- •5. Структура процессорного элемента

- •6. Подключение и отключение процессорных элементов

- •7. Сети взаимосвязей процессорных элементов

- •9. Ассоциативная память

- •10. Ассоциативные вс

- •11. Систолические структуры

- •Тема 12. Кластерные и mpp-системы

- •1. Понятие кластера. Преимущества и виды

- •2. Топологии кластеров

- •3. Примеры кластеров

- •4. Системы с массовым параллелизмом (mpp-системы)

- •Тема 13. Информационные технологии конечного пользователя

- •1. Общая классификация информационных технологий

- •2. Автоматизированное рабочее место – средство автоматизации работы конечного пользователя

- •3. Характеристика информационных технологий в экономике

- •3.1. Информационная технология поддержки принятия решений

- •3.2. Информационная технология экспертных систем

- •3.3. Информационные технологии управления

- •3.4. Автоматизация офиса

- •3.5. Аудио- и видеоконференции в автоматизации офиса

- •3.6. Технологии баз данных

- •Контрольные вопросы

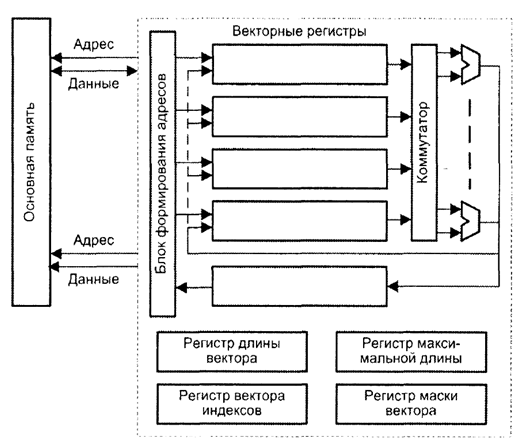

4. Структура векторного процессора

Обобщенная структура векторного процессора приведена на рис. На схеме показаны основные узлы процессора, без детализации некоторых связей между ними.

Особенности векторного процессора

- Обработка всех n компонентов векторов-операндов задается одной векторной командой.

- Элементы векторов представляются числами в форме с плавающей запятой (ПЗ).

-АЛУ векторного процессора может быть реализовано в виде:

- единого конвейерного устройства, способного выполнять все предусмотренные операции над числами с ПЗ

- АЛУ состоит из отдельных блоков сложения и умножения, а иногда и блока для вычисления обратной величины, когда операция деления x/y реализуется в виде x(1/y). Каждый из таких блоков также конвейеризирован.

Состав векторной системы:

- Cкалярный процессор, что позволяет параллельно выполнять векторные и скалярные команды.

- Векторные регистры для хранения векторов-операндов, которые представляют собой совокупность скалярных регистров, объединенных в очередь типа FIFO, способную хранить 50-100 чисел с плавающей запятой.

Набор векторных регистров (Va, Vb, Vc,...) имеется в любом векторном процессоре. Система команд векторного процессора поддерживает работу с векторными регистрами и обязательно включает в себя команды:

- загрузки векторного регистра содержимым последовательных ячеек памяти, указанных адресом первой ячейки этой последовательности;

- выполнения операций над всеми элементами векторов, находящихся в векторных регистрах;

- сохранения содержимого векторного регистра в последовательности ячеек памяти, указанных адресом первой ячейки этой последовательности.

- Регистр длины вектора. Этот регистр определяет, сколько элементов фактически содержит обрабатываемый в данный момент вектор, то есть сколько индивидуальных операций с элементами нужно сделать.

- Регистр максимальной длины вектора, определяющий максимальное число элементов вектора, которое может быть одновременно обработано аппаратурой процессора. Этот регистр используется при разделении очень длинных векторов на сегменты, длина которых соответствует максимальному числу элементов, обрабатываемых аппаратурой за один прием.

- Регистр маски вектора служит для выполнения таких операций, в которых должны участвовать не все элементы векторов. В этом регистре каждому элементу вектора соответствует один бит. Установка бита в единицу разрешает запись соответствующего элемента вектора результата в выходной векторный регистр, а сброс в ноль — запрещает.

- Регистр вектора индексов по структуре аналогичен регистру маски. Служит для выполнения операций упаковки/распаковки для получения вектора, содержащего ненулевые элементы и для обратной операции соответственно. В векторе индексов каждому элементу исходного вектора соответствует один бит. Нулевое значение бита свидетельствует, что соответствующий элемент исходного вектора равен нулю.

Достоинства векторного процессора

1) Вместо многократной выборки одних и тех же команд достаточно произвести выборку только одной векторной команды, что позволяет сократить издержки за счет устройства управления и уменьшить требования к пропускной способности памяти.

2) Векторная команда обеспечивает процессор упорядоченными данными. Когда инициируется векторная команда, ВС знает, что ей нужно извлечь n пар операндов, расположенных в памяти регулярным образом. Таким образом, процессор может указать памяти на необходимость начать извлечение таких пар. Если используется память с чередованием адресов, эти пары могут быть получены со скоростью одной пары за цикл процессора и направлены для обработки в конвейеризированный функциональный блок. При отсутствии чередования адресов или других средств извлечения операндов с высокой скоростью преимущества обработки векторов существенно снижаются.