- •Тема 9. Организация памяти вычислительных систем

- •1. Системы с общей и распределенной памятью

- •2. Многоуровневая организация общей памяти

- •3. Память с чередованием адресов

- •4. Симметричные (smp) многопроцессорные вс. Архитектура типа uma, coma, numa

- •5. Мультипроцессор Sun Enterprise 10000

- •Тема 10. Векторные и векторно-конвейерные вычислительные системы

- •1. Понятие вектора и размещение данных в памяти

- •2. Понятие векторного процессора

- •4. Структура векторного процессора

- •5. Структуры типа «память-память» и «регистр-регистр»

- •6. Обработка длинных векторов и матриц

- •Тема 11. Матричные вычислительные системы

- •1. Обобщенная модель матричной вс

- •2. Интерфейсная вм

- •3. Контроллер массива процессоров

- •4. Массив процессоров

- •5. Структура процессорного элемента

- •6. Подключение и отключение процессорных элементов

- •7. Сети взаимосвязей процессорных элементов

- •9. Ассоциативная память

- •10. Ассоциативные вс

- •11. Систолические структуры

- •Тема 12. Кластерные и mpp-системы

- •1. Понятие кластера. Преимущества и виды

- •2. Топологии кластеров

- •3. Примеры кластеров

- •4. Системы с массовым параллелизмом (mpp-системы)

- •Тема 13. Информационные технологии конечного пользователя

- •1. Общая классификация информационных технологий

- •2. Автоматизированное рабочее место – средство автоматизации работы конечного пользователя

- •3. Характеристика информационных технологий в экономике

- •3.1. Информационная технология поддержки принятия решений

- •3.2. Информационная технология экспертных систем

- •3.3. Информационные технологии управления

- •3.4. Автоматизация офиса

- •3.5. Аудио- и видеоконференции в автоматизации офиса

- •3.6. Технологии баз данных

- •Контрольные вопросы

2. Интерфейсная вм

Интерфейсная ВМ (ИВМ) соединяет матричную SIMD-систему с внешним миром, используя для этого какой-либо из сетевых интерфейсов, например Ethernet, как это имеет место в системе MasPar MP-1. Интерфейсная ВМ работает под управлением операционной системы, чаще всего ОС UNIX. На ИВМ пользователи подготавливают, компилируют и отлаживают свои программы. В процессе выполнения программы сначала загружаются из интерфейсной ВМ в контроллер управления массивом процессоров, который выполняет программу и распределяет команды и данные по процессорным элементам массива. В некоторых ВС, например в Massively Parallel Computer MPP, при создании, компиляции и отладке программ КМП и интерфейсная ВМ используются совместно.

На роль ИВМ подходят различные вычислительные машины. Так, в системе СМ-2 в этом качестве выступает рабочая станция SUN-4, в системе MasPar — DECstation 3000, а в системе МРР - DEC VAX-11/78

3. Контроллер массива процессоров

Функции контроллера массива процессоров:

- выполняет последовательный программный код,

- реализует команды ветвления программы,

- транслирует команды и сигналы управления в процессорные элементы.

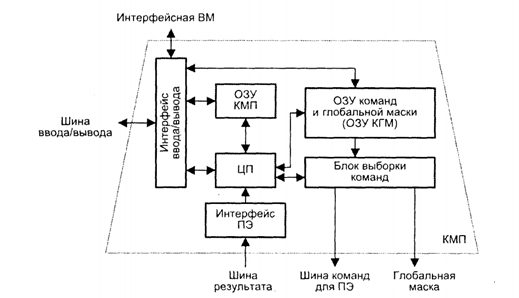

Рисунок иллюстрирует одну из возможных реализаций КМП, в частности принятую в устройстве управления системы PASM (Partitioned SIMD/MIMD computer).

Рисунок Контроллер массива процессоров

При загрузке из ИВМ программа через интерфейс ввода/вывода заносится в оперативное запоминающее устройство КМП (ОЗУ КМП). Команды для процессорных элементов и глобальная маска, формируемая на этапе компиляции, также через интерфейс ввода/вывода загружаются в ОЗУ команд и глобальной маски (ОЗУ КГМ). Затем КМП начинает выполнять программу, извлекая либо одну скалярную команду из ОЗУ КМП, либо множественные команды из ОЗУ КГМ. Скалярные команды - команды, осуществляющие операции над хранящимися в КМП скалярными данными, выполняются центральным процессором (ЦП) контроллера массива процессоров. В свою очередь, команды, оперирующие параллельными переменными, хранящимися в каждом ПЭ, преобразуются в блоке выборки команд в более простые единицы выполнения - нанокоманды. Нанокоманды совместно с маской пересылаются через шину команд для ПЭ на исполнение в массив процессоров. Например, команда сложения 32-разрядных слов в КМП системы МРР преобразуется в 32 нанокоманды одноразрядного сложения, которые каждым ПЭ обрабатываются последовательно,

В большинстве алгоритмов дальнейший порядок вычислений зависит от результатов и/или флагов условий предшествующих операций. Для обеспечения такого режима в матричных системах статусная информация, хранящаяся в процессорных элементах, должна быть собрана в единое слово и передана в КМП для выработки решения о ветвлении программы. Например, в предложении

IF A (условие A) THEN DO В

оператор В будет выполнен, если условие А справедливо во всех ПЭ. Для корректного включения/отключения процессорных элементов КМП должен знать результат проверки условия А во всех ПЭ. Такая информация передается в КМП по однонаправленной шине результата. В системе СМ-2 эта шина названа GLOBAL. В системе МРР для той же цели организована структура, называемая деревом SUM - OR. Каждый ПЭ помещает содержимое своего одноразрядного регистра признака на входы дерева, которое с помощью операции логического сложения комбинирует эту информацию и формирует слово результата, используемое в КМП для принятия решения.