- •Московский Государственный Университет Путей Сообщения (миит)

- •Курсовой проект

- •«Разработка эквалайзера»

- •Содержание

- •Введение

- •1. Цифровые сигнальные процессоры.

- •2. Общие сведения о продукции фирмы analog devices

- •2.1. Продукция компании

- •Архитектура процессора adsp-21xx

- •3.1 Интерфейс памяти и процессора

- •3.2 Набор инструкций

- •3.3 Производительность для задач dsp

- •3.4 Вычислительные устройства

- •3.5 Генераторы адресов данных и счетчик команд

- •3.6 Шины

- •Последовательные порты (sporTs)

- •3.8 Таймер

- •3.9 Порт интерфейса с хост-процессором (hip)

- •Задание

- •4. Разработка алгоритма цифровой обработки сигнала

- •5. Определение порядка и синтез коэффициентов цифровых фильтров (firf), входящих в состав эквалайзера

- •5.1. Фильтр нижних частот (фнч).

- •5.2. Полосовой фильтр №1 (пф1)

- •5.3. Полосовой фильтр №2 (пф2)

- •5.4. Полосовой фильтр №3 (пф3)

- •5.5. Полосовой фильтр №4 (пф4)

- •6. Построение ачх цифровых фильтров (firf), входящих в состав эквалайзера

- •7. Описание схемы эквалайзера

- •7.1 Системный интерфейс dsp

- •7.2. Описание ацп

- •Организация параллельного интерфейса с dsp-процессорами: чтение данных из ацп, подключенного с отображением в адресное пространство памяти

- •7.3. Описание цап организация параллельного интерфейса с dsp-процессорами: запись данных в цап, подключенный с отображением в адресное пространство памяти

- •8. Алгоритма работы устройства adsp-21xx

- •Список использованной литературы

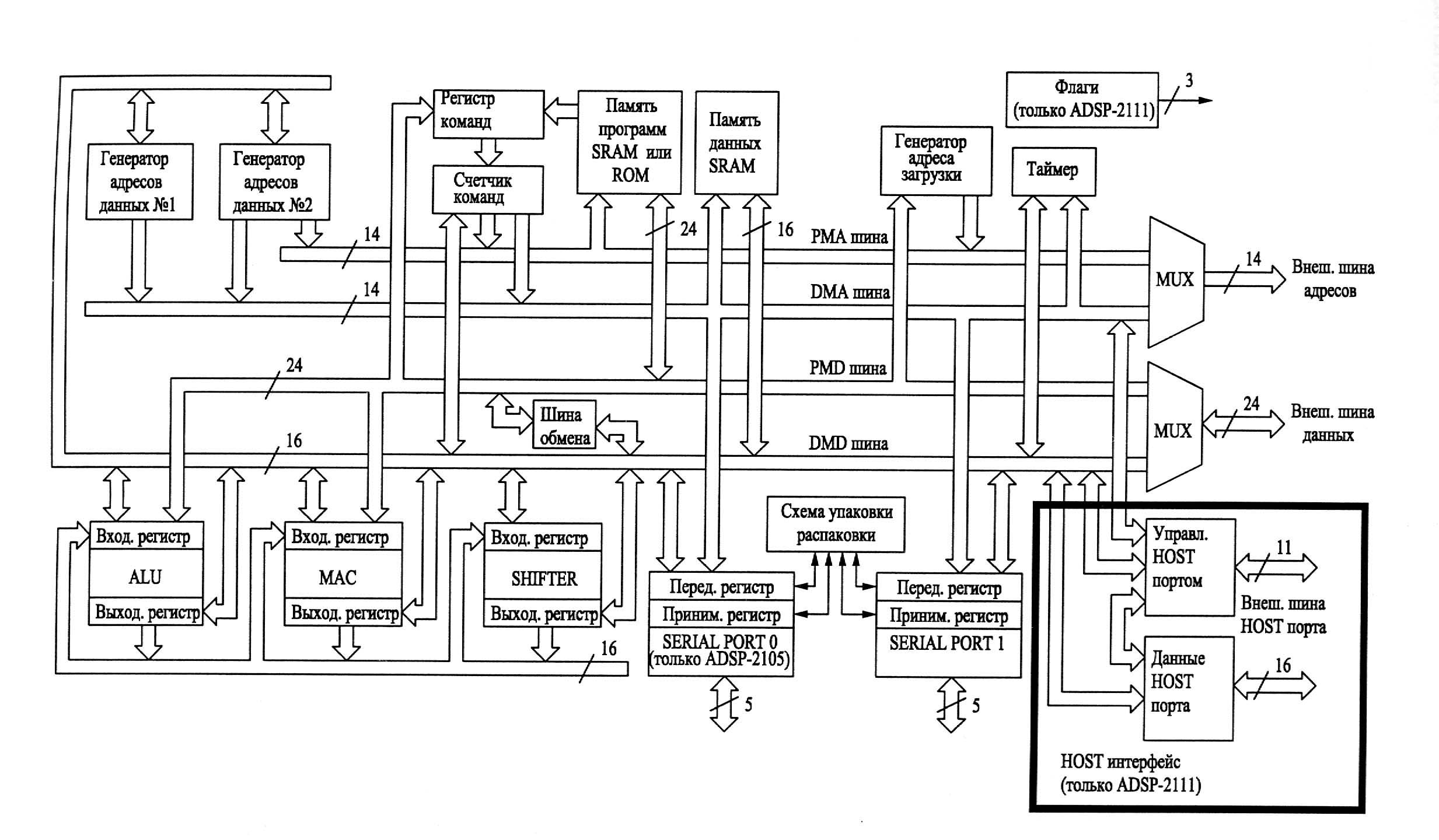

3.6 Шины

Внутренние устройства связываются пятью шинами. Шина адрес памяти данных DMA (Data Memory Address) и шина адреса памяти инструкций РМА (Program Memory Address) используются для указания адресов, относящихся к памяти данных и инструкций. Шины данных памяти данных соответствующего адресного пространства. Эти 4 шины мультиплексированы в 2е шины: шину адреса и шину данных; сигналы BMS, DMS и PMS выбирают в этом случае адресное пространство. Шина внутренних результатов R прямо связывает различные внутренние устройства и обеспечивает передачу промежуточных результатов.

Ширина шины РМА - 14 бит что обеспечивает доступ к 16 КБайта инструкций и данных. Шина PMD имеет ширину 24 бита, что обеспечивает загрузку 24-битной инструкции.

Ширина шины DMA - 14 бит, что обеспечивает доступ к 16 КБайта данных. Шина DMD имеет ширину 16 бит, что обеспечивает пересылку любого регистра процессора в любой другой регистр или в память/из памяти в течение одного цикла. Адрес памяти данных формируется из абсолютного значения, записанного в инструкции (абсолютная адресация), или из генератора адресов данных (косвенная адресация). Только косвенная адресации возможна для адресации данных в памяти программ. Шина PMD также может быть использована для пересылок данных в/из вычислительных устройств напрямую или через устройство обмена между шинами PMD-DMD. Устройство обмена между шинами PMD-DMI позволяет пересылать данные с одной шины на другую и содержит логику для преодоления разницы ширины в 8 бит между двумя шинами.

Последовательные порты (sporTs)

Почти, все процессоры семейства имеют 2 двунаправленных последовательных порта (SPORT) с двойной буферизацией. Эти порты используют синхронную передачу данных и используют кадровые сигналы чтобы контролировать поток данных. Каждый порт может тактироваться из внутреннего таймера или от внешней частоты. Сигналы кадровой синхронизации могут быть сгенерированы как самим портом, так и получены извне. Длина слова может меняться от 3 бит до 16. Один порт (SPORT0) имеет многоканальные возможности, что позволяет получать и передавать слова данных из 24- или 32-словного потока битов. Другой порт (SPORT 1) может быть сконфигурирован для использования внешних сигналов прерывания IRQI и IRQ2 и внешних сигналов Flag out (FO) и Flag in (Fl)

3.8 Таймер

Программируемый интервальный таймер обеспечивает периодическую генерацию прерываний, 8-битный масштаб позволяет ему декрементировать содержимое 16-битного регистра-счетчика в диапазоне от каждого цикла до каждого 256-го цикла процессора. Прерывание генерируется когда регистр-счетчик обнуляется. Регистр-счетчик автоматически загружается из 6-битного регистра интервала и отсчет времени немедленно возобновляется.

3.9 Порт интерфейса с хост-процессором (hip)

Порт HIP - параллельный порт ввода-вывода, позволяющий легко подсоединить хост-процессор. Через этот порт процессор может быть использован как периферийное устройство хост-процессора с отображением регистров процессора семейства ADSP-21xx на адресное пространство хост-процессора. HIP работает параллельно и асинхронно с вычислительными устройствами и памятью процессора семейства. HIP состоит из регистров через которые происходит обмен данными и статусной информацией. Он может быть настроен на 8/16 битные типы данных; на мультиплексированную шину адреса/данных или на раздельные шины; на раздельные строб-импульсы для чтения/записи или на строб-импульс чтения/записи и строб-импульс данных (DMD). Вычислительные операции обычно берут операнды из входных регистров и помещают результат в выходной регистр. Эти регистры обеспечивают буферизацию между вычислительными устройствами и памятью. Шина внутренних результатов позволяет использовать результат предыдущего вычисления использовать непосредственно как операнд операции. Это исключает задержки в случае выполнения серии различных операций. Структурная схема процессора представлена на рис.1.

Рис.3.1. Структурная схема процессора.