- •Дисциплина: «микропроцессоры и микропроцессорные системы»

- •Отличительные особенности поколений процессоров. Микропроцессоры: определение, назначение, классификация и параметры. Поколения процессоров.

- •2. Системы эвм.

- •3.Обобщенная структурная схема микропроцессора.

- •4. Типичный машинный цикл. Пути обработки командного слова.

- •5. Типичный машинный цикл. Пути обработки информационного слова.

- •6. Запоминающие устройства: назначение, классификация, параметры.

- •7.Элементы и модули статических и динамических зу: режимы работы.

- •8. Постоянные и перепрограммируемые зу. Элементы перепрограммирования.

- •10. Организация подсистемы прерываний микропроцессорной системы. Классы прерываний. Структура контроллера прерываний. Процедура обслуживания прерывания.

- •11. Организация режима прямого доступа в память. Контроллер пдп.

- •12. Организация службы времени. Программируемый таймер.

- •13. Контроллер видеотерминала. Структурная схема.

- •14. Схема включения контроллера видеотерминала в мпс.

- •15. Особенности архитектуры микропроцессоров Intel 80486 и Pentium. Структурная схема.

- •16. Эволюция архитектуры микропроцессоров. Конвейерная обработка команд.

- •17. Семейства микро-эвм. Ключевые микросхемы пк ibm pc и совместимых с ними.

- •18. Многомашинные вычислительные системы. Структурная схема.

- •19. Многопроцессорные вычислительные системы. Структурная схема.

- •20. Микроконтроллеры avr: система команд.

- •21. Интегрированная среда разработки программного обеспечения (ис рпо) для семейства мк avr. Компиляция, компоновка, отладка.

- •22. Программирование микроконтроллера на языке Assembler (asm): процедуры, подпрограммы, директивы.

- •23. Взаимодействие мк с объектами управления.

- •24. Программируемые логические матрицы. Программируемая матричная логика. Стратегия и этапы проектирования.

- •Дисциплина: «конструирование, производство и эксплуатация средств вычислительной техники»

- •25. Жизненный цикл технической системы. Структура жизненного цикла. Компьютерное сопровождение процессов жизненного цикла изделий – кспи.

- •26. Комплекс работ по созданию новой техники. Этапы проектирования.

- •27. Модульный принцип конструирования. Уровни конструктивных модулей свт. Электрические соединения в конструкциях эвм. Конструкторская, технологическая и нормативно-техническая документация.

- •28. Единая система конструкторской документации – ескд. Виды конструкторской документации.

- •29. Единая система технологической документации – естд. Виды технологической документации.

- •30. Конструирование печатных плат. Гост'ы на печатные платы. Типы печатных плат: опп, дпп, мпп, гпп.

- •31. Классы точности печатных плат (отечественные и зарубежные). Размеры печатных плат. Маркировка печатных плат.

- •32. Обеспечение помехоустойчивости в конструкциях свт. Причины возникновения помех.

- •34. Принципы конструирования печатных плат: моносхемный, схемно-узловой, каскадно-узловой, функционально-узловой.

- •35. Системы автоматизированного проектирования (сапр). Структура сапр. Виды обеспечения (подсистемы) сапр.

- •36. Комплексы технических средств сапр. Основные требования к информационным системам; базы данных (бд), субд.

- •37. Классификация по сапр. Системы проектирования электрических схем.

- •38. Системы проектирования печатных плат.

- •39. Компьютерные чертёжно-графические системы для разработки конструкторской документации аппаратно-программных систем.

- •40. Производственный процесс: типы; основные характеристики; составные части; производственного процесса. Изделия: виды изделий.

- •41. Стадии производственных процессов. Технологическое оборудование, приспособления и оснастка. Типы производства: единичное, серийное, массовое.

- •42. Виды технологических процессов. Исходные данные для разработки тп. Основные принципы организации тп

- •43. Материалы, переменяемые для изготовления печатных плат. Фольгированные и нефольгированные диэлектрики; стеклотекстолит. Изготовление оригиналов и фотошаблонов.

- •44. Технологические процессы изготовления пп: субтрактивные, аддитивные.

- •46. Типовая структура тп изготовления тэз'ов. Сборочные процессы в производстве свт: установка корпусных навесных элементов на платы. Компоновка тэз'ов.

- •47. Выходной контроль собранной системы. Регулировка. Испытания.

- •48. Надёжность. Критерии надёжности. Культура производства. Субъективные и объективные эксплуатационные факторы. Способы повышения надёжности.

- •49. Автоматизация производства свт: сапр, астпп, гпс. Промышленные работы.

- •50. Техническое обслуживание; контроль и диагностика свт. Виды неисправностей свт и способы их устранения.

- •Дисциплина: «операционные системы и среды»

- •51. Понятие процесс. Состояние процессов. Контекст и дескриптор процесса.

- •52. Алгоритмы планирования процессов. Алгоритмы основанные на квантовании. Алгоритмы основанные на приоритетах.

- •53. Абсолютные и относительные приоритеты. Вытесняющие и невытесняющие алгоритмы планирования.

- •54. Задача по управлению файлами и устройствами. Организация параллельной работы устройств ввода-вывода и процессора. Согласование скоростей обмена и кэширование данных.

- •55. Управление реальной памятью. Функции ос по управлению реальной памятью. Типы адресов.

- •56. Файловая система. Цели и задачи файловой системы. Каталоги.

- •57. Иерархическая структура файловой системы. Атрибуты файлов

- •58. Типы файлов. Имена файлов.

- •59. Виды интерфейсов пользователя ос unix.Графический, командный и программный интерфейс.

- •60. Типы файлов ос unix. Генерация имен файлов. Структура каталогов ос unix.

- •61. Основные каталоги в корне системы. Их название и назначение.

- •62. Управление правами доступа к файлам и каталогам в ос unix. Категории пользователей в системе. Изменение прав доступа файла/каталога.

- •63. Создание и редактирование текстовых файлов. Выход из текстового редактора. Команды режима ввода текста. Команды удаления текста.

- •64. Создание и редактирование текстовых файлов. Выход из текстового редактора. Команды отмены. Команды копирования.

- •65. Команды поиска файлов в ос linux. Основные команды поиска, различия между ними. Основные флаги команд поиска.

- •Дисциплина: «компьютерные сети и телекоммуникации»

- •65.Определение локальной сети. Сетевой сервис. Классификация сетей. Типы серверов.

- •Базовые сетевые топологии: полносвязные, неполносвязные (шинная, звездообразная, кольцевая, иерархическая).

- •Стандарты кабелей. Виды кабелей: коаксиал, витая пара, волоконно– оптические.

- •Методы передачи дискретных данных: аналоговая модуляция, цифровое кодирование.

- •Модель взаимодействия открытых систем osi. Понятие многоуровнего подхода. Функции уровней модели osi.

- •Технология Ethernet (ieee 802.3). Метод доступа csma/cd. Этапы доступа к среде. Возникновение коллизий.

- •Технология Ethernet (ieee 802.3). Форматы кадров технологии Ethernet.

- •Технология TokenRing (ieee 802.5). Основные характеристики. Маркерный доступ к разделяемой среде.

- •Технология TokenRing (ieee 802.5). Форматы кадров TokenRing. Физический уровень технологии TokenRing.

- •Технология fddi. Основные характеристики. Особенности метода доступа. Отказоустойчивость технологии. Физический уровень технологии fddi.

- •Сетевое оборудование: сетевые адаптеры. Функции и характеристики сетевых адаптеров. Классификация.

- •Сетевое оборудование: концентраторы и коммутаторы. Основные и дополнительные функции. Конструктивное исполнение. Принцип работы. Основное отличие концентраторов от коммутаторов.

- •Сетевое оборудование: мосты. Принцип работы мостов. Логическая структуризация сети с помощью мостов и коммутаторов.

- •Сетевое оборудование: маршрутизатор. Функции маршрутизатора. Протоколы маршрутизации.

- •Глобальные связи на основе выделенных линий. Аналоговые и цифровые выделенные линии. Модемы для работы на выделенных линиях.

- •Глобальные связи на основе сетей с коммутацией каналов. Аналоговые телефонные сети. Модемы для работы на коммутируемых аналоговых линиях.

- •Структурированная кабельная система /скс/. Иерархия в кабельной системе. Выбор типа кабелей для различных подсистем.

- •Линии связи. Аппаратура линий связи. Характеристики линий связи.

- •Дисциплина: «периферийные устройства вычислительной техники»

- •Определение, состав и назначение системной платы в составе пк.

- •Ide(дисководы, старые харды) и разъем бп

- •Bios, определение, назначение и основные функции.

- •Блок питания. Определение, назначение. Форм-фактор at. Основные технические параметры блока питанияAt.

- •Блок питания. Определение, назначение. Форм-фактор atx. Основные технические параметры блока питанияAtx.

- •Жесткий диск. Определение, назначение. Состав основных узлов. Основные технические параметры жесткого диска.

- •Определение, назначение, состав основных узлов дисковода гибких дисков. Принцип работы гибких дисков.

- •Конструкция дискеты. Логическая структура гибкого диска.

- •Определение, назначение, разновидности приводов cd-rom. Основные технические параметры приводов cd-rom.

- •Принцип действия монитора на основе элт. Основные технические параметры мониторов на основе элт.

- •Принцип действия жк монитора. Основные технические параметры жк монитора.

- •Назначение и принцип действия видеоадаптера.

- •Назначение и принцип звуковой карты.Основные технические параметры звуковой карты.

- •Функциональная схема видеоадаптера. Основные технические параметры видеоадаптеров.

- •Классификация принтеров.

- •Принцип действия струйного принтера.

- •Принцип действия лазерного принтера.

- •Принцип действия струйного плоттера.

- •Классификация сканеров, принцип действия планшетного сканера.

- •1. Ручные – в магазах штрих коды считывает

- •Классификация цифровых фотокамер. Принцип действия цифровой фотокамеры. Основные технические параметры цифровой фотокамеры.

- •Функциональная схема цифровой фотокамеры.

- •Назначение, принцип действия мыши. Основные технические параметры клавиатуры.

- •Назначение, принцип действия клавиатуры. Основные технические параметры клавиатуры.

- •Дисциплина: «программирование на языке высокого уровня»

- •Понятие алгоритма. Методы описания алгоритма.

- •107. Основные алгоритмические конструкции: линейный алгоритм, разветвляющийся, циклический.

- •Базовые алгоритмические структуры

- •Разветвляющиеся вычислительные процессы в языках высокого уровня (Pascalили си): ветвление и множественный выбор.

- •109. Организация циклических процессов в языках высокого уровня (си или Pascal). Три типа операторов цикла.

- •Алгоритм сортировки массивов. Метод установки.

- •111. Алгоритмы сортировки массивов. Метод пузырька.

- •Матрица. Ввод и вывод элементов матрицы.

- •113.Определение индексов элементов матрицы, расположенных на, над и под главной и побочной диагональю.

- •Представление символьных и строковых данных в языках высокого уровня (си или Pascal). Объявление типа, описание переменных.

- •115. Операции над строковыми переменными.

- •Процедуры и функции пользователя в языках высокого уровня (си или Pascal). Описание и вызов процедур и функций. Формальные и фактические параметры, связь между ними.

- •117. Организация работы с файлами из программы (стандартные функции обработки файлов).

- •Ввод и вывод данных из файла (матрица и массив).

- •119. Стандартные функции ввода и вывода данных (си или Pascal).

- •120. Ввод и вывод элементов в одномерном массиве. Обращение к элементам массива при помощи индекса и при помощи указателя.

14. Схема включения контроллера видеотерминала в мпс.

Вся теория в ответе на вопрос № 13.

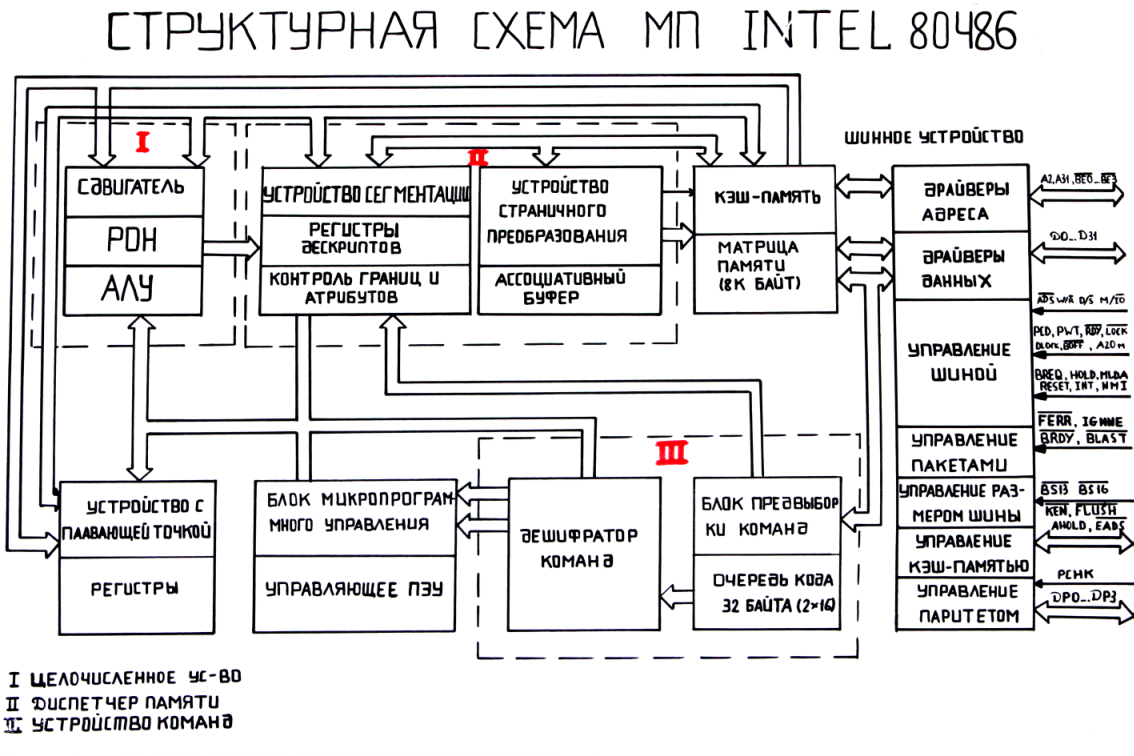

15. Особенности архитектуры микропроцессоров Intel 80486 и Pentium. Структурная схема.

МП Intel 80486 реализован с использованием новой архитектуры по сравнению с предшествующими моделями.(С моделями типа Intel 80x86) Повышение производительности в 2-4 раза по сравнению с предшественниками достигнуто в данной схеме за счет новых решений архитектуры. Внутренняя ШД увеличена до 64 разрядов, КЕШ память, математический сопроцессор выполнен на одном кристалле с основным процессором. Микросхема содержит более 1.3 миллиона транзисторов. Корпус микросхемы выполнен в виде матрицы со 168 штырьковыми выводами, столбцы выводов пронумерованы от ключа с лева не право буквами латинского алфавита ( от A до S ) а строки снизу в верх арабскими цифрами.

В состав структурной схемы микросхемы входят

целочисленное устройство

устройство с плавающей точкой соответствует математическому сопроцессору Intel 80387. Оно содержит собственный стек из 8ми 80ти разрядных регистров и содержит схему для работы с форматами чисел с плавающей запятой.

устройство управления

диспетчер памяти

устройство команд.

КЕШ память

шинное устройство.

Шинное устройство подтверждает обмен информацией МП и памятью с контроллерами ввода-вывода и др. активными устройствами. Оно содержит ША, ШУ, схему управления размером шины ( Разрядность) , пакетами данных, КЭШем, приоритетами. Шинное устройство осуществляет обмен по 32-разрядной, двунаправленной ШД, 34-разрядной ША и 32-разрядной ШУ. Набор линий шин управления, циклы обмена отличаются от 386 процессора таким образом, что за 1 цикл может осуществляться передача слов разрядностью кратной байту. ША включает 30 адресных линий и 4 линии выбора байта. ШД с побайтовой организацией передачи. К отличиям шинного устройстваможно отнести машинный такт длительностью в 1 период внешнего синхросигнала.

КЭШ-память представляет собой быстродействующую буферную память ограниченного объема, но повышенного быстродействия. Когда процессор обращается за следующей командой или данными в КЭШ память (КЭШ попадание) то временной цикл на извлечение этой информации из основной оперативной памяти не нужен. При отсутствии необходимой информации в КЭШ памяти (КЭШ промах) необходимо производить выбор ее из основной оперативной памяти и одновременно записать в КЭШ память. Высокий процент КЭШ попаданий повышает производительность МП. Считается граничная цифра попаданий не ниже 80%. В 486 МП при использовании его в МПС возможна организация 2х уровневого КЭШа . ( первый уровень на кристалле МП а другой вынесен). Адресация данной КЕШ памяти выполняется 22х разрядными командами адресации.

Устройство команд содержит:

Блок предварительной выборки

Блок выборки и дешифрации

Находящиеся в КЕШ памяти команды доступны блоку предварительной выборки команд, который имеет очередь команд ожидающих выполнения.

Блок Местного управления осуществляет интерпретацию слова команды и формирует управление микропрограммой и ее исполнения.

В восстав целочисленного устройства входит АЛУ и 8 32-разрядных РОНов и многоразрядный сдвигатель, используемый при арифметических и логических операциях, при операциях умножения-деления. Содержимое РОНов подается в устройство сегментации по отдельной 32х разрядной шине.

Устройство с плавающей точкой соответствует математическому сопроцессору Intel 80387. Оно содержит собственный стек из 8ми 80ти разрядных регистров и содержит схему для работы с форматами чисел с плавающей запятой.

Диспетчер памяти состоит из устройств сегментации и страничного преобразования и обеспечивает формирование физических адресов, сначала в приделах сегмента, а затем в приделах страницы. И поддерживает 2 основных режима работы МП. (Реальный и Защищенный)

В реальном режиме МП работает с очень высоким быстродействием , при этом реализуется расширенный набор команд, используется большой объем памяти и различные методы адресации.

В защищенном режиме выполняется несколько программ одновременно. В этом случае необходима защита от несанкционированного доступа пользователей к задачам друг друга. Устройство страничной адресации действует только в защищенном режиме. Когда каждый сегмент разделяется на страницы памяти, размером по 4Кб которые могут размещаться в любом месте памяти. Устройство сегментации и страничной адресации обеспечивают гибкость МПС и защиту информации.

Набор регистров 486МП включают в себя все регистры 386МП и 387сопроцессора. Кроме того в систему добавлено 3 системных регистра, регистры для операндов с плавающей запятой

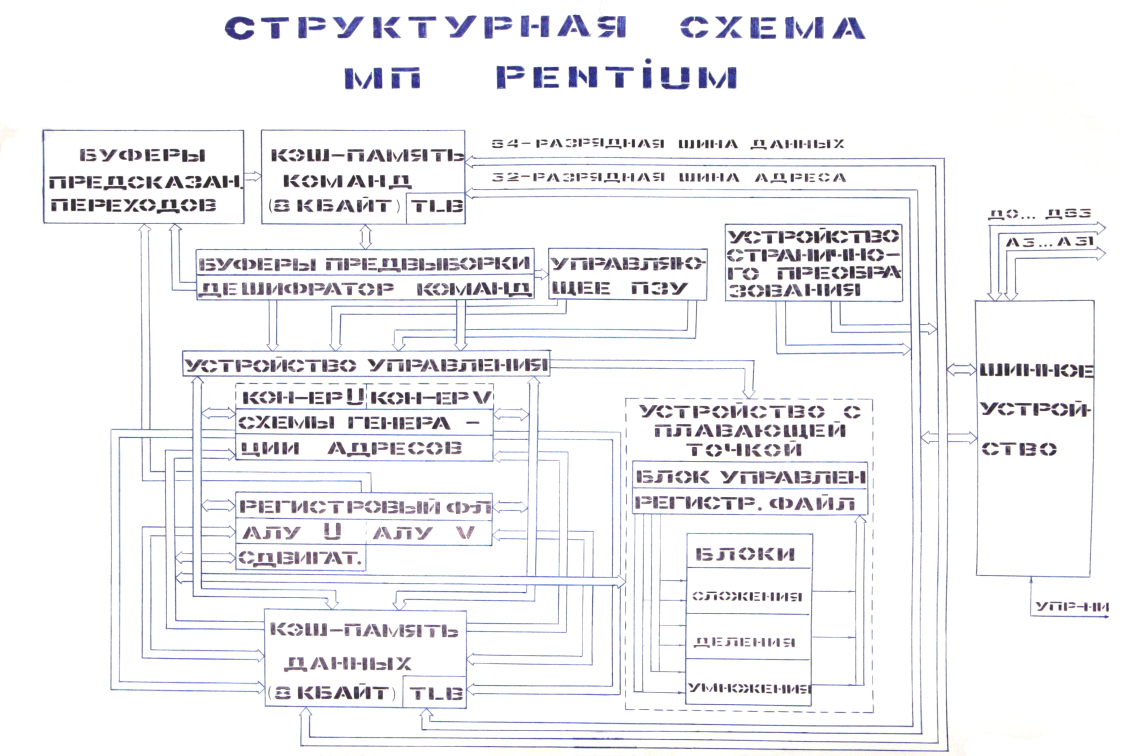

МП Pentium является представителем следующего после 386ого поколения. Представитель фирмы Intel. Он совместим со всеми предыдущими моделями типа 80Х86. новая архитектура, отдельные КЭШ памяти команд и данных, конвейерное устройство обеспечивают значительное повышение производительности. Кристалл данного МП содержит 3.1 млн. транзисторов, реализованных 0.8 микронными технологическими нормами.

Корпус выполнен в виде керамической матрицы с числом рядов 21 на 21 по 4 вывода в каждом ряду. Общее число выводов 273. Столбцы выводов пронумерованы с лева на право от ключа, буквами латинского алфавита от A до W , а строки снизу вверх арабскими цифрами от 1 до 21.

Структурная схема МП Pentium

В структуре можно выделить 2 целочисленных конвейера (2 АЛУ), устройство с плавающей запятой, КЭШ памяти данных и команд, УУ, управление ПЗУ, буфер предварительной выборки, дешифратор команд, буфер предсказания перехода, устройство страничного преобразования, шинное устройство и др.

Два целочисленных конвейера аналогичны друг другу по структуре и порядку функций. В них конвейерный режим, как и в 486 МП реализован 5ти ступенях:

предварительная выборка (PF)

декодирование (D1)

Генерация адреса (D2)

Исполнение (EX)

Обратная запись, результат.(WB)

На первой ступени (PF) команда выбирается из КЭШ памяти или ОЗУ наличие независимых КЭШей данных и команд, исключает конфликты при выборке из памяти.

Два независимых буфера предварительной выборки по 32 байта работают совместно со схемой предсказания переходов.

На ступени D1 выполняется декодирование для запуска 1 или 2 команд одновременно.

Вычисление адресов операндов размещенных в памяти реализуется на ступени D2

На ступени ЕХ команды исполняются в АЛУ

На последней ступени WB фиксируется результат выполненной команды ( обратная запись )

Если на ступени ЕХ происходит задержка выполнения команды в одном из двух конвейеров – последующие команды не поступают пока на обоих конвейерах не завершиться.переход команд на ступень WB

Две КЭШ-памяти данных и команд по 8 кб каждая, реализованы по ассоциативной организации. И выдает информацию из памяти строками по 32 байта, что дает возможность при поиске информации просматривать ее последовательно по 2 строки.

Дешифратор команд преобразует коды выбранных команд для последующего их исполнения на конвейерах.

Управляющее ПЗУ осуществляет непосредственное управление работой двух конвейеров.

Устройство с плавающей запятой позволяет выполнять операции над мантиссами и порядками чисел за 1 такт и так же использует конвейерный режим. Однако выполнение операция в устройстве с плавающей запятой происходит за 8 ступеней.

Ступени 1-4 аналогичны целочисленным конвейерам, кроме того, реализуются операции над порядками, нормализуется результат, округление, сообщения об ошибках

Шинное устройство обеспечивает поддержку нескольких режимов шины в том числе. Групповую передачу данных, изменение длины передаваемых кодов.

Набор регистров МП Pentium аналогичен набору регистров МП Intel 80486

В МП Pentium имеется 16 регистров доступных программисту в том числе

1) 32-разрядные РОНы 8 шт.

2) флаги

3) сегментные регистры (16 бит.) хранящие коды для составления сегментных базовых адресов при обращении в память системы.

В наборе команд микропроцессора добавлены 3 новые прикладные команды. И 4 системные. Они обеспечивают возможности тестирования и отладки. Интерфейс шины МП Pentium близок к шинному интерфейсу МП 486 (расширенная ШД).