- •1)Дизъю́нкция

- •2) Конъю́нкция

- •3) Инверсия

- •4) Переместительный закон

- •5)Сочетательный закон

- •6. Распределительный закон

- •7.Законы поглощения

- •8. Правило склеивания

- •9. Правило де Моргана

- •10.Стрелка Пирса

- •13. Транзисторные ключи

- •14. Электронная логическая схема операции не.

- •15. Электронная логическая схема операции или

- •18. 19Схема на логических элементах – мультивибратор.

- •20.Схема на логических элементах – одновибратор.

- •21. Схема на логических элементах – мультивибратор.

- •25. Схема на логических элементах – синхронный rs-триггер

- •26.Схема на логических элементах – d-триггер.

- •27.Схема на логических элементах – синхронный jk-триггер.

- •28.Схема на логических элементах – dv-триггер

- •29.Типовой узел цифровых устройств – регистр.

- •30.Типовой узел цифровых устройств – счетчик импульсов.

- •31.Типовой узел цифровых устройств – сумматор.

- •32.Регистр состояния status микроконтроллера pic16f877

- •33. Организация памяти микроконтроллера pic16f877.

- •35.Использование тактового генератора для микроконтроллера pic16f877.

- •44.Характеристика микроконтроллера pic16f877.

- •45.Отладочные средства микроконтроллера pic16f877

- •47. Флаги регистров специального назначения.

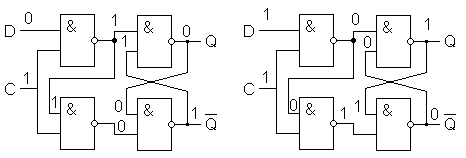

26.Схема на логических элементах – d-триггер.

Триггером называется устройство, обладающее двумя состояниями устойчивого равновесия и способное под воздействием внешнего управляющего сигнала переходить скачком из одного состояния в другое.

D-триггер (рис.10) имеет в своем составе 4 логических элемента И-НЕ, два из которых образуют простой RS-триггер, а входные подключены к клеммам D (вход приема информации) и С (вход синхронизации). При С=0, как и в синхронном триггере, на выходах входных элементов установятся уровни логической 1. Для выходного RS-триггера это режим хранения.

Рис. 10. Схема D-триггера на логических элементах И-НЕ

Независимо от состояния входа D на выходе информация не меняется (Qt+1=Qt). При С=1 информация со входа D переписывается на выход Q (Q t+1 = D t). Проследить за состояниями сигналов во всех точках схемы D-триггера при D=0 и D=1 можно по рис. 11.

Рис. 11. Распределение сигналов в D-триггере при D=0 (слева) и D=1 (справа)

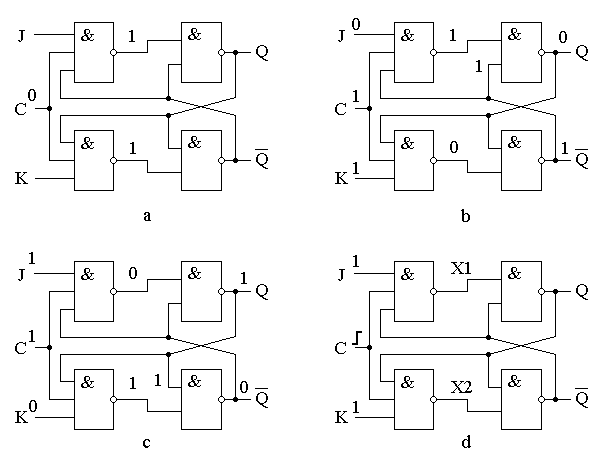

27.Схема на логических элементах – синхронный jk-триггер.

Простейший JK-триггер (рис. 2.9) на четырех логических элементах И-НЕ имеет три входа: вход синхронизации С и два логических входа J и K. При С=0 (рис. 2.9,а) на входах выходного RS-триггера уровни логической единицы, что соответствует режиму хранения информации. При С=1 состояние триггера зависит от уровней напряжения на входах J и K. В случае J=0 и K=1 (рис. 2.9,b) триггер устанавливается в нулевое состояние, а при J=1 и K=0 (рис. 2.9,с) – в единичное. Сравнивая с синхронным RS-триггером, можем заключить, что входы J и K аналогичны входам S и R. Однако при J=1 и K=1 (рис. 2.9,d) JK-триггер ведет себя иначе. В этом случае при положительном скачке напряжения на входе С триггер переключается в противоположное состояние. Процесс переключения можно объяснить с помощью уравнений состояния триггера:

При скачке напряжения на входе С (С=0 C=1) получаем: , . При и . Ноль на инверсном выходе получается при учете, что на прямом выходе уже установился уровень логической единицы. При достаточно коротком импульсе на входе С триггер при каждом таком импульсе будет переключаться только один раз. Но при продолжительном импульсе синхронизации триггер будет непрерывно переключаться, т.е. перейдет в режим генерации.

Рис. 2.9. Схема JK-триггера при различных состояниях входов.

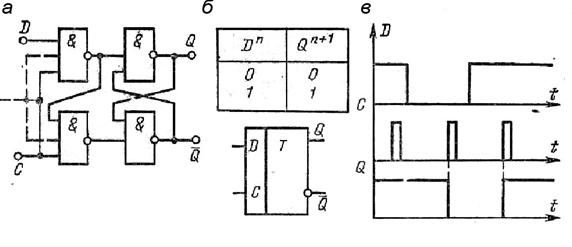

28.Схема на логических элементах – dv-триггер

D-тpиггep имеет один информационный вход (D-вход) и вход для синхронизирующего импульса (рис. 2.4). Основное назначение D-триггера – задержка сигнала, поданного на вход. Как и RS-триггер, он может быть построен на различных логических элементах. Видно, что при С = 0 изменение входного сигнала не сказывается на состоянии триггера, и только при С = 1 триггер принимает состояние, определяемое входным сигналом.

Разновидностью D-триггера является DV-триггер, который дополнительно к D-входу имеет управляющий V-вход (на рис. 2.4, а показан пунктирной линией). При V = 1 триггер работает аналогично D-триггеру, а при V = 0 сохраняет исходное состояние независимо от изменения сигнала на D-входе и С-входе.

Широкое применение в практике построения цифровых устройств находят D-триггеры с динамическим управлением (155TM2 564ТМ2). Они реагируют на информационные сигналы только в момент изменения сигнала на С-входе от 0 к 1 (прямой динамический вход) или от 1 к 0 (инверсный динамический вход).

Рис. 2.4. D-триггер (DV-триггер при наличии V-входа): а – функциональная схема; б – таблица состояний; в – условное обозначение; г – временные диаграммы