- •1)Дизъю́нкция

- •2) Конъю́нкция

- •3) Инверсия

- •4) Переместительный закон

- •5)Сочетательный закон

- •6. Распределительный закон

- •7.Законы поглощения

- •8. Правило склеивания

- •9. Правило де Моргана

- •10.Стрелка Пирса

- •13. Транзисторные ключи

- •14. Электронная логическая схема операции не.

- •15. Электронная логическая схема операции или

- •18. 19Схема на логических элементах – мультивибратор.

- •20.Схема на логических элементах – одновибратор.

- •21. Схема на логических элементах – мультивибратор.

- •25. Схема на логических элементах – синхронный rs-триггер

- •26.Схема на логических элементах – d-триггер.

- •27.Схема на логических элементах – синхронный jk-триггер.

- •28.Схема на логических элементах – dv-триггер

- •29.Типовой узел цифровых устройств – регистр.

- •30.Типовой узел цифровых устройств – счетчик импульсов.

- •31.Типовой узел цифровых устройств – сумматор.

- •32.Регистр состояния status микроконтроллера pic16f877

- •33. Организация памяти микроконтроллера pic16f877.

- •35.Использование тактового генератора для микроконтроллера pic16f877.

- •44.Характеристика микроконтроллера pic16f877.

- •45.Отладочные средства микроконтроллера pic16f877

- •47. Флаги регистров специального назначения.

44.Характеристика микроконтроллера pic16f877.

Характеристика вычислительного ядра МК:

выполнено по высокоскоростной RISC технологии. Высокая производительность достигается за счет применения конвейерной архитектуры и малого числа команд (всего 35);

тактовая частота МК составляет 20МГц, при этом время длительности машинного цикла достигает 200 нс;

8Кх14 слов FLASH памяти программ;

368х8 байт памяти данных (ОЗУ);

256х8 байт EEPROM памятью данных;

систему прерываний (14 источников).

Характеристика периферийных модулей:

два 8-разрядных таймера/счетчика;

один 16-разрядный таймер/счетчик с возможностью подключения внешнего резонатора;

два модуля захват/сравнение/ШИМ:

16-разрядный захват (максимальная разрешающая способность 12.5нс);

16-разрядный сравнение (максимальная разрешающая способность 200нс);

10 разрядный ШИМ;

8-канальное 10-разрядное АЦП;

последовательный синхронный порт;

ведущий/ведомый режим SPI;

ведущий/ведомый режим I2C;

последовательный асинхронный приемопередатчик USARTc поддержкой детектирования адреса;

ведомый 8-разрядный параллельный порт PSP с поддержкой внешних сигналов #RD, #WR, #CS.

45.Отладочные средства микроконтроллера pic16f877

Симулятор PDS-PIC представляет собой программно-логическую модель микроконтроллера, имитирующую (симулирующую) работу всех его узлов - памяти, АЛУ, системы команд, регистров, периферийных устройств и т.д. Возможности PDS-PIC:

отслеживание выполнения программы по ее исходному тексту;

просмотр и изменение значений любых переменных;

встроенный анализатор эффективности программного кода;

точки останова по сложному условию;

неограниченное количество точек останова по доступу к ячейкам памяти;

просмотр стека вызовов подпрограмм и функций;

встроенный строчный ассемблер;

возможность выполнения программы "назад" на большое количество шагов, а также в непрерывном режиме. При этом состояние модели микроконтроллера полностью восстанавливается;

точный подсчет интервалов времени и многое другое.

Основные достоинства программно-логической модели микроконтроллера, реализованной в PDS-PIC - точная симуляция узлов микроконтроллера и возможность моделировать устройства, подключенные к микроконтроллеру "снаружи" (т.н. моделирование внешней среды), например, внешнюю логику, датчики, клавиатуру, исполнительные устройства (дисплеи), задавать периодические и непериодические воздействия и т.п.

46.

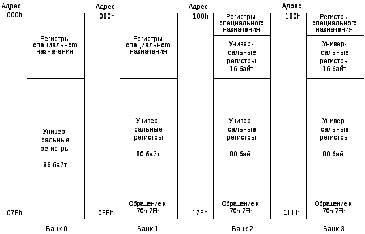

Память данных разделена на четыре банка, которые содержат регистры общего и специального (SFR) назначения. Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками данных. В таблице 1 показано состояние управляющих битов при обращении к банкам памяти данных.

Таблица 1. Обращение к банкам памяти данных

|

RP1 |

RP0 |

Банк |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

Объем банков памяти данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения выполненные как статическое ОЗУ. Все банки содержат регистры специального назначения. Часто используемые регистры специального назначения отображаться в других банках памяти. Старшие 16 байт памяти данных в банках 1, 2 и 3 отображены в банке 0.

Рис.4. Структура памяти данных