- •1)Дизъю́нкция

- •2) Конъю́нкция

- •3) Инверсия

- •4) Переместительный закон

- •5)Сочетательный закон

- •6. Распределительный закон

- •7.Законы поглощения

- •8. Правило склеивания

- •9. Правило де Моргана

- •10.Стрелка Пирса

- •13. Транзисторные ключи

- •14. Электронная логическая схема операции не.

- •15. Электронная логическая схема операции или

- •18. 19Схема на логических элементах – мультивибратор.

- •20.Схема на логических элементах – одновибратор.

- •21. Схема на логических элементах – мультивибратор.

- •25. Схема на логических элементах – синхронный rs-триггер

- •26.Схема на логических элементах – d-триггер.

- •27.Схема на логических элементах – синхронный jk-триггер.

- •28.Схема на логических элементах – dv-триггер

- •29.Типовой узел цифровых устройств – регистр.

- •30.Типовой узел цифровых устройств – счетчик импульсов.

- •31.Типовой узел цифровых устройств – сумматор.

- •32.Регистр состояния status микроконтроллера pic16f877

- •33. Организация памяти микроконтроллера pic16f877.

- •35.Использование тактового генератора для микроконтроллера pic16f877.

- •44.Характеристика микроконтроллера pic16f877.

- •45.Отладочные средства микроконтроллера pic16f877

- •47. Флаги регистров специального назначения.

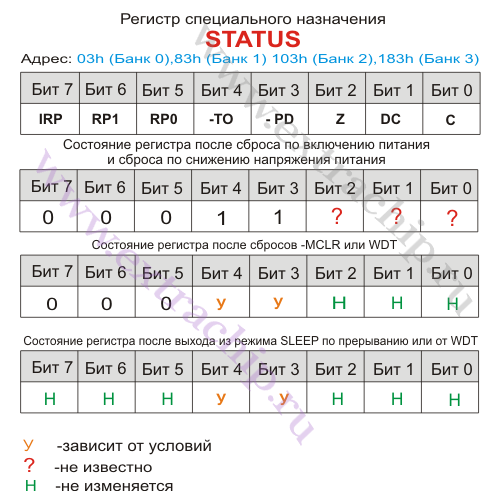

32.Регистр состояния status микроконтроллера pic16f877

Регистр STATUS отображается на все 4 банка микроконтроллера и имеет адреса: 03h (банк 0), 83h (банк 1), 103h (банк 2) и 183h (банк 3). В этом регистре находятся флаги состояния АЛУ, флаги причины сброса микроконтроллера и биты управления банками RAM памяти данных микроконтроллера. Если обращение к регистру STATUS выполняется командой, которая воздействует на флаги Z, DC и C, то изменение этих трех битов заблокировано. Эти биты сбрасываются или устанавливаются согласно логике ядра микроконтроллера. Команды изменения регистра STATUS также не воздействуют на биты –TO и –PD, которые доступны только для чтения. Для изменения битов регистра STATUS рекомендуется использовать команды, не влияющие на флаги АЛУ такие, как SWAPF, MOVWF, BCF и BSF. Используются все 8 битов этого регистра. На рисунке №1 показаны обозначения битов регистра и состояние регистра после всех видов сброса.

Рис.1

Рис.1

IRP – бит выбора банка при косвенной адресации. При IRP=1 выбирается банк 2 или 3; при IRP=1 выбирается банк 0 или 1. Бит доступен для чтения и записи.

RP1:RP0 – биты выбора банка при непосредственной адресации (11- банк 3; 10 – банк 2; 01 – банк 1; 00 – банк 0). Биты доступны для чтения и записи.

- TO – флаг переполнения сторожевого таймера. После сброса по включению питания POR или выполнения команд CLRWDT, SLEEP бит установлен в 1. После переполнения сторожевого таймера сбрасывается в 0. Этот бит доступен только для чтения.

- PD – флаг включения питания. После POR или выполнения команды CLRWDT бит установлен в 1. После выполнения команды SLEEP бит сбрасывается в 0. Этот бит доступен только для чтения.

Z – флаг нулевого результата. При нулевом результате выполнения логической или арифметической операции устанавливается в 1. При ненулевом результате выполнения логической или арифметической операции устанавливается в 0. Бит доступен для записи и чтения.

DC – флаг десятичного переноса/заема (для команд: ADDWF, ADDWL, SUBWF, SUBWL), заем имеет инверсное значение. В случае переноса из младшего полубайта бит устанавливается в 1. В случае отсутствия переноса из младшего полубайта бит сбрасывается в 0.

C – Флаг переноса/заема (для команд ADDWF, ADDWL, SUBWF, SUBWL), заем имеет инверсное значение. В случае переноса из старшего бита флаг устанавливается в 1. . В случае отсутствия переноса из старшего бита флаг сбрасывается в 0.

33. Организация памяти микроконтроллера pic16f877.

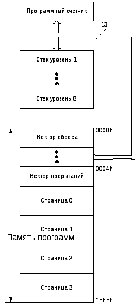

Структура памяти команд показана на рис.3.

Микроконтроллеры PIC16F877 имеет 13-разрядный программный счетчик ПС, способный адресовать 8К х 14 бит памяти программ.

Адрес вектора сброса - 0000h.

Адрес вектора прерываний - 0004h.

Рис.3. Структура памяти программ и стека

Организация памяти данных

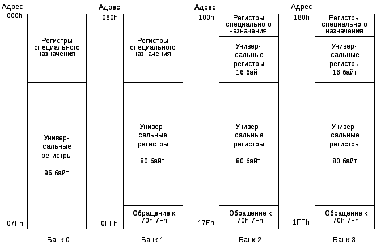

Структура памяти данных показана на рис.4.

Память данных разделена на четыре банка, которые содержат регистры общего и специального (SFR) назначения. Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками данных. В таблице 1 показано состояние управляющих битов при обращении к банкам памяти данных.

Таблица 1. Обращение к банкам памяти данных

|

RP1 |

RP0 |

Банк |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

Объем банков памяти данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения выполненные как статическое ОЗУ. Все банки содержат регистры специального назначения. Часто используемые регистры специального назначения отображаться в других банках памяти. Старшие 16 байт памяти данных в банках 1, 2 и 3 отображены в банке 0.

Рис.4.

Структура памяти данных