- •1)Дизъю́нкция

- •2) Конъю́нкция

- •3) Инверсия

- •4) Переместительный закон

- •5)Сочетательный закон

- •6. Распределительный закон

- •7.Законы поглощения

- •8. Правило склеивания

- •9. Правило де Моргана

- •10.Стрелка Пирса

- •13. Транзисторные ключи

- •14. Электронная логическая схема операции не.

- •15. Электронная логическая схема операции или

- •18. 19Схема на логических элементах – мультивибратор.

- •20.Схема на логических элементах – одновибратор.

- •21. Схема на логических элементах – мультивибратор.

- •25. Схема на логических элементах – синхронный rs-триггер

- •26.Схема на логических элементах – d-триггер.

- •27.Схема на логических элементах – синхронный jk-триггер.

- •28.Схема на логических элементах – dv-триггер

- •29.Типовой узел цифровых устройств – регистр.

- •30.Типовой узел цифровых устройств – счетчик импульсов.

- •31.Типовой узел цифровых устройств – сумматор.

- •32.Регистр состояния status микроконтроллера pic16f877

- •33. Организация памяти микроконтроллера pic16f877.

- •35.Использование тактового генератора для микроконтроллера pic16f877.

- •44.Характеристика микроконтроллера pic16f877.

- •45.Отладочные средства микроконтроллера pic16f877

- •47. Флаги регистров специального назначения.

31.Типовой узел цифровых устройств – сумматор.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры. Сумматоры классифицируют по различным признакам. В зависимости от системы счисления различают:

-двоичные; -двоично-десятичные (в общем случае двоично-кодированные); -десятичные; -прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел: -одноразрядные, -многоразрядные.

Сумматоры - это цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие – запоминающие результаты вычислений при снятии входных сигналов. В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС.

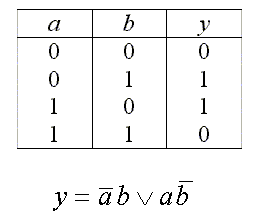

Сумматор по модулю два - Это устройство с двумя входами (а и b), на выходе у которого сигнал "1" появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. "0" и "1". Сумматор не обладает памятью.

Eго таблица истинности и логическое уравнение имеют вид:

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

Рис. 21. Реализация сумматора по модулю два:а – принципиальная схема; б – функциональная схема

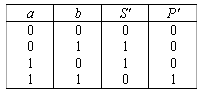

Полусумматор - Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b. Так как при a = 1 и b = 1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого - сигнал переноса.

Таблица истинности полусумматора и его логические уравнения имеют вид:

![]()

P' = ab

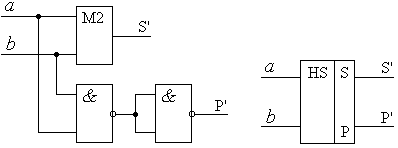

Реализация полусумматора в базисе И–НЕ представлена на рис. 22

а б

Рис. 22. Схема полусумматора:а – реализация в базисе И–НЕ; б – условное обозначение

Условное обозначение полусумматора на схемах – HS (halfsum – полусумма), а полного сумматора – SM.

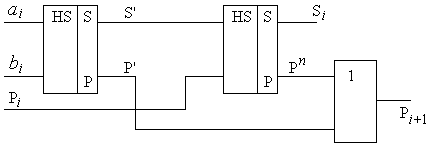

Полный сумматор - Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c - сигнал переноса из предыдущего младшего разряда. Имеет два выхода S (сумма) и Р (перенос).

Полный сумматор можно построить из двух полусумматоров (рис. 23), отсюда и название – полусумматор, используя следующие логические уравнения

![]()

![]()

Рис. 23. Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел. В цифровой схемотехнике операцию вычитания обычно заменяют сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, поэтому вычитатели могут быть выполнены на основе сумматоров.

32.Типовой узел цифровых устройств – дешифратор Шифраторы – это устройства сжатия информации. Они преобразуют M-разрядный код с KM избыточными состояниями (безразличными) в N-разрядный с KN безразличными состояниями, N < M, KN < KM. Обратное преобразование – дешифрация. Обычно говорят «шифратор из M в N», если осуществляется преобразование M-разрядного кода в N-разрядный. Шифраторы служат для сжатия информации при обмене между различными устройствами, при вводе с клавиатуры шестнадцатеричных, десятичных, восьмеричных цифр.

Дешифратор - Комбинационное устройство, позволяющее преобразовать n-разрядный двоичный код в позиционный 2n-разрядный код. Имеет n входов и 2n или меньше выходов. В зависимости от входного набора сигнал 1 появится только на одном определенном выходе, а на всех остальных выходах будут сигналы 0.

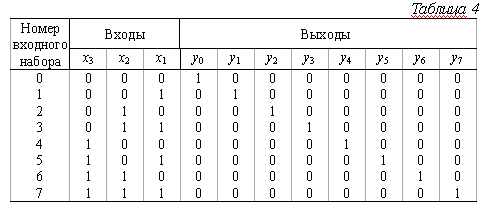

Таблица истинности полного дешифратора на три входа имеет вид (табл.4):

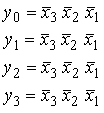

Логические функции выходов дешифратора:

По способу реализации дешифраторы могут быть линейные, прямоугольные и пирамидальные.

Более совершенными являются пирамидальные дешифраторы, относящиеся к многоступенчатым структурам и содержащие ряд логических элементов для выделения общих частей функций.

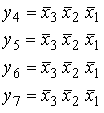

В ниже следующей таблице дана сравнительная оценка линейных, пирамидальных и прямоугольных дешифраторов по аппаратным затратам NЛЭ в пересчете на 2-входные ЛЭ для m-разрядного входного кода (табл. 5).

Как видно из таблицы 5, преимущества многоступенчатых дешифраторов заметно нарастают с увеличением m. В специализированных ИС тем не менее предпочтение часто отдают более простым линейным (одноступенчатым) дешифраторам, обладающим к тому же повышенным быстродействием.