- •Содержание

- •1. Общие сведения

- •1.1. Системы счисления

- •2. Цифровая логика

- •2.2. Булева алгебра

- •2.3. Цифровые интегральные схемы

- •2.4. Триггеры

- •2.5 Сдвиговые регистры

- •2.6 Выходные буферные схемы

- •2.7 Счетчики

- •2.8 Сумматоры

- •2.9 Дешифраторы

- •2.10 Мультиплексоры

- •2.11 Шифраторы

- •3. Память

- •3.1 Постоянные запоминающие устройства

- •3.2 Оперативные запоминающие устройства

- •4. Ацп и цап

- •4.1 Общие сведения

- •4.2 Электрические параметры, эксплуатационные характеристики ацп и цап

- •4.3 Классификация ацп

- •4.4 Классификация цап

2.3. Цифровые интегральные схемы

Логические элементы, могут быть выполнены в виде интегральных схем (ИС). Интегральные схемы имеют значительное преимущества перед схемами на дискретных элементах по габаритам, потребляемой мощности и стоимости. В одном корпусе ИС может быть размещено большое количество логических элементов при условии незначительной величины потребляемой мощности.

Транзисторы как элементы цифровой логики

Транзисторы являются базовыми элементами большинства типов ИС. Они используются и как дискретные элементы при сопряжении логических устройств. При изготовлении ИС применяют два основных вида транзисторов: биполярные транзисторы и полевые МОП-транзисторы .

Биполярные транзисторы бывают двух типов: р—п—риn—р—n. Как логический элемент транзистор может находиться либо в открытом (проводящем) состоянии, либо в закрытом (непроводящем) состоянии. Транзисторр—п—р типа закрыт, если его база(Б)имеет более положительный потенциал, чем потенциал эмиттера(Э),и открыт, если потенциал базы более отрицательный, чем потенциал эмиттера. На коллектор(К)подается отрицательное напряжение по отношению к эмиттеру. Тогда ток (движение положительных зарядов) в данном транзисторе имеет направление от эмиттера к коллектору. Величина напряжения база — эмиттер, необходимая для переключения транзистора из закрытого в полностью открытое состояние (состояние насыщения), колеблется в пределах от -0,1 до -0,7 В, Транзисторп—р—п типа закрыт, если его база имеет более отрицательный потенциал, чем эмиттер, и открыт, если потенциал базы более положительный, чем потенциал эмиттера. На коллектор подается положительное напряжение относительно эмиттера, и ток в этом транзисторе протекает от коллектора к эмиттеру. Величина напряжения база— эмиттер, необходимая для переключения транзистора из закрытого состояния в открытое, составляет 0,1—0,7 В.

Одной

из возможных схем включения биполярного

транзистора является схема с общим

эмиттером (рис. 2.14). НапряжениеEnменьше или больше нуля дляр—п—рип—р—nтранзисторов

соответственно. При такой схеме включения

сигнал логической переменнойА,подаваемый на вход, преобразуется на

выходе в![]() ,

и таким образом схема реализует

операцию инвертирования. Отрицательное

напряжение, подаваемое на вход данной

схемы, открываетр—п—р транзистор,

положительное напряжениеп—р—п

транзистор. При подаче на БАЗУ

транзистора напряжение высокого уровня,

что соответствует логической ЕДИНИЦЕ,

транзистор закрывается, ток от эмиттера

к коллектору не течет, на выходе логический

НОЛЬ.

,

и таким образом схема реализует

операцию инвертирования. Отрицательное

напряжение, подаваемое на вход данной

схемы, открываетр—п—р транзистор,

положительное напряжениеп—р—п

транзистор. При подаче на БАЗУ

транзистора напряжение высокого уровня,

что соответствует логической ЕДИНИЦЕ,

транзистор закрывается, ток от эмиттера

к коллектору не течет, на выходе логический

НОЛЬ.

Рис. 2.14. Включение биполярного транзистора по схеме с общем эмиттером.

При отсутствии потенциала на базе транзистора, ток течет от эмиттера к коллектору на выходе ЕДИНИЦА.

Полевые МОП - транзисторы, относящиеся ко второй важной группе транзисторов также бывают двух типов: р-ип- канальные. Электронный ключ, собранный на р - канальном МОП -транзисторе, закрыт, если потенциал затвора (3) более положительный, чем потенциал истока (И), и открыт, если потенциал затвора более отрицательный. На сток (С) по отношению к истоку подается отрицательное напряжение, ток в транзисторе течет от истока к стоку.

В n- канальном МОП - транзисторе потенциал затвора, более отрицательный по сравнению с потенциалом истока, закрывает транзистор, а более положительный - открывает. На сток относительно истока подается положительное напряжение, ток в транзисторе направлен от стока к истоку. Подложка транзистора обычно электрически соединяется с истоком.

На рис. 2.15 показано включение р-илиn-канального МОП - транзистора по схеме собщим истоком.Данная схема аналогична схеме включения с общим эмиттерам для биполярного транзистора (рис. 2.14) и также реализует операцию инверсии логической переменной А. Как и в случае биполярного транзистора,р-иn– канальные полевые транзисторы обладают свойством двойственности.

Рис. 2.15. Инвертор на р – канальном МОП – транзисторе (схема с общим истоком).

Данная схема работает аналогично выше описанной схеме на биполярном транзисторе.

Диодно-транзисторная логика

Схемы диодно-транзисторной логики (DTL)являются наиболее известным классом логических схем. Эти схемы, как следует из названия, состоят из диодов и биполярных транзисторов. Базовым элементом диодно-транзисторной логики является схема И-НЕ (рис. 2.16).

Рис. 2.16. Стандартная схема DTL, выполняющая операцию И-НЕ.

Принцип работы такой схемы заключается в следующем. Если входы А и Внаходятся в состоянии 1, то ток, протекающий отEkчерезR1 и R2,открывает транзисторТ1.Ток, проходящий черезR1иT1,открываетТ2,и таким образом на выходе схемы устанавливается низкий потенциал. ЕслиА,илиВ,или оба входа находятся в состоянии 0, то ток протекает черезR2на «землю» иT1 закрыт. Следовательно, T2 также закрыт и на выходе устанавливается высокий потенциал. Описанная схема выполняет операцию И-НЕ для положительной логики. Схема, нагруженная на входАилиВи переключающая этот вход в состояние 0, должна «отбирать» ток, протекающий черезR2.Поэтому этот тип логических схем называетсясхемой с отбором тока.

Максимально

возможное количество входов схемы

называется коэффициентом объединения

по входу.Аналогичным образомкоэффициент разветвления по

выходу—это максимально возможное

количество входов схем того же типа,

которое может переключать выход данной

схемы. Обычно коэффициент объединения

по входу уDTL-схем10,

а коэффициент разветвления по выходу

равен 8. Номинальное напряжение питания

Еk=5В,потребляемая

мощность 10 мВт/элемент, задержка

переключения ~ 30 нс/элемент. На входе

схемы напряжения

![]() ,и

,и

![]() есть соответственно 1,2 и 2,0 В. На

выходе схемы

есть соответственно 1,2 и 2,0 В. На

выходе схемы

![]() и

и

![]() имеют значения 0,45 и 2,6 В.

имеют значения 0,45 и 2,6 В.

При рассмотрении любого типа логических схем необходимо учитывать защищенность схемы от воздействия помех. Защищенность схемы связана с двумя важными факторами — помехоустойчивостьюиуровнем наводимой помехи.Помехоустойчивость схемы определяется величиной сигнала помехи, который, накладываясь на входной логический сигнал, вызывает ошибочное переключение схемы. Относительно второго фактора известно, что (помехи наводятся в основном через шины питания при переключении логических схем.DTL-схемыобладают хорошей помехоустойчивостью и средним по величине уровнем наводимых помех.

Транзисторно-транзисторная логика

Широко

распространенный класс логических схем

— схемы транзисторно-транзисторной

логики (TTL, или

![]() ).

На входе таких схем находятся

многоэмиттерные транзисторы. На рис.

2.17 показана TTL-схема, реализующая операцию

И-НЕ для положительной логики.

).

На входе таких схем находятся

многоэмиттерные транзисторы. На рис.

2.17 показана TTL-схема, реализующая операцию

И-НЕ для положительной логики.

Рис. 2.17. Стандартная схема TTL, выполняющая операцию И–НЕ.

Схема работает следующим образом. Если входы А и В находятся в состоянии 1, то ток, протекающий от Ek черезR1, поступает на базуT2 через переход база — коллектор транзистораT1,смещенный в прямом направлении. Этот ток открывает транзисторT2, который переключает ток, протекающий черезR2,от базы транзистораT3 к базе транзистораT4.ТранзисторT3 запирается, а транзисторT4 входит в режим насыщения; при этом на выходе схемы устанавливается низкий потенциал (состояние 0). Далее, еслиАилиВ,или оба этих входа находятся в состоянии О, то ток черезR1 уходит («отбирается») на землю через переходT1. Следовательно,T2 закрыт,T3 открыт,T4 закрыт и на выходе устанавливается высокий потенциал (состояние 1). Эти логические схемы, так же как и схемыDTL,являются схемами с отбором тока.

Стандартные

TTL-схемы,например

серии 155, обычно имеют коэффициент

разветвления по выходу, равный 10, и

коэффициент объединения по входу 8.

Номинальные значения других параметров

следующие: напряжение источника питания

.Еп=5 В, потребляемая мощность 12

мВт/элемент, задержка 10 нс/элемент. Для

серии 1533 потребляемая мощность 2

мВт/элемент, задержка 4 нс/элемент.

Напряжения на входе схемы

![]() и

и

![]() соответственно равны 0,8 и 2,0 В, а напряжения

на выходе

соответственно равны 0,8 и 2,0 В, а напряжения

на выходе

![]() и

и

![]() – 0,4 и 2,4 В. Устройство, переключающее

схему TTL,должно—«отбирать» 1,6 мА в

состоянии 0 и 40 мкА в состоянии 1. Этим

определяетсянагрузочная способность

элемента TTL.

– 0,4 и 2,4 В. Устройство, переключающее

схему TTL,должно—«отбирать» 1,6 мА в

состоянии 0 и 40 мкА в состоянии 1. Этим

определяетсянагрузочная способность

элемента TTL.

Другой

важный параметр, связанный с

помехоустойчивостью, — запас

помехоустойчивости по постоянному

напряжению. Запас помехоустойчивости

— есть разность между выходным и входным

напряжениями для худшего случая. Когда

выход элемента связан со входом другой

такой же схемы, существует запас по

напряжению

![]() ,

удерживающий управляемую схему в

нулевом состоянии.

,

удерживающий управляемую схему в

нулевом состоянии.

![]() называетсязапасом помехоустойчивости в нулевом

состоянии.(Ясно, что для схемы,

удерживаемой в нулевом состоянии,

необходим сигнал .помехи, по крайней

мере равный

называетсязапасом помехоустойчивости в нулевом

состоянии.(Ясно, что для схемы,

удерживаемой в нулевом состоянии,

необходим сигнал .помехи, по крайней

мере равный

![]() на входе, чтобы ошибочно изменить

ее состояние.) Аналогичнозапас

устойчивости для единичного состояниясхемы определяется как

на входе, чтобы ошибочно изменить

ее состояние.) Аналогичнозапас

устойчивости для единичного состояниясхемы определяется как

![]() .Для стандартной TTL-схемы типичные

значения

.Для стандартной TTL-схемы типичные

значения

![]() и

и

![]() составляют 0,4 В. Помехоустойчивость

этого типа схем считается очень хорошей,

а величина наводимой помехи—выше

средней.

составляют 0,4 В. Помехоустойчивость

этого типа схем считается очень хорошей,

а величина наводимой помехи—выше

средней.

При помощи TTL–cxeм,выполненных на основе технологии МИС, можно реализовать большое количество различных операций. Наряду со стандартными TTL-схемами имеются специальные схемы, которые включаютмаломощные TTL-схеми, быстродействующие TTL-схемы, схемы, с диодами Шоттки, маломощные TTL- схемы, с диодами Шоттки.Маломощные ТТLсхемы характеризуются потребляемой мощностью 1 мВт/элемент и задержкой 33 нс/элемент. БыстродействующиеTTLимеют задержку 6 нс и потребляемую мощность 22 мВт/элемент.TTL-схемыс диодами Шоттки и маломощные TTL-схемы с диодами Шоттки имеют задержку соответственно 3 и 10 нс/элемент, а потребляемые мощности 22 и 2 мВт/элемент.

Рекомендации по применению TTL микросхем.

Все ИС ТТЛ по логическим уровням напряжения совместимы друг с другом. Однако по нагрузочной способности ИС различных серий имеют различия. Превышение нагрузочной способности по отношению к заданной техническим условиям приводят к ухудшению других параметров ИС: снижению быстродействия, увеличению потребляемой мощности, ухудшению помехоустойчивости и надежности. Для обеспечения большого тока в серии К155, К555, Е531 введены схемы с повышенной нагрузочной способностью как с двухтактным выходом (типа К155ЛА6, К555ЛА6, К155ЛА12 и др.), так и с открытым коллектором. В качестве коллекторного резистора в схемах с открытым коллектором может быть использован внешний резистор от 500 Ом до 1 кОм.

Неиспользуемые входы можно оставлять не подключенными при этом уровень на таком входе воспринимается как логическая 1 или подключать к источнику питания через резистор 1 кОм, для формирования логического 0 соответствующий вход подключают к «земле».

Логические схемы с эмиттерными связями

В стандартных TTL- схемах переход из одного состояния в другое требует переключения выходного транзистора, включенного по схеме с общим эмиттером, в состояние насыщения или выхода его из этого состояния. Когда транзистор переключается в состояние насыщения, базовая область насыщается неосновными носителями. Чтобы выключить транзистор, требуется время на удаление неосновных носителей, что ограничивает быстродействие схемы. Логические схемы, работающие в активной зоне между областями насыщения и отсечки, называютсясхемами с эмиттерными связями или ЭСЛ-схемами.

Стандартная схема ЭСЛпоказана на рис. 2.18. Она состоит из дифференциального усилителя, цепи смещения и эмиттерного повторителя на выходе. Цепь смещения работает таким образом, чтоT3 открыт, еслиА и Внаходятся в состоянии 0(T1 иT2 закрыты). При этомT4 заперт и на выходе устанавливается низкий потенциал (состояние 0). Если жеAили В имеют высокий потенциал (состояние 1), то транзисторT1 илиT2 открыт и ток, протекающий черезT3,уменьшается, вызывая увеличение потенциала коллектора. Это приводит к отпираниюT4 и установлению высокого потенциала (состояния 1) на выходе. Такая работа схемы соответствует операции ИЛИ. Если на выходе схемы стоит дополнительный эмиттерный повторитель и его база связана с коллекторомT2, то схема реализует операцию ИЛИ-НЕ. По этой причине типовыми схемамиЭСЛобычно считают схемы ИЛИ и ИЛИ-НЕ.

Рис. 2.18. Стандартная схема ЭСЛ.

В

стандартных схемах ЭСЛ коэффициент

объединения по входу и коэффициент

разветвления по выходу обычно имеют

значения 5 и 50 соответственно, напряжения

источников питания Ек=0иЕэ= -5,2

В, номинальные значения .потребляемой

мощности 25 мВт/элемент, задержка 2

нс/элемент,

![]() =

- 1,85 В,

=

- 1,85 В,

![]() =

- 0,810 В,

=

- 0,810 В,

![]() =

-l,65 В и

=

-l,65 В и

![]() = - 0,96 В. Помехоустойчивость схем считается

удовлетворительной (запас помехоустойчивости

= - 0,96 В. Помехоустойчивость схем считается

удовлетворительной (запас помехоустойчивости

![]() =0,2

В и

=0,2

В и

![]() =0,15

В), величина наводимой помехи ниже

средней величины. Рассмотренный класс

схем реализует довольно широкий набор

различных функций и обладает такими

достоинствами, как малое время переключения

(задержка по меньшей мере на порядок

меньше, чем в TTL-схемах) и незначительные

переходные процессы в цепях питания;

обеспечивается также возможность

совместной работы со схемамиTTL.

=0,15

В), величина наводимой помехи ниже

средней величины. Рассмотренный класс

схем реализует довольно широкий набор

различных функций и обладает такими

достоинствами, как малое время переключения

(задержка по меньшей мере на порядок

меньше, чем в TTL-схемах) и незначительные

переходные процессы в цепях питания;

обеспечивается также возможность

совместной работы со схемамиTTL.

Наибольшее распространение ЭСЛ микросхем получило серия К1500 и К500. Логические элементы в микросхемах К1500 имеют типовое время задержки сигнала при переключении менее 1 нс.

Рекомендации по применению ЭСЛ микросхем.

Одной из главных задач при проектировании устройств на ИС серии ЭСЛ является обеспечение их устойчивой работоспособности в реальных условиях при воздействии внешних факторов, К основным дестабилизирующим фактором относится отклонения напряжения электропитания от номинального значения. Этот фактор снижает помехозащищенность спроектированной аппаратуры. Необходимо предусматривать влияния внешних факторов при работе на высоких частотах.

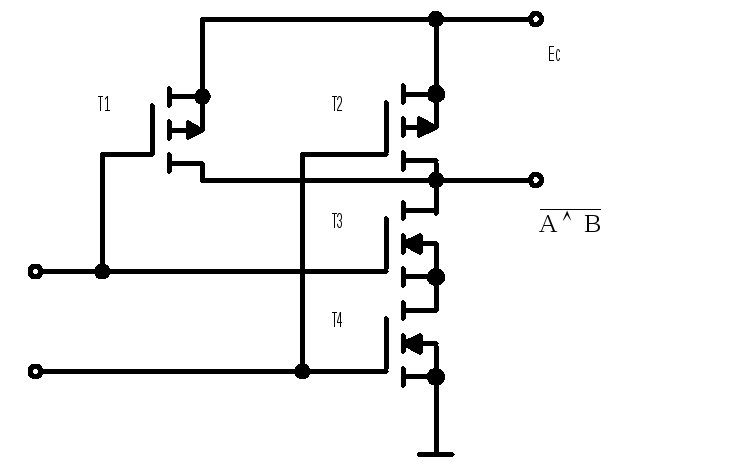

Комплементарная логика

Схемы комплементарной логики —это МОП-схемы, характеризующиеся низкой потребляемой мощностью и высокой помехоустойчивостью. Логические схемы этого типа изготавливают на базеn- иp-канальных МОП - транзисторов. Стандартная комплементарная МОП-схема (КМОП) представлена на рис. 2.19. Когда входыАиВимеют высокий потенциал (состояние 1),T1 иT2 закрыты, аT3 иT4 открыты и на выходе схемы низкий потенциал (состояние 0). Если жеАилиВ(или оба входа) находятся в состоянии 0, тоT1 иT2 открыты, аT3 иT4 закрыты и на выходе высокий потенциал (состояние 1). Таким образом, данная схема работает как схема И-НЕ. Если в этой схеме поменять местамир- иn- канальные транзисторы, то схема будет выполнять функцию ИЛИ-НЕ. Следовательно, стандартная КМОП - схема – это либо схема И-НЕ, либо схема ИЛИ-НЕ.

Рис. 2.19. Стандартная комплементарная МОП-схема, реализующая функцию И-НЕ.

В соответствии с рис. 2.19 А и Вявляются входами схемы на МОП-транзисторах. Так как их входное сопротивление порядка 1012Ом, то ток во входной цепи фактически не потребляется. В связи с тем, что один из двух транзисторов, связанных с каждым входом (т. е. Т1-Т3 и Т2-Т4),находится всегда в состоянии насыщения, выходное сопротивление низкое и коэффициент разветвления по .выходу высокий. Кроме того, в статическом режиме один транзистор в каждой из цепей, проходящих от Ес к земле (т. е. Т1-Т3 и Т2-Т4), всегда находится в режиме отсечки, поэтому нет утечки на землю. Потребляемая мощность связана лишь с утечкой в полевых МОП-транзисторах, которая в отдельных схемах составляет величину до нескольких нановатт. Однако в динамическом режиме паразитные емкости в схеме вызывают повышенное потребление мощности. При частоте переключения 1МГц потребляемая мощность может увеличиваться до 1 мВт/элемент.

Рекомендации по применению МОП-схем.

Интегральные схемы выполненные по МОП технологии менее критичны к напряжению электропитания. Напряжение питания для некоторых микросхем может колебаться в диапазоне от 3 до 15 вольт. Недопустимо оставлять входные сигналы незадействованными. Главным недостатком МОП-схем их низкое быстродействие, особенно при нагрузках на выходе имеющей емкостной характер.