- •Содержание

- •1. Общие сведения

- •1.1. Системы счисления

- •2. Цифровая логика

- •2.2. Булева алгебра

- •2.3. Цифровые интегральные схемы

- •2.4. Триггеры

- •2.5 Сдвиговые регистры

- •2.6 Выходные буферные схемы

- •2.7 Счетчики

- •2.8 Сумматоры

- •2.9 Дешифраторы

- •2.10 Мультиплексоры

- •2.11 Шифраторы

- •3. Память

- •3.1 Постоянные запоминающие устройства

- •3.2 Оперативные запоминающие устройства

- •4. Ацп и цап

- •4.1 Общие сведения

- •4.2 Электрические параметры, эксплуатационные характеристики ацп и цап

- •4.3 Классификация ацп

- •4.4 Классификация цап

3. Память

Команды и данные необходимо хранить и выбирать по мере надобности в процессе работы ЭВМ. Для этой цели применяют запоминающие устройства (ЗУ). Запоминающие устройства можно разделить на два типа – постоянные запоминающие устройства (ПЗУ) и оперативные запоминающие устройства (ОЗУ). ПЗУ используется для хранения команд и констант. Запись в ПЗУ сложна и занимает много времени, поэтому этот тип памяти применяется в ситуациях, когда не требуется изменять однажды записанную информацию, например в специализированных системах. Поскольку микро-ЭВМ в основном используется в подобных системах, в большинстве таких ЭВМ для хранения программ применяется только ПЗУ.

Оперативные запоминающие устройства используются для хранения данных, изменяющихся в процессе работы системы, например результатов вычислений или программ, которые часто меняются. Однако в функцию любого из рассмотренных типов памяти входят хранение данных и команд и обеспечение их выборки в процессе реализации программы.

В последующих разделах подробно рассматриваются постоянные и оперативные запоминающие устройства.

3.1 Постоянные запоминающие устройства

Для большинства микро-ЭВМ основным используемым типом памяти являются постоянные запоминающие устройства. Данный тип памяти также называют мертвой, фиксированной или долговременной памятью. Постоянное запоминающее устройство функционирует как .матрица памяти, для которой однажды полученное заполнение постоянно и не может быть изменено микропроцессором, использующим эту память.

Выключение электропитания не меняет содержимого ПЗУ. Большинство ПЗУ относится к устройствам памяти с произвольным доступом, в которых время доступа одинаково для всех ячеек памяти. То есть, говоря более строго, для устройства с произвольным доступом время доступа не зависит от адреса, по которому производится обращение.

Вследствие последних достижений в области технологий ИС наметилось несколько вариантов исполнения ПЗУ. Удобным средством классификации данных устройств является способ их программирования, позволяющий поделить все ПЗУ на три класса. К первому классу следует отнести ПЗУ, программируемые изготовителем по заказу пользователя. Такие устройства называют иногда ПЗУ с масочным программированием. В ПЗУ данного класса не допускается внесение изменений после их поставки.

Во второй класс входят ПЗУ, программируемые непосредственно пользователем. Подобные устройства часто называют программируемыми ПЗУ либо ПЗУ с программируемым полем и сокращенно называют ППЗУ. Обычно в ППЗУ используются плавкие связи, которые могут быть модифицированы пользователем. Однако, после того как устройство запрограммировано, содержимое его памяти остается постоянным, как и в ПЗУ первого класса.

К третьему классу относят ПЗУ, которое можно программировать повторно, такие устройства называют перепрограммируемые или полупостоянными. Перепрограммирование ПЗУ данного класса производится автономно с использованием электрических, оптических и других устройств.

Структурная

схема типичного постоянного запоминающего

устройства приведена на рис. 3.1. Здесь

дешифратором адреса памяти является

комбинационная схема, которая по

требуемому одному из Nвозможных адресов открывает доступ к

соответствующемуM–

разрядному слову в матрице памятиMxN,

содержимое этихMразрядов

затем передается в выходной буферный

усилитель для последующего использования

в системе. При генерированииNвозможных комбинаций (адресов) дешифратор

адреса памяти должен иметьpвходных зажимов (![]() )

т.е. необходимpразрядный

вход. Матрица памятиMxNсодержит постоянно хранимую комбинацию

двоичных знаков. Выходной буферный

усилитель формируетM–

разрядный выход.

)

т.е. необходимpразрядный

вход. Матрица памятиMxNсодержит постоянно хранимую комбинацию

двоичных знаков. Выходной буферный

усилитель формируетM–

разрядный выход.

Общую схему рис 3.1 можно реализовать при помощи двух схем адресации, называемых линейной выборкой и выборкой по принципу совпадения токов. Схема линейной выборки, как наиболее простая, в основном применяется в ПЗУ небольшого объема (например, в преобразователях кодов), тогда как в ПЗУ большого объема применяют схему выборки по принципу совпадения токов.

Рис. 3.1 Структурная схема ПЗУ

Адресация по принципу линейной выборки

ПЗУ можно характеризовать по способу адресации матрицы памяти, которая осуществляется дешифратором адреса памяти. В ПЗУ, использующих линейную выборку, дешифратор адреса памяти, показанный на рис 3.1, как правило, является дешифратором типа 1 из N. Выходной сигнал дешифратора отпирает одну изNчисловых линий, каждая из которых несетMдвоичных разрядов информации. Двумерная матрица памятиMxNподобной структуры называется прямоугольной.

Когда происходит обращение к памяти, дешифратор адреса памяти подает напряжение (состояние 1) на соответствующую числовую линию (одну из N). На каждую разрядную линию, соединенную с данной числовой линией элементом связи, подается напряжение возбуждения, что соответствует состоянию 1 для этой линии. Разрядные линии, на пересечении которых с числовой линией отсутствуют элементы связи, находится в состоянии 0.

Рис. 3.2. Резистивное ПЗУ с линейной выборкой

Различные

варианты ПЗУ с линейной выборкой

отличаются в основном типом используемых

элементов связи. В простейших ПЗУ

применяются пассивные схемные элементы

– резисторы и конденсаторы. В случае

больших матриц при использовании

резисторов возникает ряд проблем,

связанных с явлением затухания сигнала.

Рассмотрим, например, резистивную

матрицу 4х4, показанную на рисунке 3.2.

Состояние дешифратора приведено для

состояния входного сигнала 10, который

активирует числовую линию W2.

В результате на выходе получатся значения

1011. Входное напряжение, подаваемое на

буферный усилитель от разрядной линииB0, есть результат

деления напряжения считыванияVмежду резисторамиR1иR2. Поскольку все

резисторы одинаковы, это напряжение

равно

![]() .

.

Рассмотрим

теперь разрядную линию B1.

В данном случае выходным напряжением

буферного усилителя является напряжениеV, поделенное междуR3и параллельным соединениемR3иR4и равное

![]() .

В общем случае легко показать, что

максимальная величина напряжения,

подаваемого в качестве единичного

сигнала на вход буферного усилителя,

есть

.

В общем случае легко показать, что

максимальная величина напряжения,

подаваемого в качестве единичного

сигнала на вход буферного усилителя,

есть

![]() , (3.1)

, (3.1)

где nобщее количество резисторов, подсоединенных к рассматриваемой разрядной линии. Из 3.1 следует, что при большихnVmaxстановится малым, и тем затрудняется различие состояний 0 и 1.

Рассмотренные проблемы можно значительно упростить, если использовать нелинейные либо активные элементы. Применение диодов вместо резисторов в схеме 3.2 с подсоединением катода к разрядным линиям, а анодов к числовым линиям устраняет действие нагрузки, характерное для резистивных ПЗУ. В связи с последними успехами в области технологии СИС и БИС стало обычным применение биполярных транзисторов и МОП – транзисторов.

Адресация по принципу совпадения токов

В настоящее время потребителям поставляют ПЗУ большого объема (порядка сотен слов). При использовании линейной выборки дешифратор адреса памяти при больших значениях Nпревращается в очень сложную схему. Чтобы избежать этого, каждую разрядную линию заменяютN– разрядной матрицейX-Y. Адресация производится путем одновременной выдачиX- иY- адресов. В этом случае для схемы рис. 3.1. дешифратор адреса памяти будет состоять из 1 изXи 1изYдешифраторов, а матрица памяти будет включатьMматрицX-Y.

Отдельная

матрица X-Y для ПЗУ с адресацией по

принципу совпадения токов показана на

рис. 3.3. Здесь имеется qвходных зажимов дешифратора 1 изXиrвходных зажимов

дешифратора 1 из Y, что требует выполнения

соотношения

![]() и

и

![]() .

Поскольку

.

Поскольку

![]() ,

то

,

то

![]() .

Учитывая, что

.

Учитывая, что

![]() для случая линейной выборки, получаем

для случая линейной выборки, получаем

![]() .

Таким образом, для ПЗУ необходимо одно

и тоже число входных зажимов независимо

от способа адресации.

.

Таким образом, для ПЗУ необходимо одно

и тоже число входных зажимов независимо

от способа адресации.

Рис. 3.3. Отдельная матрица X-Yв ПЗУ с выборкой по принципу совпадения

При обращении к ПЗУ за некоторым словом qвходных сигналов поступают наXдешифратор, который активирует соответствующуюX-линию. ВходXназывают иногда выборкой строки или выборкой слова. Подобным образомrвходных сигналов Y дешифратора активируют соответствующую Y-линию. Вход Y называют выборкой столбца или разряда. Пересечению активных линийXиYсоответствует единственная ячейка памяти. Управляющая схема через линию считывания подает сигнал, соответствующий хранимому в данной ячейки двоичному знаку, на выходной буферный усилитель. Этот сигнал представляет один из разрядовMдвоичного слова. ОстальныеM-1 разрядов слова генерируются аналогичным образом.M– матрицы, называемые платами или сегментами, соединяются параллельно, так что платы возбуждаются одновременно. Далее один двоичный сигнал с каждой платы поступает через линию считывания на выходной буферный усилитель.

Матрица памяти типа X-Yс адресацией по принципу совпадения токов на МОП – транзисторных элементах связи показана на рис. 3.4, где подсоединение затворов транзисторов к линиямXсоответствует нулю, а открытые затворы единице.

Рис. 3.4 Отдельная матрица X-Yв ПЗУ с выборкой по принципу совпадения.

Полупроводниковые ПЗУ

ПЗУ реализуют на СИС и БИС, выполненных на основе как биполярной, так и МОП – технологии. Как правило, биполярные схемы обладают большим быстродействием и более высокой нагрузочной способностью по выходу, в то время как МОП – схемы потребляют меньшую мощность и более компактны. Время выборки лежит в интервале от 1 до 50 мкс для МОП ‑ схем и биполярных схем. Емкость как МОП, так и биполярных ПЗУ достигает 8К бит.

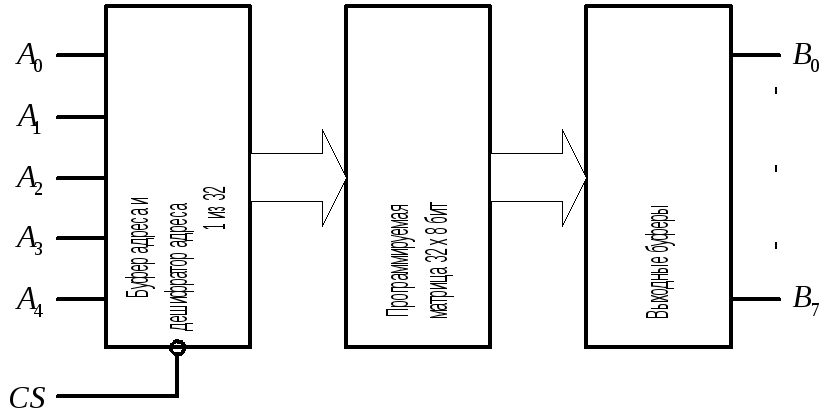

При производстве биполярных ПЗУ широко используются TTLиECL– схемы. На рис. 3.5 показана блок схема ПЗУ типа 7488TTLемкостью 256 бит. Это устройство, выпускаемое многими фирмами, программируется по заказу пользователя. Здесь используется адресация по принципу линейной выборки на 32 8-разрядных слова. Устройство имеет 16 выводов и поставляется в корпусе с двухрядным расположением выводов и в плоском корпусе. Вывод «Выбор кристалла» используется для отпирания выводовB0-B7, он необходим для расширения емкости памяти за счет объединения нескольких модулей. При этом требуется дополнительная комбинационная схема для активации нужного выхода выбора кристалла.

Рис. 3.5 Структурная схема ПЗУ емкостью 256 бит типа 7488, выполненного на базе TTL

Для большинства полупроводниковых ЗУ характерно наличие выходного сигнала с тремя выходными состояниями. В памяти подобного типа выходные схемы разомкнуты, когда нет обращения к памяти. Это делает возможным параллельное использование шины данных различными ЗУ, так как устраняется действие нагрузки со стороны запертых входных схем. При обращении к ЗУ считываются обычные сигнал 0 и 1.

Биполярные ПЗУ с программируемым полем также производятся в широких масштабах. В таких устройствах обычно используют легко плавкие соединения эмиттеров отдельных ячеек памяти, которые могут быть разомкнуты при программировании устройства после его компоновки. Другой метод программирования заключается в подаче напряжения превышающего уровень пробоя перехода эмиттер-база отдельных транзисторов ячеек памяти. В результате переноса металла закорачивается переход эмиттер-база. В настоящее время многие изготовители выпускают оборудование для программирования ППЗУ.

В ПЗУ, построенных на базе на базе МОП – приборов, используется p– канальная (p- МОП) иnканальная (n-МОП) и комплиментарная (КМОП) технологии. Эти виды технологии используются в указанных трех случаях: в ПЗУ программируемых по заказу пользователей, в ПЗУ с программируемым полем и перепрограммируемых ПЗУ. Обычноp-МОП – схемы дешевле, но обладают более низким быстродействием, в то время какn-МОП – схемы по быстродействию в некоторых случаях приближаются к биполярным приборам. КМОП – схемы имеют крайне низкую потребляемую мощность и относительно высокое быстродействие, позволяя легко достигать частот 20 МГц. К сожалению технология производства КМОП – схем является сложной, и поэтому они дорожеp- иn-МОП – схем.

В настоящее время поставляются по крайней мере два типа перепрограммируемых МОП ПЗУ. Наибольшее распространение получили устройства, использующие матрицу p-МОП – транзисторов с плавающим затвором. При большой разности потенциалов между истоком и стоком на затворе скапливается отрицательный заряд в следствии инжекции электронов с истока. Этот изолированный отрицательный заряд создает канал проводимости с временем жизни при нормальных условиях работы до 100 лет. Записанную в данном устройстве информацию можно стереть путем воздействия на схему ультрафиолетовым излучением. Для обеспечения возможности стирания данных рассматриваемые ИС выпускаются в корпусе с кварцевым покрытием.

Полупроводниковые ЗУ делятся на статические и динамические. В статических ЗУ обычно не требуется дополнительных схем для восстановления выбираемой информации, в то время как в динамических ЗУ необходимы схемы для осуществления периодически выполняемого цикла регенерации. Все ПЗУ, рассмотренные в настоящем разделе, являются статическими. Хотя динамические ПЗУ и поставляются потребителям, более распространенными являются устройства статического типа.