- •Предисловие

- •Глава 1

- •1.1. Средства микропроцессорной вычислительной техники

- •1.2. Основные характеристики, место и классификация микроЭвм

- •1.3. Индустрия микропроцессорных средств вт

- •Глава 2 элементная база микроэвм. Микропроцессоры

- •2.1. Микропроцессорные бис

- •2.2. Микропроцессор 8086

- •2.3. Развитие семейства мп 8086

- •Глава 3 элементная база микроэвм. Микропроцессорные семейства бис

- •3.1. Сопроцессоры

- •3.2 Интегральные микросхемы памяти

- •3.3. Интерфейсные схемы, контроллеры

- •3.4. Схемы обрамления

- •Глава 4 магистрально-модульная организация микроэвм

- •4.1. Интерфейсы и магистрали микроЭвм

- •4.2. Магистрали типа Multibus

- •4.3. Интерфейсы периферийного оборудования

- •4.4. Конструктивные особенности микроЭвм

- •Глава 5 аппаратура микроэвм

- •5.1. Периферия микроЭвм

- •5.2. Аппаратура персональных микроЭвм

- •5.3. Модульные системы и одноплатные микроЭвм

- •Глава 6

- •6.1. Операционные системы

- •6.2. Средства автоматизации программирования

- •6.3. Пакеты прикладных программ

- •1. Монография я учебные издания

- •2. Периодические издания

- •3. Фирменные издания

- •Глава 1. Введение в микропроцессорную технику .............................. 5

- •Глава 2. Элементная база микроЭвм. Микропроцессоры ...................... 18

- •Глава 3. Элементная база микроЭвм. Микропроцессорные семейства бис ............................................................................................................................ 81

- •Глава 4. Магистрально-модульная организация микроЭвм ……………108

- •Глава 5. Аппаратура микроЭвм ............. ……………………………….148

- •Глава 6. Программное обеспечение микроЭвм ........................................187

Глава 3 элементная база микроэвм. Микропроцессорные семейства бис

При создании законченного микропроцессорного вычислителя невозможно обойтись только одной микросхемой МП, необходим достаточно большой набор БИС, обеспечивающих хранение информации, связь с внешним миром, генерацию сигналов и т. п. Такой набор микросхем, совместимых с микропроцессором и между собой по своим системным и схемным характеристикам, получил название микропроцессорного семейства БИС или микропроцессорного комплекта БИС (несколько более узкое понятие). Микропроцессорное семейство в широком его понимании, кроме собственно БИС МП, содержит:

сопроцессоры, снижающие вычислительную нагрузку на основной МП за счет аппаратной реализации часто встречающихся операций и функций (операции с плавающей запятой, вычисление элементарных функций, обработка графических примитивов и т. п.);

микросхемы памяти, необходимые для хранения, воспроизведения и записи программ и обрабатываемых данных;

интерфейсные схемы, обеспечивающие сопряжение вычислителя с различными внешними устройствами (дисками, дисплеями, принтерами и т. п.);

схемы обрамления, поддерживающие нормальное функционирование микропроцессора и вычислителя в целом.

Микропроцессорный комплект БИС включает более узкий набор микросхем (обычно без элементов памяти) и чаще относится к многокристальным или секционным МП. Микропроцессорное семейство выпускается, как правило, одной или по лицензионным соглашениям несколькими фирмами. Однако формальное отсутствие той или иной микросхемы в списке семейства не является препятствием к ее использованию наряду с настоящими членами. Здесь все определяется системной, схемной и экономической целесообразностью.

3.1. Сопроцессоры

Стремление повысить производительность микропроцессорных вычислительных систем привело в конце 70-х — начале 80-г гг. к появлению нового класса БИС — сопроцессоров (coprocessor). Сопроцессор аппаратно ориентирован на выполнение некоторых часто встречающихся операций и/или функций и, при включении в систему, исключает их из основного процессора. Это, во-первых, резко снижает временные затраты на их реализацию и, во-вторых, основной процессор освобождается для других вычислений. В настоящее время наибольшее распространение получили следующие типы сопроцессоров:

сопроцессоры ввода-вывода, предназначенные для организации быстрого обмена большими массивами информации с внешними устройствами, например, БИС 8089 фирмы Intel Corp. [3.2];

арифметические (математические) сопроцессоры, ориентированные на выполнение арифметических операций над числами в формате с плавающей запятой и вычисление элементарных функций;

кремниевые операционные системы, реализующие в виде БИС ядро некоторой операционной системы, например, схема 80150 фирмы Intel Corp. [3.2], поддерживающая работу ОС СР/М 86 в портативных микроЭВМ на базе МП 8086/8088;

графические сопроцессоры, содержащие аппаратные средства построения графических примитивов (линий, окружностей, текстов и т. п.), управления окнами и многостраничной экранной памятью в высококачественных графических дисплеях, например, ИС 34010 фирмы Texas Instruments [2.8] для МП типа Motorola 68020;

коммуникационные сопроцессоры, аппаратно реализующие протоколы обмена информацией в локальных вычислительных сетях, например, схема 82586 фирмы Intel Corp. для работы в сети чипа Ethernet/IEEE 802.3 [3.8].

Рассмотрим подробнее арифметический сопроцессор 8087 фирмы Intel Corp. для МП типа 8086/8088 [2.8, 3.13]. БИС 8087 предназначена для выполнения арифметических операций и вычисления элементарных функций с числами в форматах целого, короткого и длинного вещественного. Сопроцессор изготавливается по усовершенствованной nMOS технологии на кристалле площадью 70 мм2, содержит более 65 000 элементов, упакован в корпус типа DIP с 40 выводами. Сопроцессор состоит (рис. 3.1) из двух блоков — управления CU (control unit) и обработки NEU (numerical execution unit). Блок управления поддерживает синхронизацию работы микросхемы с основным процессором. В него входят 6-байтная очередь команд, идентичная по своей организации очереди в МП 8086, буфероперандов, в котором накапливаются многоразрядные коды, устройство сопряжения с шиной и регистры состояния и управления. Блок управления информационно связан с блоком обработки 16-разрядной шиной, подключенной к регистровому стеку. Кроме стека в NEU входят временные регистры, 68-разрядное АЛУ мантисс, быстрый 63-разрядный сдвигатель и обработчик порядков.

Регистровый стек ST состоит из восьми 80-разрядных регистров, в которых в специальном формате временных вещественных хранятся все операнды. Этот формат с 15-разрядным смещением и 64-разрядной мантиссой позволяет представлять числа в диапазоне Ю±490о с точностью до 19 десятичных цифр. Все типы данных при загрузке в NEU автоматически преобразуются в формат временного вещественного, а при выводе — в требуемый тип. В регистре слова состояния выделено трехразрядное поле Тор, содержимое которого определяет регистр, являющийся в данный момент вершиной стека. По сути Top — это указатель стека. Операции загрузки (типа POP) уменьшают Тор на единицу и записывают 80-разрядный код в новый регистр вершины стека. Операции разгрузки (типа PUSH, вытолкнуть) считывают код числа из текущего регистра вершины и автоматически увеличивают Тор на единицу.

Как и в МП 8086, стек «растет вниз» по направлению уменьшения номеров регистров. Команды сопроцессора могут адресовать регистры стека неявно, обращаясь к вершине, или явно, задавая смещение номера регистра относительно Тор. Такая двойная адресация ST значительно упрощает организацию передачи параметров при обращении к подпрограммам.

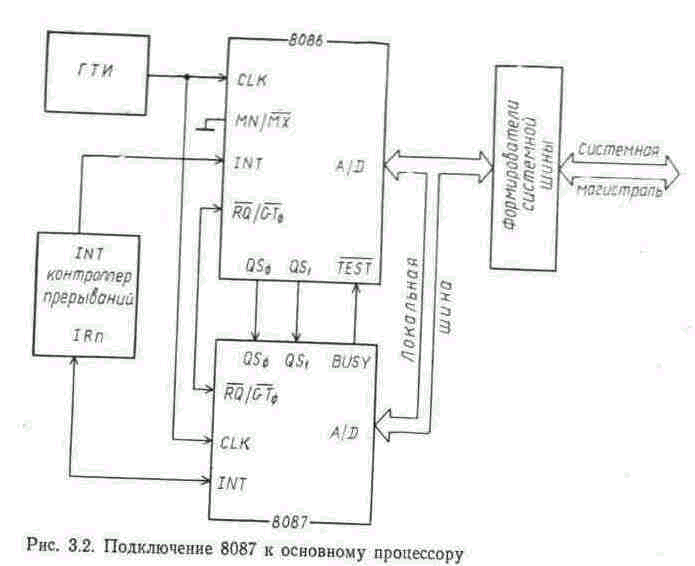

Внешний

интерфейс сопроцессора и его подключение

к процессору 8086 иллюстрируется рис.

3.2. Назначение и спецификация линий

адреса/данных A/D15—A/D0,

адреса/состояния A19/S6

— A16/S3,

разрешения старшего байта

![]() сопроцессора абсолютно аналогичны МП

8086. Одноименные линии сопроцессора и

процессора соединяются, образуя

локальную шину системы. Управляет этой

шиной основной процессор 8086, он формирует

адреса, считывает программные коды

из памяти, выполняет запись или чтение

данных. Все коды, которые МП выбирает

из памяти, поступают по локальной шине

и на вход сопроцессора. Последовательность

команд одновременно с основным процессором

записывается в очередь команд

сопроцессора.

сопроцессора абсолютно аналогичны МП

8086. Одноименные линии сопроцессора и

процессора соединяются, образуя

локальную шину системы. Управляет этой

шиной основной процессор 8086, он формирует

адреса, считывает программные коды

из памяти, выполняет запись или чтение

данных. Все коды, которые МП выбирает

из памяти, поступают по локальной шине

и на вход сопроцессора. Последовательность

команд одновременно с основным процессором

записывается в очередь команд

сопроцессора.

Для синхронизации этого процесса служат два входа QS0, QS1, соединенные с соответствующими выходами 8086. Обычные команды МП 8086 сопроцессором игнорируются. И только, когда процессор и сопроцессор начинают обрабатывать команду расширения ESC, она воспринимается как инструкция для 8087. Возможные три типа команд сопроцессора: без обращения к памяти, с обращением к памяти для чтения операнда, с обращением памяти для записи результата. В первом случае сопроцессор, получив команду, приступает к ее выполнению, а процессор может продолжать выборку и обработку программы. Во втором случае МП формирует адрес операнда и организует фиктивный цикл чтения. Считанное из памяти слово поступает на локальную шину и принимается сопроцессором. Если операнд большой разрядности (32, 64 или 80), сопроцессор в цикле фиктивного чтения перехватывает адрес операнда и получает право управления шиной. Теперь уже сопроцессор организует циклы чтения остальных элементов операнда. Прочитав его полностью, он возвращает управление шиной основному процессору и приступает к выполнению команды. В третьем случае (обращение к памяти для записи результата), получив команду 8086, также формирует адрес и организует цикл фиктивного чтения. Сопроцессор перехватывает и запоминает адрес результата, и начинает выполнять операцию. Завершив ее, 8087 запрашивает право управления шиной. Получив шину от МП 8086, сопроцессор записывает результат по сохраненному адресу.

Передача

управления шиной осуществляется с

помощью сигнала на линии

![]() процессора и сопроцессора, объединенных

между собой. Когда 8087 необходимо

управление шиной, он выдает единичный

сигнал (низкий уровень) шириной в один

тактовый импульс в МП 8086. Последний,

приняв этот сигнал, завершает выполнение

очередного цикла работы и в такте Т4

(или T1

следующего цикла) выдает по той же линии

ответный сигнал, сообщая сопроцессору,

что в наступающем такте линии адреса/данных

будут переведены в третье состояние.

Получив управление шиной, сопроцессор

через такт переводит свои линии

адреса/данных в активное состояние и

выполняет необходимые действия по

чтению или записи данных. После завершения

обмена 8087 вторично генерирует сигнал

на линии

,

информируя процессор, что локальная

шина отдается в его распоряжение.

Таким образом, обмен шиной требует не

менее трех тактов работы.

процессора и сопроцессора, объединенных

между собой. Когда 8087 необходимо

управление шиной, он выдает единичный

сигнал (низкий уровень) шириной в один

тактовый импульс в МП 8086. Последний,

приняв этот сигнал, завершает выполнение

очередного цикла работы и в такте Т4

(или T1

следующего цикла) выдает по той же линии

ответный сигнал, сообщая сопроцессору,

что в наступающем такте линии адреса/данных

будут переведены в третье состояние.

Получив управление шиной, сопроцессор

через такт переводит свои линии

адреса/данных в активное состояние и

выполняет необходимые действия по

чтению или записи данных. После завершения

обмена 8087 вторично генерирует сигнал

на линии

,

информируя процессор, что локальная

шина отдается в его распоряжение.

Таким образом, обмен шиной требует не

менее трех тактов работы.

В процессе выполнения команды в блоке NEU сопроцессор активизирует выход BUSY (занято), который подключен к входу TEST МП 8086. Следовательно, с помощью команды WAIT можно легко засинхронизировать работу процессора и сопроцессора при выполнении некоторой программы. Это важно в двух случаях, во-первых, когда программа обращается к сопроцессору до завершения им обработки предыдущей команды и, во-вторых, когда программе необходимо работать с результатом операции, выполняемой в 8087. В ассемблере MASM-86 предусмотрена автоматическая генерация команды WAIT перед каждой командой сопроцессора, требующей ресурсов блока обработки, что обеспечивает синхронизацию для первого случая. При возникновении особых ситуаций сопроцессор генерирует на выходе INT запрос на прерывание, который обычно подается на контроллер 8259А для обработки.

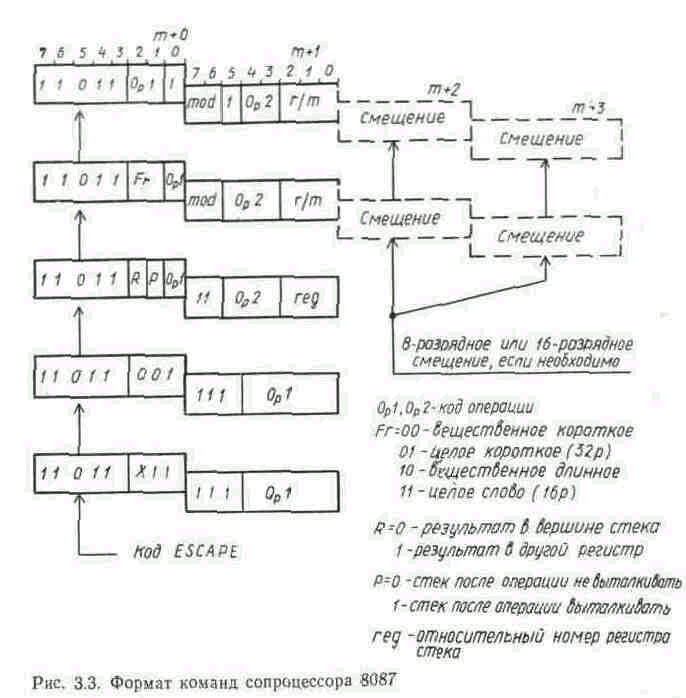

БИС 8087 работает с семью типами данных (см. табл. 2.7 и рис. 2.20): целые двоичные со знаком (слово, короткое, длинное), целые упакованные десятичные (18 десятичных разрядов и байт знака) и вещественные (короткие, длинные, временные). Сопроцессор выполняет 69 команд, форматы которых приведены на рис. 3.3. Все команды в пяти старших разрядах первого байта содержат код 110112, позволяющий отличить их от команд МП 8086. Собственно операция для сопроцессора задается полями Ор1 и Ор2.

Так как адрес операнда в памяти формируется 8086 в цикле фиктивного чтения, то и поля mod и r/m имеют аналогичный смысл (см. рис. 2.12, кроме случая mod = 11). В части команд тип операнда задается полем Fr (формат), однако операции над временными вещественными и длинными целыми инициализируются особыми инструкциями. Команды сопроцессора можно разбить на 6 групп:

передача данных - пересылка кодов между памятью и стеком ST (как с вершиной стека, так и любым из 8 его регистров), между регистрами стека;

арифметика — сложение, инкремент, вычитание, обратное вычитание, декремент, умножение, деление, обратное деление, квадратный корень и другие;

логика — сравнение двух чисел (вершины стека с любым элементом или нулем) с установкой флагов состояния, проверка;

трансцендентные

функции — вычисление тангенса,

арктангенса,

![]() ;

;

формирование констант — загрузка в стек констант 0, 1, , log102, log210, log2е, loge2;

управление сопроцессором — загрузка и запись управляющего слова, загрузка и запись полного состояния сопроцессора, управление режимами работы схемы (инициализация, прерывание, ошибки).

Программисту предоставляется возможность управления точностью округления результатов операций до одного из трех диапазонов представления мантиссы (24, 53, 64 разряда). При задании точности 24 или 53 разряда результат всех операций формируется в соответствии с требованиями стандарта IEEE. Само округление также может выполняться одним из четырех способов: «вверх», «вниз», по направлению к нулю, до ближайшего представимого числа. Конкретный способ округления выбирается программно. Формат вещественного предусматривает представление + и . Эти значения генерируются сопроцессором при наступлении особых случаев, например, при делении на ноль или получении результата, превосходящего максимально представимое число. Пользователь может задать формирование только + в любой ситуации или в зависимости от знака результата. В случае неопределенного операнда, например, при считывании из пустого регистра, сопроцессор автоматически формирует специальный код результата Nan (см. с. 64), что позволяет легко зафиксировать использование неинициализированных переменных.

Сопроцессор обнаруживает шесть особых ситуаций, которые отображаются в слове состояния и являются причиной формирования запроса на прерывание. Устанавливая программно соответствующие разряды в управляющем слове, можно замаскирован прерывание по каждой ситуации или их комбинации. При запрете возникшая особая ситуация обрабатывается аппаратно и генерируется предопределенный результат. БИС 8087 реагирует на следующие особые ситуации.

Недействительная операция — переполнение или антипереполнение стека, неопределенная ситуация (деление 0 на 0, вычитание бесконечностей) или использование Nan в качестве операнда. Если прерывание замаскировано, то в качестве результата генерируется Nan. Переполнение — результат операции слишком большой для заданного формата. Если этот случай замаскирован, 8087 генерирует код , в соответствии с запрограммированной реакцией. Антипереполнение — слишком маленький ненулевой результат, не размещающийся в заданном формате. При маскировании 8087 выполняет денормализацию результата (сдвиг вправо мантиссы). Этот процесс называется «мягким» антипереполнением. Нулевой делитель — в операции деления делитель равен нулю, а делимое — нет. 8087 генерирует код , если этот случай замаскирован. Денормализованный операнд — один из операндов или результат денормализован. При маскировании продолжается нормальная работа. Неточный результат — ситуация возникает, если результат неточно представим в выбранном формате (т. е. требует округления). Результат округляется по запрограммированному правилу и, если прерывание замаскировано, вычисления продолжаются.

Необходимо отметить, что будучи взведенным, флаг особой ситуации в слове состояния остается неизменным. Его можно сбросить лишь специальной командой перезаписи флаговых разрядов. Это дает возможность после выполнения длинной последовательности команд, например, подпрограммы, проверить слово состояния и убедиться, что особые ситуации не возникали.

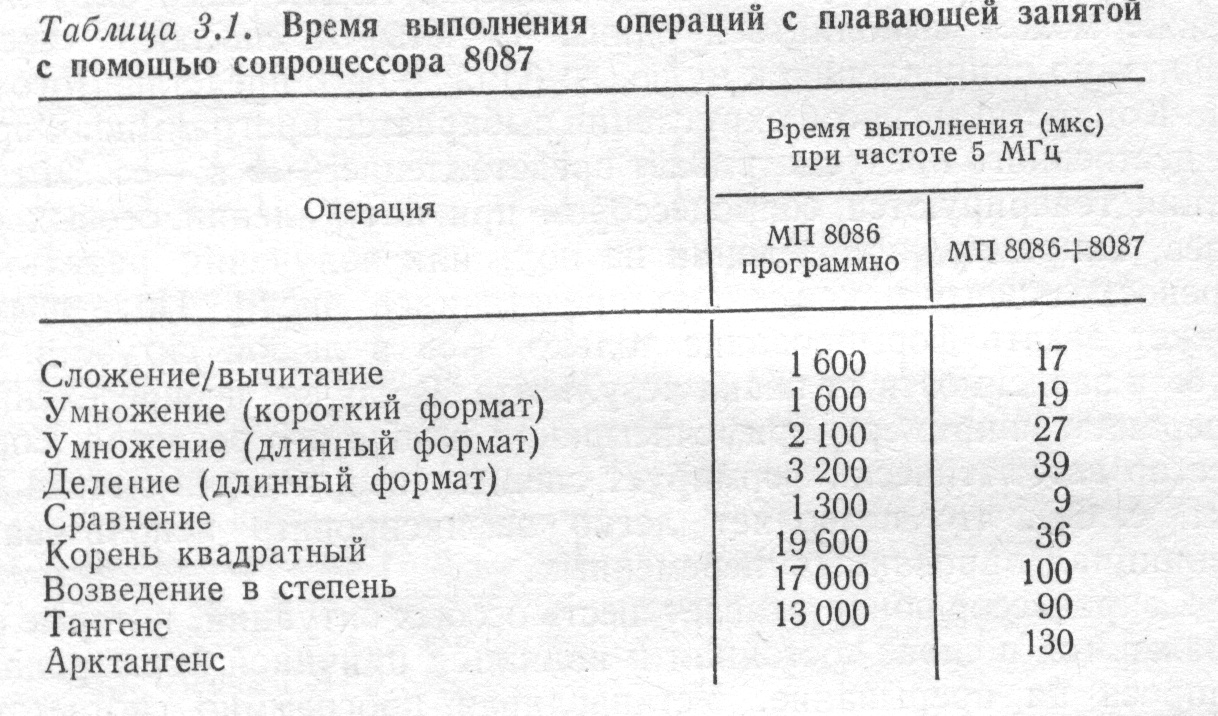

Работая на частоте 5 МГц, сопроцессор на два порядка сокращает время выполнения операций с плавающей запятой (табл. 3.1)

1.30, 3.13]. БИС 8087 обеспечивает точность вычислений и предоставляет пользователю ряд возможностей (управление округлением, управление знаком бесконечности, управление особыми ситуациями), недостижимых в большинстве мини- и средних ЭВМ. Дальнейшее развитие идеи математического сопроцессора получили в БИС 80287 (сопроцессор для МП 80286) и БИС 80387 (32-разрядный сопроцессор для МП 80386).