- •Предисловие

- •Глава 1

- •1.1. Средства микропроцессорной вычислительной техники

- •1.2. Основные характеристики, место и классификация микроЭвм

- •1.3. Индустрия микропроцессорных средств вт

- •Глава 2 элементная база микроэвм. Микропроцессоры

- •2.1. Микропроцессорные бис

- •2.2. Микропроцессор 8086

- •2.3. Развитие семейства мп 8086

- •Глава 3 элементная база микроэвм. Микропроцессорные семейства бис

- •3.1. Сопроцессоры

- •3.2 Интегральные микросхемы памяти

- •3.3. Интерфейсные схемы, контроллеры

- •3.4. Схемы обрамления

- •Глава 4 магистрально-модульная организация микроэвм

- •4.1. Интерфейсы и магистрали микроЭвм

- •4.2. Магистрали типа Multibus

- •4.3. Интерфейсы периферийного оборудования

- •4.4. Конструктивные особенности микроЭвм

- •Глава 5 аппаратура микроэвм

- •5.1. Периферия микроЭвм

- •5.2. Аппаратура персональных микроЭвм

- •5.3. Модульные системы и одноплатные микроЭвм

- •Глава 6

- •6.1. Операционные системы

- •6.2. Средства автоматизации программирования

- •6.3. Пакеты прикладных программ

- •1. Монография я учебные издания

- •2. Периодические издания

- •3. Фирменные издания

- •Глава 1. Введение в микропроцессорную технику .............................. 5

- •Глава 2. Элементная база микроЭвм. Микропроцессоры ...................... 18

- •Глава 3. Элементная база микроЭвм. Микропроцессорные семейства бис ............................................................................................................................ 81

- •Глава 4. Магистрально-модульная организация микроЭвм ……………108

- •Глава 5. Аппаратура микроЭвм ............. ……………………………….148

- •Глава 6. Программное обеспечение микроЭвм ........................................187

2.3. Развитие семейства мп 8086

Архитектура 16-разрядных микропроцессоров фирмы Intel развивалась (см. рис. 2.1) по двум направлениям: интеграция в одном микропроцессорном кристалле схем обрамления и интерфейсных схем (линия 80186) и расширение системных возможностей процессора (линия 80286, 80386).

МП 80186/80188 (система iAPX 186) [2.5, 2.7, 3.3].

Микропроцессор 80186, упрощенная структура которого дана на рис. 2.21, кроме устройства сопряжения с шиной и устройства обработки, выполняющих те же функции, что и в МП 8086, содержит:

генератор тактовых синхросигналов,

программируемый контролер прерываний,

три программируемых 16-разрядных таймера,

два программируемых контролера канала прямого доступа в память,

программируемые формирователи сигналов выборки кристаллов ЗУ и ВВ.

МП 80186 упакован в квадратный корпус типа JEDEC с 68 выводами (по 17 на каждой стороне) и выпускается в двух модификациях с рабочими частотами 6 и 8 МГц. При полной программной совместимости снизу (МП 80186 может выполнять все программы, написанные для 8086), производительность 80186, в среднем в два раза выше, чем 8086. В МП 80186 введено десять новых команд, которые упрощают программирование или повышают быстродействие.

Генератор тактовых импульсов полностью обеспечивает как внутреннюю, так и внешнюю синхронизацию микропроцессорной системы на базе 80186. Период тактовых импульсов стабилизируется внешним кварцевым резонатором удвоенной частоты. В генераторе предусмотрены также схемы синхронизации внешних асинхронных сигналов сброса и готовности.

Управление работой всех внутренних дополнительных устройств МП осуществляет через соответствующие регистры, составляющие единый регистровый блок управления длиной 256 байт. Каждый регистр адресуется смещением относительно базового адреса, который программно записывается в специальный регистр перемещения (последние два байта управляющего блока). Блок управления разрядом M/IO в регистре перемещения может «накладываться» на адресное поле памяти или на адресное поле устройств ввода-вывода. В последнем случае доступ к регистрам управления возможен только с помощью команд ввода-вывода.

Программируемый контроллер прерываний предназначен для обработки запросов на прерывания от внутренних и внешних источников. Внутренними источниками могут быть таймеры и каналы прямого доступа. Пять внешних запросов INT3—INT0 и не маскируемый NMI поступают через соответствующие контакты микросхемы. Контроллер может работать в двух, программно задаваемых режимах: основном и совместимом с 8086.

В контроллере содержится 15 программно доступных регистров (смещения 2216—3Е16), с помощью которых процессор управляет его работой. Например, для каждого внешнего источника запроса можно установить реакцию либо на уровень, либо на фронт сигнала. С помощью маски можно подавить запрос от любого источника. Программно для каждого внутреннего и внешнего источника можно задать один из восьми приоритетных уровней. Контроллер, при наличии нескольких запросов, выберет наиболее приоритетный и аппаратно сформирует соответствующий вектор прерывания. При поступлении более приоритетного запроса во время обслуживания менее приоритетного контроллер выполнит переключение на его обработку.

В основном режиме допускается каскадное подключение восьми дополнительных контролеров типа 8259А, что расширяет количество обрабатываемых внешних запросов до 128. В режиме, совместимом с 8086, внутренний контроллер функционирует под управлением внешнего, имитируя структуру системы прерывания, принятую для операционной системы iRMX.

В МП 80186 встроено три программно управляемых 16-разрядных таймера, два из которых (Tmr0 и Tmr1) имеют внешние входы и выходы. Третий таймер (Tmr2) используется только для внутренних нужд МП: организации системного таймера, генерации временных задержек, генерации запроса на передачу данных через канал прямого доступа. Таймеры Tmr0, Tmrl разработчик может применять для различных целей, например, для подсчета внешних событий, генерации периодических и непериодических сигналов и т. п.

Управление работой таймеров осуществляется через одиннадцать 16-разрядных регистров (смещения 5016—6616). Каждый таймер имеет 4 программно доступных регистра: регистр режима — управления, регистр счетчика, максимальный регистр А и максимальный регистр В (в Tmr2 регистра В нет). На вход таймеров, в зависимости от кода в регистре управления — режима, можно подавать внешние сигналы, воспринимаемые по фронту или уровню, или тактовые

импульсы синхронизации. В максимальные регистры А и В заносятся предельные значения, после достижения которых счетчик таймера сбрасывается в ноль и вырабатывает сигнал запроса на прерывание и внешний выходной сигнал, вид которого тоже программно контролируется. Возможен режим автоматического переключения максимальных регистров А и В. Программное изменение содержимого свободного максимального регистра позволяет генерировать произвольно сложные непериодические сигналы. Процессор может в любой момент прочитать содержимое регистра счетчика таймера или записать в него новый код.

Два контроллера каналов прямого доступа в память (direct memory access channel, DMA channel) обеспечивают передачу данных между различными областями памяти и/или устройствами ввода-вывода с максимальной скоростью 2 Мбайт/с. Управление paботой каналов осуществляется с помощью шести 16-разрядных регистров (смещения CO16—CA16 для канала 0, смещения D016—DА16 для канала 1): регистр — указатель источника (2 слова), регистр — указатель приемника (2 слова), счетчик передач и регистр режима. Код в последнем регистре задает: режим синхронизации (от источника, от приемника, асинхронно), разрядность данных (байт, слово), генерацию запроса на прерывание после окончания обмена, относительный приоритет между каналами, режим изменения указателей источника и приемника (не изменять, увеличивать, уменьшать) после каждого обмена, поле адресов памяти или поле адресов ввода-вывода отдельно для приемника и источника.

Количество обменов, которое необходимо выполнить, определяется содержимым счетчика передач, первоначально устанавливаемым программно. После каждого обмена содержимое счетчика уменьшается на единицу. При достижении нуля обмен прекращается и, если запрограммировано, генерируется запрос на прерывание. Максимальное количество передаваемых по каналу данных 64 Кбайт или 64 Кслов. Двадцатиразрядные указатели приемника и источника адресуют данные в поле адресов памяти или ввода-вывода. Указатели после каждой передачи автоматически уменьшаются (увеличиваются) на 1 при обмене байтами или на 2 при обмене словами. Отмечается высокая гибкость встроенных контроллеров прямого доступа, их функциональные возможности значительно шире, чем у многих контроллеров, реализованных в виде отдельных БИС [2.7].

Программируемые формирователи обеспечивают генерацию шести сигналов выборки кристаллов памяти и семи сигналов выборки устройств ввода-вывода. Сигнал LCS выдается при обращении. к «младшей» области памяти, начинающейся с адреса 0000016 Сигнал UCS генерируется при обращении к «старшей» области памяти, которая заканчивается адресом FFFFF16. Длина этих двух областей может быть установлена программно. Остальные четыре сигнала выборки кристаллов памяти МСS3—MCS0 формируются при обращении к некоторой «средней» области, начальный адрес и длина которой также задаются программно. Сигналы выборки периферийных устройств PCS6 — PCS0 генерируются при обращении к области адресов устройства ввода-вывода, начальный адрес которой устанавливается процессором. Для управления схемами формирования используются четыре регистра (смещения А016—А816).

Считается, что встроенные в МП 80186 устройства сокращают на 15—20 корпусов количество схем обрамления и периферийных схем, необходимых для построения законченного микропроцессорного вычислителя.

МП 80286 (система iАРХ286) [2.8, 2.12, 3.4]. Этот микропроцессор ориентирован на построение многозадачных и многопользовательских систем, аппаратно поддерживает виртуальное адресное пространство объемом 1 Гбайт (физически адресуется память 16 Мбайт) и четырехуровневую систему защиты программ и данных. МП 80286 программно совместим «сверху» с 8086 и 80186, список его команд расширен системными операциями и операциями управления режимами работы памяти и защиты.

Упрощенная структура микропроцессора приведена на рис. 2.22. Кроме устройства сопряжения с шиной и устройства обработки, функционально аналогичным соответствующим элементам МП 8086, в состав 80286 включены декодер команд и формирователь адресов. Как и в МП 8086 устройство связи с шиной выполняет предварительную выборку команд, когда в шестибайтной очереди освобождается не менее двух байт. Устройство декодирования извлекает из очереди первую команду и расшифровывает ее, формируя 69-разрядную микрокоманду, которая загружается в собственную очередь декодированных команд. После завершения выполнения текущей операции устройство обработки извлекает из очереди декодированных команд очередную микрокоманду и начинает выполнять ее. Операции по обработке адресов и проверки правильности доступа к памяти и портам ввода-вывода возложены на устройство формирования адресов. Внутренние устройства МП 80286 образуют четырехступенчатый конвейер независимо от работающих блоков, что значительно повышает производительность процессора. В [3.4] указывается на шестикратное повышение производительности по сравнению с МП 8086, хотя в 12.12] приведены более сдержанные оценки, полученные экспериментально.

Микропроцессор работает в двух режимах: реальной адресации и защищенной виртуальной адресации. В первом режиме МП адресует 1 Мбайт памяти с помощью адресных линий А19—А0 и . Сегментация памяти, формирование физического адреса полностью аналогичны МП 8086. При инициализации и перезапуске микропроцессор автоматически переходит в режим реальной адресации. Основным режимом работы является защищенная виртуальная адресация, при которой каждому заданию доступен 1 Гбайт виртуальной памяти, отображаемой на 16 Мбайт физической. Для задания виртуального адреса используется 32-разрядный указатель, состоящий из 16-разрядного смещения в сегменте и 16-разрядного селектора сегмента. Селектор, который подобно базе сегмента для

МП 8086 хранится в сегментном регистре, содержит старшие 14 разрядов виртуального адреса и два разряда уровня приоритетности сегментов (поле RPL). Виртуальное адресное пространство делится на две равные части по 512 Мбайт — глобальную область и локальную область. Глобальная область доступна всем заданиям, находящимся в системе, локальная — только заданию, к которому она относится. Таким образом, каждое задание имеет свою защищенную локальную виртуальную память емкостью 512 Мбайт.

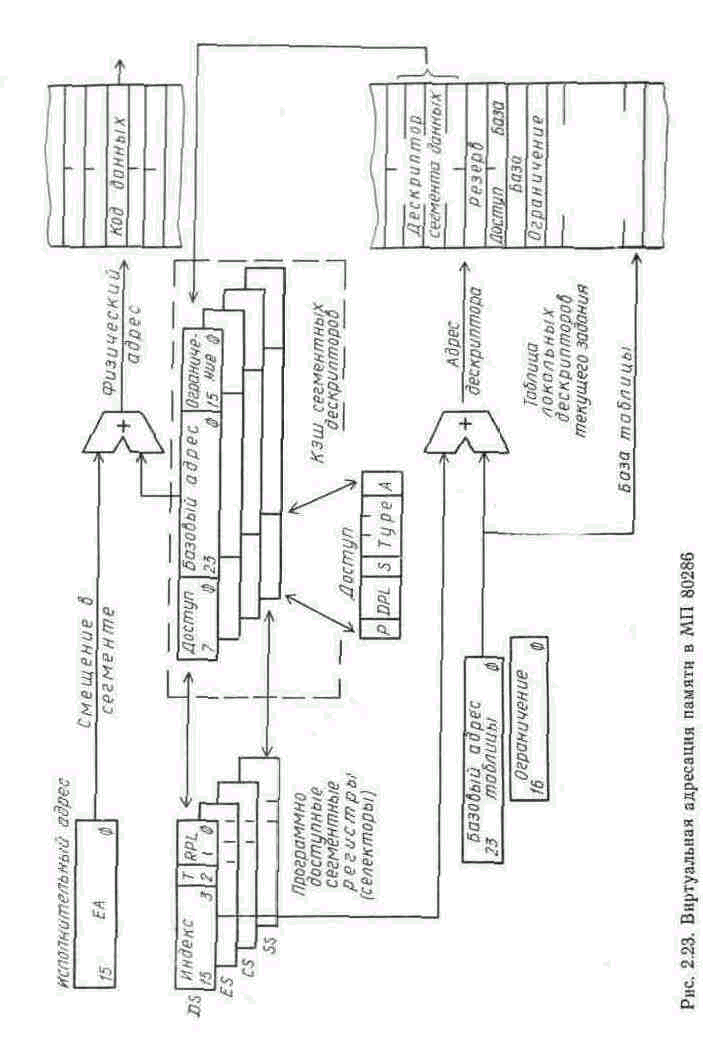

Отображение виртуального адреса на физическое адресное пространство в МП 80286 представлено на рис. 2.23. Любой сегмент памяти (локальной или глобальной), необходимый для выполнения

задания, например сегмент данных, стека или программы, задается с помощью 64-разрядного описателя сегмента — дескриптора (segment descriptor), который занимает восемь последовательных байт памяти. Дескриптор содержит 24-разрядную базу сегмента, 16-разрядное ограничение (длина сегмента — от 1 байта до 64 Кбайт) и байт доступа, определяющий тип сегмента, его привилегии и правила обращения. Дескрипторы сегментов, необходимые для прохождения задания, объединяются в таблицу локальных дескрипторов. Кроме дескрипторов сегментов таблица может содержать также дескрипторы вызова подпрограмм и заданий. Всего таблица может включать 8192 дескриптора. Аналогично образуется и таблица глобальных дескрипторов, определяющая программные сегменты и сегменты данных, доступные любому заданию.

В процессе выполнения текущего задания базовые адреса таблиц глобальных и локальных дескрипторов содержатся в специальных регистрах. При загрузке селектора в сегментный регистр, например, командой MOV, по его второму разряду (поле Т) определяется тип таблицы (если Т=0, то глобальная, если Т=1, то локальная) дескрипторов и, соответственно, тип виртуальной памяти. Старшие 13 разрядов селектора (индекс) определяют смещение вызываемого дескриптора в таблице относительно базы. Если соблюдаются все привилегии (текущий и запрашиваемый уровни достаточны для доступа), дескриптор считывается из таблицы и загружается в специальный программно недоступный набор регистров (кэш) сегментных дескрипторов, состоящий из четырех 48-разрядных регистров. При обращении к памяти, например, для чтения данных исполнительный адрес ЕА сравнивается с ограничением. Если предел сегмента не нарушен (причем можно задавать сегменты «растущие» вверх — сегменты данных и «растущие» вниз — сегменты стека), то физический адрес формируется как сумма 24-разрядного базового адреса сегмента и исполнительного адреса. По этому адресу и извлекается код данных из памяти. В случае отсутствия сегмента в физической памяти наступает исключительное событие (exeption) «нет сегмента», по которому управление передается операционной системе для подкачки сегмента с внешнего носителя. После записи сегмента в физическую память управление возвращается в программу пользователя, и операция чтения повторяется.

Три разряда (поле Type) в байте доступа сегмента определяют допустимые действия с кодами, расположенными в сегменте. Один из разрядов задает тип сегмента — данные или коды программы. Для сегмента данных возможна защита от записи. Для сегмента программных кодов обеспечивается защита от чтения и/или выполнения заданиями с более низким приоритетом. Поле DPL определяет один из четырех уровней привилегий данного сегмента. Наиболее привилегированный нулевой уровень предназначен для ядра операционной системы. Первый и второй уровни обычно назначаются расширениям операционной системы. Самый низкий уровень, четвертый, присваивается заданиям пользователя. Уровень привилегий текущего задания определяется содержимым поля RPL в сегментном регистре CS программных кодов. При попытке загрузить новый селектор в сегментный регистр данных DS происходит аппаратное сравнение текущего уровня (RPL из CS), запрашиваемого уровня (RPL из селектора) и уровня доступа (DPL из байта доступа дескриптора). Только, если текущий и запрашиваемый уровни меньше или равны (не менее приоритетны) уровню привилегий дескриптора, задание получает доступ к сегменту данных.

Межсегментные передачи управления (вызовы подпрограмм и возвраты из них, обработка прерываний и исключений) выполняются только через специально оговоренные шлюзы (gate), которые также задаются своими дескрипторами. Формат дескриптора шлюза во многом подобен дескриптору сегмента. Передача управления из менее привилегированной программы в область с большими привилегиями помимо шлюзов невозможна и вызывает соответствующее исключение. При любой передаче управления между сегментами с помощью механизма привилегий происходит проверка допустимости такого перехода. Дескрипторы вызовов подпрограмм и заданий располагаются в таблицах локальных и глобальных дескрипторов. Дескрипторы прерываний образуют специальную таблицу, определяющую до 256 входов в подпрограммы обработки прерываний и исключений.

Считается, что совокупность архитектурных и схемных решений, заложенных в МП 80286, открывает широкие возможности по построению многозадачных и многопользовательских микросистем повышенной производительности.

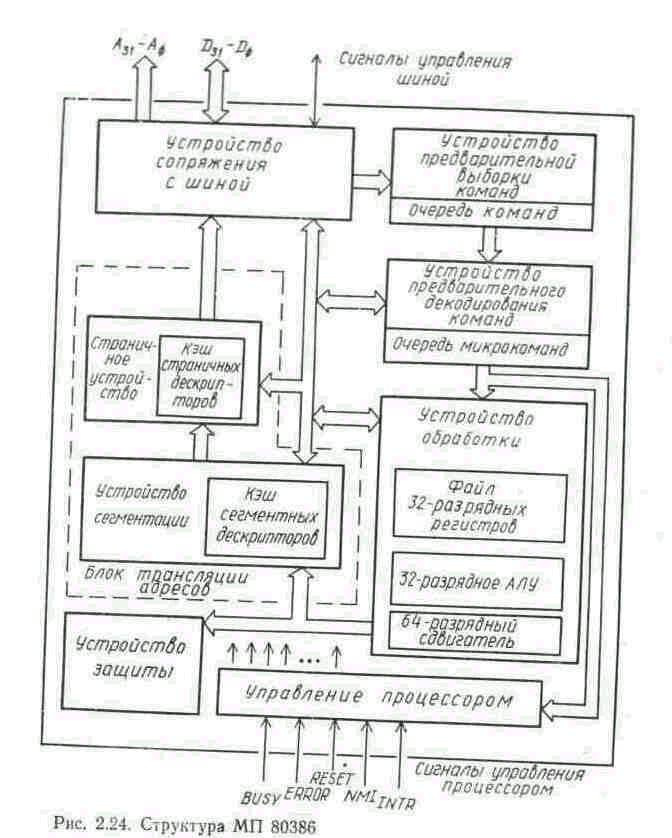

Микропроцессор 80386 (система iAPX386) [2.8, 2.9, 3.5]. 32-разрядный микропроцессор 80386 выполнен по усовершенствованной HMOS технологии с 1.5-микронными проектными нормами на квадратном кристалле со стороной 9,9 мм, содержит 250 000 транзисторов и работает с тактовой частотой 16 МГц. МП размещается в керамическом кристаллоносителе со 132 выводами. Структура микропроцессора приведена на рис. 2.24.

Процессор организован как конвейер восьми независимо работающих устройств, четыре из которых функционально идентичны МП 80286. Устройство сопряжения с шиной обеспечивает информационную связь МП с внешними элементами. Полноразрядная шина адреса позволяет подключать физическую память емкостью до 4 Гбайт. Шина данных поддерживает передачу кодов с максимальной скоростью до 32 Мбайт/с. С помощью специального входного сигнала (BS16) можно динамически изменять разрядность передаваемых по шине данных кодов. Получив этот сигнал, устройство сопряжения аппаратно организует передачу 32-разрядных кодов последовательно за два цикла по 16 разрядов каждый. Причем, на работе остальных блоков МП это никак не отражается. Устройство предварительной выборки загружает внутреннюю очередь команд, из которой они читаются устройством предварительного декодирования. Последнее, по коду команды, формирует 100-разрядную микрокоманду, которую заносит в очередь микрокоманд. Устройство управления и устройство обработки извлекают первую микрокоманду из очереди и обеспечивают ее выполнение.

Физические адреса формируются блоком трансляции адресов, состоящим из двух устройств, поддерживающих страничную и сегментную организацию памяти. Допустимость обращений к памяти и портам ввода-вывода проверяется устройством защиты.

В блоке обработки регистровый файл включает те же регистры, что и МП 8086 и МП 80286, расширенные до 32 разрядов. Сохранены все способы адресации операндов (формирования исполнительного адреса ЕА), типы и форматы обрабатываемых данных. Пересылочные и арифметико-логические операции могут выполняться над 8-, 16- и 32-разрядными кодами. В среднем, для выполнения одной команды требуется 4.4 такта синхронизации, что при частоте 16 МГц дает

усредненное быстродействие 3.6 MIPS. На простейших операциях (передача из регистра в регистр) быстродействие увеличивается до 8 MIPS. Существенно отличается в МП 80386 организация виртуальной памяти. При сохранении идеи сегментации, аналогичной 80286, во-первых, максимальная длина сегмента увеличена до 4 Гбайт и, во-вторых, введена двухуровневая страничная организация памяти. Виртуальный адрес состоит из 14-разрядного селектора, загружаемого в один из 6 сегментных регистров, и 32-разрядного исполнительного адреса (смещения в сегменте). Таким образом, емкость адресуемой виртуальной памяти составляет 246= 64 Тбайт. Столь гигантский объем виртуальной памяти, по мнению разработчиков, необходим для подключения перспективных внешних запоминающих устройств сверхвысокой емкости, например, оптических дисков. Селектор сегмента задает расположение дескриптора в соответствующей (локальной или глобальной) таблице, по которой определяется базовый адрес сегмента, длина сегмента и правила доступа. Сумма базового и исполнительного адресов, вычисляемая в устройстве сегментации так же, как и в МП 80286, является исходной для страничного устройства. В 80386 эта сумма получила название линейного адреса. Линейный адрес разбивается на три поля: 10-разрядное поле индекса в справочнике таблиц, 10-разрядное поле индекса в таблице страниц и 12-разрядное поле смещения в странице (рис. 2.25). Следовательно, длина страницы составляет 4 Кбайт, а вся физическая память разбивается на 220 страниц. В памяти располагается справочник таблиц, который содержит до 1024 входных точек (начальных адресов) таблиц страниц. Каждая таблица в свою очередь определяет 1024 начальных адреса страницы в физической памяти. Начальный адрес справочника таблиц хранится в специальном 32-разрядном регистре, формирование физического адреса выполняется в два этапа: сначала из справочника таблиц по старшему индексу линейного адреса выбирается начальный адрес таблицы страниц, затем по второму индексу из таблицы выбирается начальный адрес страницы. Сумма начального адреса страницы и смещения из линейного адреса дает физический адрес требуемой ячейки памяти. Если найденная страница отсутствует в памяти, возникает исключение «нет страницы» и операционная система загружает с внешнего носителя 4 Кбайт в физическую память и записывает соответствующий адрес в таблицу страниц. После этого прерванная команда выполняется повторно. Информация о 32 наиболее используемых страницах хранится в специальном кэше (наборе регистров) страничных дескрипторов, что позволяет адресовать 128 Кбайт памяти без обращения к справочнику таблиц и таблице страниц. По данным [2.8] только в 2 % обращений к памяти приходится перегружать кэш дескрипторов, т. е. введение страничной адресации практически не снижает скорость формирования физических адресов.

Имеется возможность программно отключать как сегментацию памяти, так и поиск страниц. Первое делается загрузкой всех сегментных регистров одинаковыми селекторами, задающими нулевой базовый адрес сегмента. Тогда 32-разрядный исполнительный адрес ЕА фактически становится линейным адресом. Формирование физического адреса из линейного просмотром таблиц можно отменить, устанавливая соответствующий разряд управляющего регистра. При этом линейный адрес воспринимается как физический. Следовательно, допустимо четыре разных способа организации памяти в МП 80386: бесстраничная несегментированная, емкостью 4 Гбайт; страничная несегментированная, емкостью 4 Гбайт со страницами по 4 Кбайт; сегментированная бесстраничная виртуальная память, емкостью 64 Тбайт с сегментами по 4 Гбайт и страничная сегментированная виртуальная память, емкостью 64 Тбайт с сегментами по 4 Гбайт и страницами по 4 Кбайт. Конкретно выбираемая организация определяется, в первую очередь, требованиями к емкости и скорости доступа к памяти, защищенности данных и программ. При инициализации МП 80386 автоматически переходит в режим реальной адресации (как и МП 80286), в котором эмулируется работа микропроцессора 8086. В этом режиме загружаются все таблицы и системные регистры процессора, а затем программно выполняется переход к основному режиму работы с выбранной организацией памяти. К несомненным преимуществам МП 80386 относится и самотестирование, позволяющее при его инициализации проверить свыше 75 % аппаратуры интегральной схемы.

Совокупность архитектурных и схемных достоинств делает МП линии 8086, 80286, 80386 фактически международным стандартом для построения персональных и многопользовательских микроЭВМ. Фирма Intel объявила также о разработке нового микропроцессора 80486, первые поставки которого запланированы на 1989 г. Выпуск персональных ЭВМ на его базе ожидается в 1990—1991 гг. На момент написания пособия, предполагаемые технические характеристики МП 80486 не были опубликованы, хотя ожидается, что он будет содержать 1—1.25 млн. вентилей, иметь производительность 15—20 млн. операций/с, адресовать 4 Гбайт физической памяти с виртуальной адресацией до 64 Тбайт.