- •Предисловие

- •Глава 1

- •1.1. Средства микропроцессорной вычислительной техники

- •1.2. Основные характеристики, место и классификация микроЭвм

- •1.3. Индустрия микропроцессорных средств вт

- •Глава 2 элементная база микроэвм. Микропроцессоры

- •2.1. Микропроцессорные бис

- •2.2. Микропроцессор 8086

- •2.3. Развитие семейства мп 8086

- •Глава 3 элементная база микроэвм. Микропроцессорные семейства бис

- •3.1. Сопроцессоры

- •3.2 Интегральные микросхемы памяти

- •3.3. Интерфейсные схемы, контроллеры

- •3.4. Схемы обрамления

- •Глава 4 магистрально-модульная организация микроэвм

- •4.1. Интерфейсы и магистрали микроЭвм

- •4.2. Магистрали типа Multibus

- •4.3. Интерфейсы периферийного оборудования

- •4.4. Конструктивные особенности микроЭвм

- •Глава 5 аппаратура микроэвм

- •5.1. Периферия микроЭвм

- •5.2. Аппаратура персональных микроЭвм

- •5.3. Модульные системы и одноплатные микроЭвм

- •Глава 6

- •6.1. Операционные системы

- •6.2. Средства автоматизации программирования

- •6.3. Пакеты прикладных программ

- •1. Монография я учебные издания

- •2. Периодические издания

- •3. Фирменные издания

- •Глава 1. Введение в микропроцессорную технику .............................. 5

- •Глава 2. Элементная база микроЭвм. Микропроцессоры ...................... 18

- •Глава 3. Элементная база микроЭвм. Микропроцессорные семейства бис ............................................................................................................................ 81

- •Глава 4. Магистрально-модульная организация микроЭвм ……………108

- •Глава 5. Аппаратура микроЭвм ............. ……………………………….148

- •Глава 6. Программное обеспечение микроЭвм ........................................187

3.4. Схемы обрамления

В процессе проектирования аппаратуры микроЭВМ любого класса возникает ряд специфических вопросов. Как засинхронизировать работу МП и ЭВМ в целом? Как МП подключить к системной шине и организовать правильное их взаимодействие? Как выполнить регенерацию динамической памяти? И множество других, такого рода. Типичные схемные ответы на эти вопросы реализуются в виде БИС обрамления, которые ориентированы на какой-либо распространенный микропроцессор и/или системную шину. Можно указать четыре основные группы схем обрамления.

Схемы поддержки, обеспечивающие микропроцессору требуемые «условия труда» — синхронизирующие сигналы необходимой амплитуды, частоты и длительности (БИС генераторов тактовых импульсов — clock generator), запросы на прерывания, обработанные в соответствии с установленными приоритетами и порядком их поступления (БИС контроллеров прерываний — interrupt controller), служба времени (таймеры — interval timer).

Схемы управления памятью, поддерживающие работу МП с внутренними ЗУ большой емкости. Сюда относятся БИС управления регенерацией динамических ЗУПВ и БИС преобразования относительных (виртуальных) адресов в физические при сегментной и/или страничной организации памяти. Последние необходимы для МП, не имеющих встроенных трансляторов адресов. Например, для своего МП типа Z8001 фирма Zilog выпускает «менеджер» памяти (memory-manager unit — MMU), обеспечивающий работу с 64 сегментами по 64 Кбайт. Выпускаются также микросхемы, расширяющие адресное пространство малоразрядных микропроцессоров. Так, например, БИС 74LS610 фирмы Texas Instruments увеличивает объем адресуемой памяти с 64 Кбайт до 16 Мбайт.

Схемы управления шиной, связывающие МП, другие устройства микроЭВМ с системной шиной (магистралью), по которой они обмениваются информацией в соответствии с принятыми для этой шины правилами. К этой группе относятся шинные формирователи (bus driver), предназначенные для формирования сигналов с требуемыми электрическими параметрами, контроллеры шины (bus controller), генерирующие управляющие сигналы, и арбитры (bus arbiter), которые по определенным правилам выбирают одно устройство из нескольких, требующих шину для обмена информацией.

Схемы управления прямым доступом в память, организующие обмен информацией между внутренним ЗУ микроЭВМ и устройствами ввода-вывода (вернее, интерфейсными БИС или контроллерами ввода-вывода), минуя микропроцессор. При обмене по каналу прямого доступа в память (ПДП, direct memory access — DMA) МП только инициализирует операцию — определяет, с каким устройством выполнить обмен, сколько элементов информации необходимо передать или принять, где их разместить в памяти.

Выполнение же операции возлагается на контроллер ПДП (DMA controller), который генерирует всю необходимую последовательность сигналов на шине, «отвлекая» МП от основной работы только при завершении обмена или в случае непредвиденной ситуации.

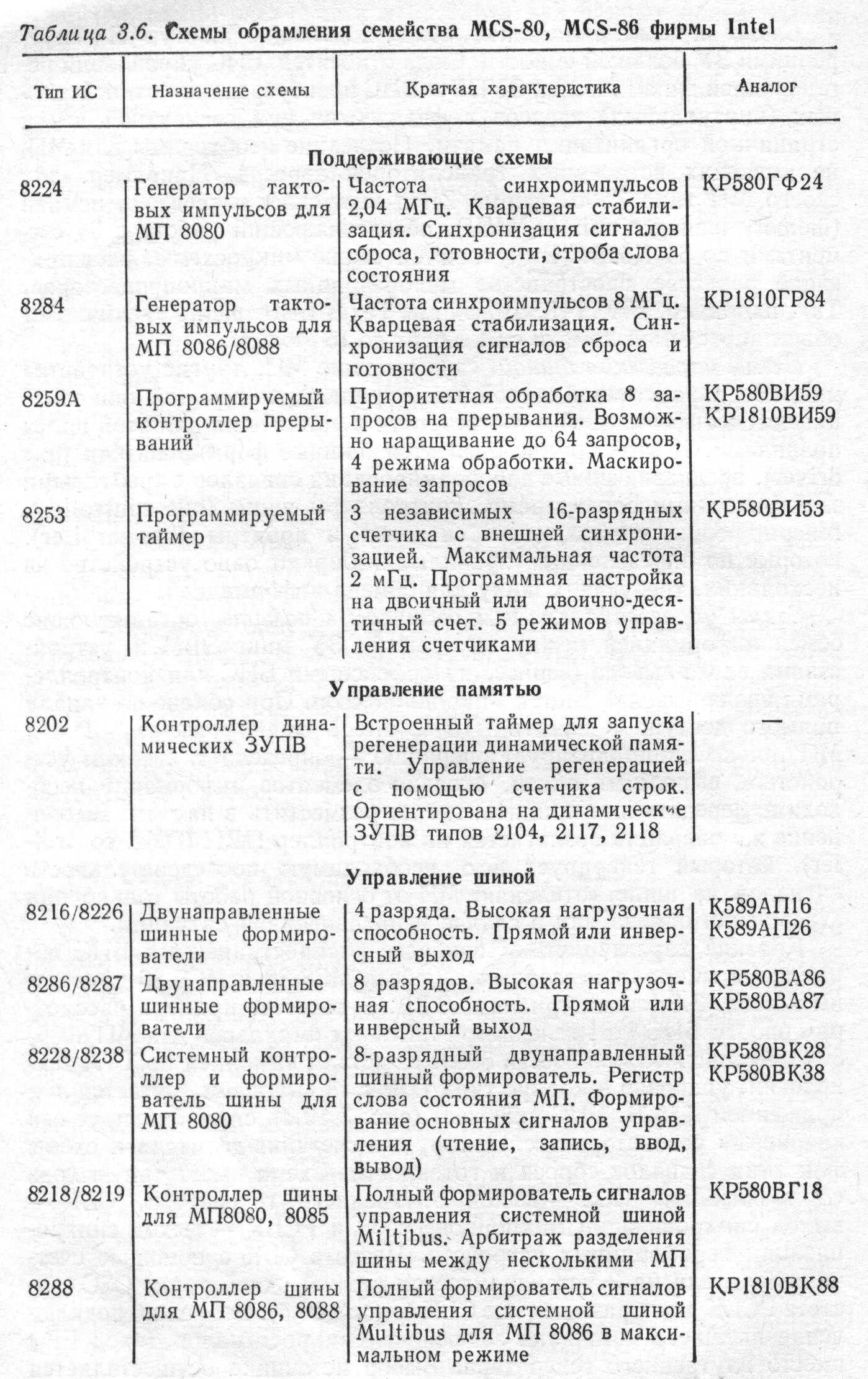

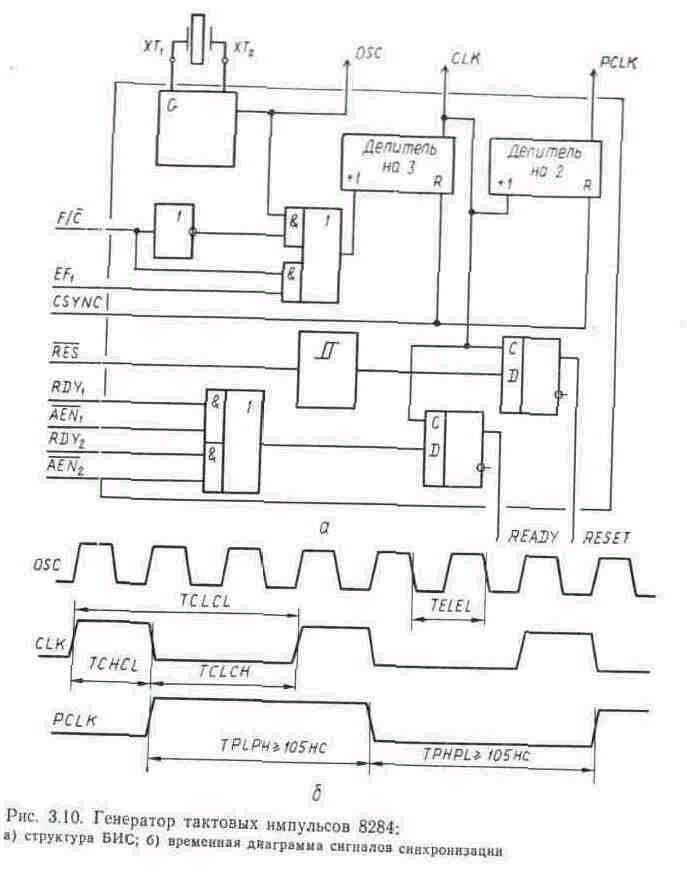

Краткие характеристики наиболее распространенных БИС обрамления микропроцессорных семейств MCS-80 и MCS-86 приведены в табл. 3.6 (по материалам [3.2]). В качестве примера рассмотрим работу БИС 8284 генератора тактовых импульсов для МП 8086/8088 и сопроцессоров 8087 и 8089. Кристалл выполнен по ТТЛ технологии, упакован в корпус типа DIP с 18 выводами, питается напряжением 4 — 5 В. БИС включает (рис. 3.10, а) синхронизируемый кварцевым резонатором генератор, два счетчика-делителя и схемы фиксации сигналов сброса и готовности. Схема имеет три выхода синхронизации: OSC — выход внутреннего генератора. CLK — выход синхронизации микропроцессора и PCLK — выход синхронизации периферийных устройств.

Частота

CLK с помощью счетчика-делителя на 3

устанавливается равной одной трети

OSC, частота PCLK в два раза меньше CLK

(рис. 3.10, б).

Возможно подключение внешнего

источника задающих синхросигналов

(вход EF1)

вместо внутреннего генератора. Выбор

источника осуществляется сигналом

![]() .

С помощью триггера Шмидта и D-триггера

внешний асинхронный сигнал сброса

.

С помощью триггера Шмидта и D-триггера

внешний асинхронный сигнал сброса

![]() фиксируется спадающим фронтом сигнала

CLK

в соответствии со спецификациями на

сигнал RESET

МП 8086. Внешние сигналы готовности также

фиксируются спадающим фронтом сигнала

CLK с помощью D-триггера. При синхронизации

кварцевым резонатором частота OSC

лежит в пределах 12 — 25 МГц (TELEL40

нс). Максимально допустимая частота

CLK=8 МГц при длительности импульса TCHCL

не менее 43 не и паузы TCLCH

не менее 68 нс. Длительность паузы и

импульса PCLK

не менее 105 нс.

фиксируется спадающим фронтом сигнала

CLK

в соответствии со спецификациями на

сигнал RESET

МП 8086. Внешние сигналы готовности также

фиксируются спадающим фронтом сигнала

CLK с помощью D-триггера. При синхронизации

кварцевым резонатором частота OSC

лежит в пределах 12 — 25 МГц (TELEL40

нс). Максимально допустимая частота

CLK=8 МГц при длительности импульса TCHCL

не менее 43 не и паузы TCLCH

не менее 68 нс. Длительность паузы и

импульса PCLK

не менее 105 нс.

Стремление разработчиков расширить доступ непрофессиональных пользователей ко все большим вычислительным мощностям приводит к дальнейшему усложнению как самих микропроцессорных БИС, так и БИС микропроцессорных семейств. Наращивание функциональной гибкости схем обрамления, контроллеров и интерфейсных схем; их «интеллектуализация» ведет фактически к тому, что они сами превращаются в специализированные микропроцессоры или микрокомпьютеры.