- •1.2. Логическая операция или

- •5.2. Полный двоичный сумматор

- •1270 Гц – логическая 1; 1070 Гц – логический 0.

- •2. 2225 Гц – логическая 1; 2025 Гц – логический 0.

- •12.4. Передача данных по протяженным линиям связи

- •1. Модуляция - на основе синусоидального несущего сигнала.

- •12.4.2. Модуляция как вид кодирования сигналов

- •12.4.3. Цифровое кодирование

5.2. Полный двоичный сумматор

Σ

s

c

Σ/2

x

c

s

Σ/2

1

c0

y

c

сумматор |

||||

вход |

выход |

|||

x |

y |

c |

s |

c0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Таблица истинности

двоичного сумматора.

Функция преобразования

двоичного сумматора:

S = x'y'c+x'yc'+xy'c'+xyc

C0= x'yc+xy'c+xyc'+xyc

Мнемоническое изображение сумматора:

c

Σ

s

x

c0

y

c0

5.3. Параллельный двоичный сумматор

линия циклического переноса

x4

y4

x3

y3

x2

y2

x1

y1

c1

c4

c3

c2

Σ

Σ

Σ

Σ

линия переполнения

с0

с0

с0

с0

s

s

s

s

&

&

&

&

линия сложения

s4

s3

s2

s1

6. Триггеры

Мнемоническое изображение триггера:

T

Q

выходные

Q' входные

сигналы

входные

сигналы

сигналы

импульсы

синхронизации

6.1. RS – триггер

RSA

Q

S

&

Текущее состояние выхода |

Входы |

|||

S=0 R=0 |

S=0 R=1 |

S=1 R=0 |

S=1 R=1 |

|

Q=0 Q=1 |

0 1 |

0 0 |

1 1 |

× × |

Q

&

R

× - неопределенное состояние триггера.

U

t

tp1

tp2

RS

S

RSA

Q

&

SC

Q'

R

&

RC

C

6.2. JK – триггер

JK

J

Q

&

RS

S

Текущее состояние выхода |

Входы |

|||

J=0 K=0 |

J=0 K=1 |

J=1 K=0 |

J=1 K=1 |

|

Q=0 Q=1 |

0 1 |

0 0 |

1 1 |

1 0 |

K

&

R

C

Q

C

6.3. Т – триггер

Таблица состояний Т - триггера

Текущее состояние выхода |

Входы |

|

T=0 |

T=1 |

|

Q=0 |

0 |

1 |

Q=1 |

1 |

0 |

Q

T

J

K

JK

C

T

Q

6.4. D – триггер

Таблица

состояний D

- триггера

Таблица

состояний D

- триггера

Текущее состояние выхода |

Входы |

|

D=0 |

D=1 |

|

Q=0 |

0 |

1 |

Q=1 |

0 |

1 |

6.5. Асинхронные входы триггеров

Двухтактный JK - триггер с входами предустановки и очистки:

предустановка

Q

J

JK

K

Q'

C

очистка

7. Регистры

7.1 Запоминающий регистр

7.2. Схема загрузки запоминающего регистра

7.3. Порт ввода-вывода

7.4. Сдвиговый регистр

8. Счетчики

8.1. Двоичные счетчики

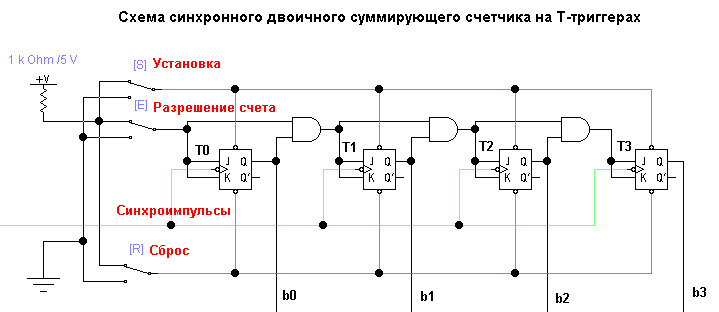

8.1.1. Синхронный двоичный суммирующий счетчик

Временная диаграмма суммирующего счётчика

8.1.2. Параллельный синхронный двоичный

суммирующий счетчик

8.1.3. Асинхронный суммирующий счетчик

8.1.4. Двоичные вычитающие счетчики

b3 |

b2 |

b1 |

b0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 ↓ |

1 |

0 |

0 |

1 ↑ |

0 |

0 |

0 ↓ |

1 |

1 |

0 |

1 ↑ |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 ↓ |

1 |

1 |

1 |

1 ↑ |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

↓- суммирующий счетчик; ↑- вычитающий счетчик.

8.2. Десятичные счетчики

8.2.1. Синхронный десятичный суммирующий счетчик

8.2.2. Трехразрядный синхронный суммирующий счетчик

в коде 8-4-2-1

9 . Дешифраторы

9.1. Дешифратор "1 из 4-х"

9.2. Дешифратор "1 из 16-и"

9.3. Дешифраторы других типов

Семисегментный индикатор

Таблица преобразователя кодов семисегментного индикатора

Десятичная цифра |

Код 8 – 4 – 2 – 1 |

Семисегментный код a b c d e f g |

0 |

0 0 0 0 |

1 1 1 1 1 1 0 |

1 |

0 0 0 1 |

0 1 1 0 0 0 0 |

2 |

0 0 1 0 |

1 1 0 1 1 0 1 |

3 |

0 0 1 1 |

1 1 1 1 0 0 1 |

4 |

0 1 0 0 |

0 1 1 0 0 1 1 |

5 |

0 1 0 1 |

1 0 1 1 0 1 1 |

6 |

0 1 1 0 |

1 0 1 1 1 1 1 |

7 |

0 1 1 1 |

1 1 1 0 0 0 0 |

8 |

1 0 0 0 |

1 1 1 1 1 1 1 |

9 |

1 0 0 1 |

1 1 1 1 0 1 1 |

10.Селектор

11. Шины

11.1. Типовая структура шин

11.2. Параллельные синхронные шины

11.2.1. Простейшая система с одной параллельной

шиной данных

Тристабильный формирователь

D Q

Q

Разрешение

11.2.2. Система с двумя адресными шинами

11.2.3 Система с общей шиной адреса и данных

11.3. Схемы с предопределенным участником передачи

11.4. Параллельные асинхронные шины

11.4.1. Система с параллельной асинхронной шиной

11.4.2. Квитирование для асинхронной шины

12. Последовательный ввод/вывод

12.1. Схема последовательного синхронного канала

12.2. Схема последовательного асинхронного канала

12.3. Двунаправленные каналы последовательной передачи данных

UART – универсальный асинхронный ресивер-трансмиттер.

USRT – универсальный синхронный ресивер-трансмиттер.

Стандарты двунаправленных каналов:

- «токовая петля»

- RS 232 C

Полосы частот модемов: