- •1. Однокристальные микро-эвм (омэвм) семейства mcs51. Обобщённая структурная схема микроЭвм. Основные характеристики омэвм.

- •2. Структурная схема микро-эвм семейства mcs51 (к1816ве51). Операционный узел. Формат регистра psw. Структурная схема микроконтроллера

- •Операционный узел

- •3. Структурная схема микро-эвм семейства mcs51 (к1816ве51). Узел внутренней памяти. Состав регистров специального назначения.

- •4. Организация адресного пространства микро-эвм семейства mcs51. Узел внутренней памяти

- •5. Порты микро-эвм семейства mcs51 (к1816ве51). Назначение портов. Функциональная схема порта р0. Узел управления и синхронизации

- •Узел сопряжения с внешними устройствами

- •6. Способы адресации микро-эвм семейства mcs51 (к1816ве51).

- •Cпособы адресации

- •7. Система команд микро-эвм семейства mcs51 (к1816ве51). Группа команд пересылки данных.

- •8. Система команд микро-эвм семейства mcs51 (к1816ве51). Группа команд обработки данных.

- •9. Система команд микро-эвм семейства mcs51 (к1816ве51). Группа команд управления.

- •11. Временная диаграмма типового машинного цикла. Примеры временных диаграмм для выполнения команд за один и за два машинных цикла.

- •А) Считывание команд из внутр. Памяти программ (сверху до пунктира).

- •Б) Ниже пунктира – внешняя память данных. Данные читаются во 2ом мц.

- •1. Если чтение из внутр. Пп, то psen не вырабатывается.

- •12. Таймеры/счётчики 0 и 1 микроконтроллера семейства mcs51 (омэвм51). Режимы работы, программирование таймера/счётчика.

- •13. Таймер/счётчик 2. Режимы работы.

- •14. Организация прерываний в омэвм51.

- •Обработка внутренних прерываний

- •15. Организация последовательного ввода/вывода микроконтроллера семейства mcs51 (омэвм51). Режимы работы uart. Расчет скорости передачи данных для асинхронного режима.

- •Формирование p для передатчика.

- •Примеры программирования последовательного ввода/вывода.

- •16. Последовательный интерфейс i2c.

- •Случай чтения байта из памяти:

- •Временная диаграмма

- •17. Последовательный интерфейс spi (Serial Periferial Interface).

- •18. Последовательный интерфейс can.

- •19. Последовательный интерфейс One wire (MicoLine).

- •Структурная схема шины usb

- •Хост контроллер – на шине только один. Функция – периферийное устройство. В хабе имеется порт (точка подключения). Корневой хаб входит в состав хоста.

- •21. Обзор современных микроконтроллеров семейства mcs51. Особенности микроконтроллеров фирм Philips, Atmel и др.

- •22. Микроконтроллеры mсs 251, 151. Микроконтроллер 251.

- •23. События. Примеры захвата событий. Массив программируемых счетчиков (pca). Режимы захвата, программируемого таймера, скоростного ввода вывода, генератора шим.

- •Краткий обзор pic 16c 6x/7x/8x

- •3. Управляющие команды

- •4. Команды пересылки данных

- •25. Микроконтроллеры с risc архитектурой (семейство avr). Организация памяти. Особенность портов ввода вывода. Обзор системы команд. Пример программы с использованием команд микроконтроллера avr.

- •26. Цифровая обработка сигналов (цос). Примеры задач цос. Сигнальные микроконтроллеры фирмы Texas Instruments (tms320). Сигнальные процессоры

- •Рассмотрим tms 320

- •Организация памяти

- •Инструментальные ср-ва разработки и отладки мпс

1. Однокристальные микро-эвм (омэвм) семейства mcs51. Обобщённая структурная схема микроЭвм. Основные характеристики омэвм.

G – внутренний тактовый генератор;

CPU – процессор (АЛУ, дешифратор команд, счетчик команд и т.д.);

ROM, RAM: память программ – ПЗУ;

память данных – ОЗУ;

IU – интерфейсные устройства;

P0, …, Pn – порты ввода/вывода;

EA – специальный управляющий сигнал, с помощью которого внутреннюю память можно исключить;

M – внутренняя магистраль.

Технические характеристики:

Контроллеры – 8-разрядные;

Используется гарвардская архитектура (т.е. память делится на память программ и память данных), для связи с внешней средой – порты ввода/вывода, интерфейсные устройства IU: таймеры, контроллеры прерываний, UART, АЦП и т.д.;

fтактовая = 12 40 МГц;

Память программ – емкость 2 64 Кбайт. Может быть с однократным или многократным программированием.

Если внутренняя память отсутствует, то могут быть использованы внешние микросхемы памяти программ, с помощью которых память программ можно расширить до 64К. НО в сумме внешняя и внутренняя память программ не должна превышать 64 Кбайт.

Память данных – 128 8 бит, либо 256 8 бит.

Память данных с помощью внешних микросхем памяти также может быть расширена до 64К.

Примечание: может быть объединена память программ и данных, и общая память будет составлять 64К.

Число портов ввода/вывода: общий набор выводов – 32 линии (из них может быть назначено любое количество линий ввода и вывода, например, 27 линий ввода и 5 линий вывода).

Количество портов может быть более четырех.

Наличие таймеров/счетчиков. Базовая конфигурация: 2 шт.

Может быть встроено устройство – сторожевой таймер, – которое через определенные интервалы времени подтверждает работу процессора, если подтверждения нет, то формируется сигнал сброса.

UART – универсальный синхронный приемник/передатчик или наличие последовательного ввода/вывода. Последовательные интерфейсы I2C, CAN, SPI, USB.

Контроллер прерываний может содержать от 5 до 6 уровней прерывания (как внутренние, так и внешние), если 5, то 3 внутренних и 2 внешних.

Наличие побитной обработки, т.е. возможность управления не всем портом целиком, а конкретным битом задачи управления упрощаются

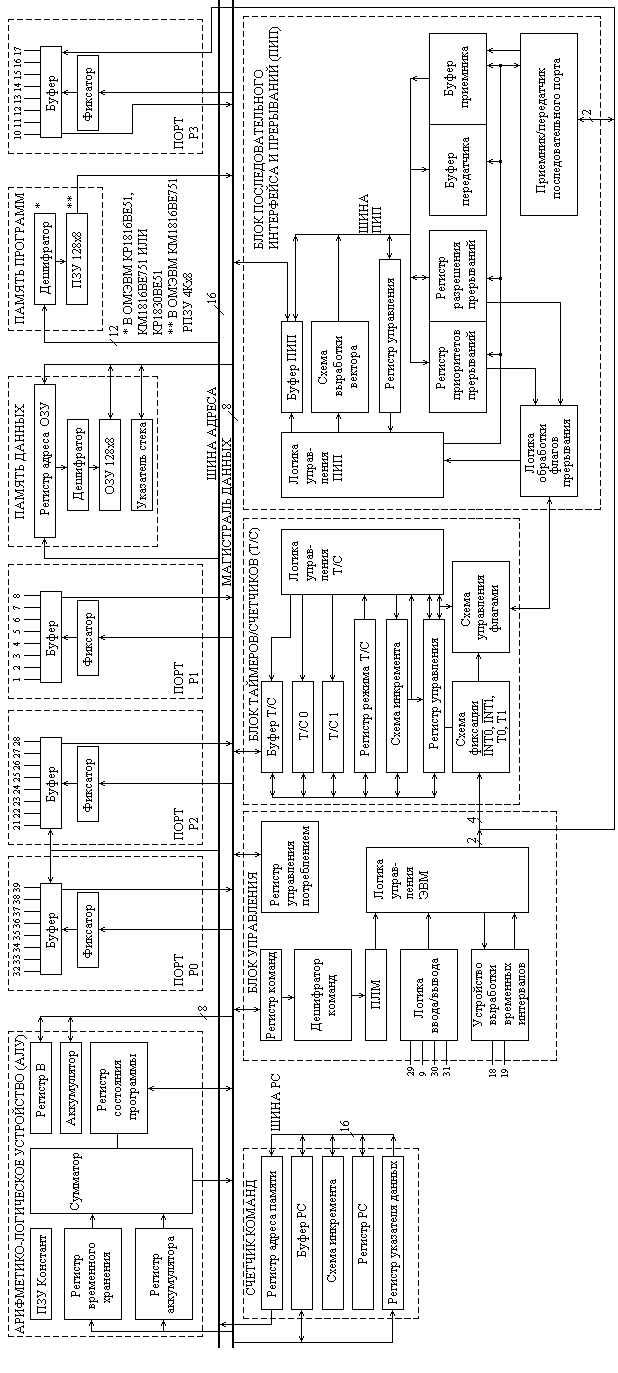

2. Структурная схема микро-эвм семейства mcs51 (к1816ве51). Операционный узел. Формат регистра psw. Структурная схема микроконтроллера

Структурная схема ОМЭВМ условно может быть разделена на 4 узла:

операционный узел;

узел внутренней памяти;

узел управления и синхронизации;

узел сопряжения с внешними устройствами, к которому относятся порты ввода/вывода.

Операционный узел

Состав операционного узла: АЛУ (арифметические и логические операции), регистр-аккумулятор ACC, буферные регистры временного хранения операндов БР1 и БР2, регистр состояния программы PSW, регистр расширения B (для операций деления и умножения), участвующий в операциях умножения и деления и схема десятичной коррекции СДК.

Важной особенностью АЛУ является его возможность оперировать не только байтами, но и битами.

Структура регистра состояния программы PSW:

![]()

С – признак переноса;

AC – признак промежуточного переноса;

F0 – определяется пользователем;

RS1 и RS0 – выбор номера банка РОНов, т.е. всего 4 банка.

RS1 |

RS0 |

№ банка |

Адреса регистров |

0 |

0 |

0 |

00h – 07h |

0 |

1 |

1 |

08h – 0Fh |

1 |

0 |

2 |

10h – 17h |

1 |

1 |

3 |

18h – 1Fh |

В каждом банке 8 регистров (R0, …, R7), различающиеся по текущему номеру банка. При сбросе устанавливается 0-ой банк.

OV – арифметическое переполнение;

P – признак четности (паритет).

Примечание: отсутствует Z – знак результата; он формируется по умолчанию при участии аккумулятора