- •Предисловие

- •Глава 1. Организация и методика проектирования

- •1.1. Общие рекомендации

- •1.2. Сигналы и каналы связи в радиоэлектронных системах.

- •1.3. Радиопередающие устройства в каналах связи радиоэлектронных систем

- •Глава 2. Применение устройств формирования сигналов в радиоэлектронных системах.

- •2.1. Рэс с текущей и задержанной информацией.

- •2.2. Рэс спутниковой связи.

- •2.3. Телеметрические рэс.

- •2.4. Радиорелейные линии связи – ррлс.

- •2.5. Радиостанции оперативной связи.

- •2.6. Радиоэлектронные системы с задержанной информацией.

- •2.6.1. Навигационные радиопередатчики-радиомаяки.

- •2.6.2. Охранные рэс.

- •2.6.3. Рэс дистанционно управляемых механизмов (замков, станков и т.П.)

- •2.6.4. Радиоэлектронные системы опознавания и разведки.

- •2.6.5. Многоканальный приемо-передатчик с автоматическим управлением.

- •Глава 3. Проектирование устройств формирования сигналов.

- •3.1. Функциональная схема.

- •3.2. Структурная схема.

- •3.2.1. Структурная схема передающего модуля.

- •3.2.2. Структурная схема передатчика службы спасения.

- •3.2.3. Структурные схемы транзисторных передатчиков.

- •3.2.4. Структурная схема синтезатора частот.

- •3.3. Принципиальная схема.

- •3.3.1. Принципиальная схема передающего модуля.

- •3.3.2. Принципиальные схемы синтезаторов частот.

- •3.3.5. Принципиальные схемы транзисторного передатчика.

- •3.4. Конструкция.

- •3.5. Техническая документация. Оформление проекта.

- •3.5.1. Пояснительная записка.

- •3.5.2. Чертежи.

- •Библиографический список.

- •1. Учебники и учебные пособия.

- •2. Системное проектирование.

- •3. Функциональное проектирование.

- •Приложение п3. Перечень элементов к принципиальной схеме рис 3.16.

- •Наименование

- •Передающий модуль

- •Наименование

- •Приложение п7. Микросхемы усилителей мощности.

- •Приложение п8. Микросхемы фильтров на поверхностно-аккустических волнах (пав).

- •Приложение п12. Микросхемы демодуляторов.

- •Приложение п16. Микросхемы передатчиков.

- •Приложение п17. Параметры биполярных транзисторов.

- •Приложение п18. Параметры типового режима биполярных транзисторов. Предельные эксплуатационные данные.

- •Оглавление.

- •Глава 1. Организация и методика проектирования 4

- •Глава 2. Применение устройств формирования сигналов в радиоэлектронных системах. 9

- •Глава 3. Проектирование устройств формирования сигналов. 37

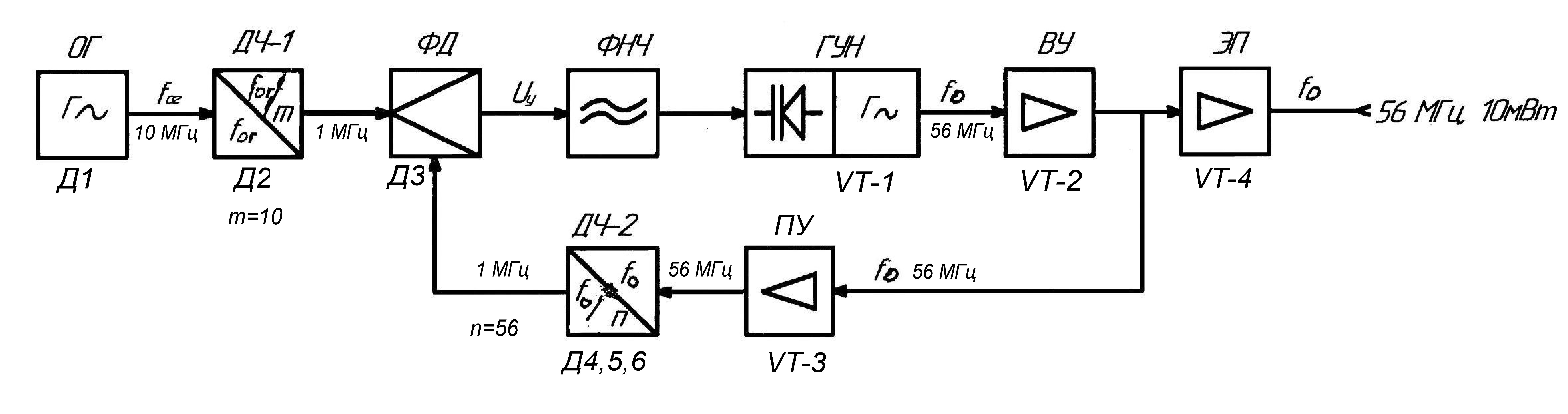

3.2.4. Структурная схема синтезатора частот.

Структурная схема синтезатора частот ККС, используемого в качестве возбудителя РПУ или генератора опорной частоты гетеродина, показана на рис. 3.15.

Синтезатор формирует малошумящий гармонический сигнал на опорной частоте f0 =56 МГц с высокой стабильностью δf=±5∙10-8 и мощностью 10 мВт. Формирование выходного сигнала осуществляется по принципу косвенного, некогерентного синтеза путем синхронизации генератора, управляемого напряжением (ГУН) колебаниями высокостабильного эталонного ОГ при помощи системы фазовой автоподстройки частоты (ФАПЧ), образованной фазовым детектором (ФД), на один их входов которого подается напряжение с выхода ОГ через делитель частоты (ДЧ-1) с коэффициентом деления m=10, а на другой – напряжение с выхода ГУН через выходной усилитель (ВУ), промежуточный усилитель (ПУ) и делитель частоты (Д4-2) с коэффициентом деления n=56. С выхода фазового детектора управляющее напряжение Uу через фильтр нижних частот (ФНЧ) подается на управляющий элемент ГУН. Связь с нагрузкой осуществляется через эмиттерный повторитель (ЭП).

Рис. 3.15. Структурная схема синтезатора частот косвенного когерентного синтеза.

3.3. Принципиальная схема.

Электрическая принципиальная схема определяет полный состав элементов и связей между ними и представляет собой схему соединения отдельных каскадов структурной схемы с учетом активных элементов и пассивных СВЧ-устройств, соединяющий каскады между собой или с нагрузкой, обеспечивающих согласование соединяемых элементов по уровню входного и выходного сигнала и сопротивления. Кроме того принципиальная схема дополняется элементами, обеспечивающими управление, электрический контроль, сигнализацию и соединение с другими блоками и узлами системы (переключателями, разъемами, реле, измерительными приборами, предохранителями и т.п.). К принципиальной схеме составляется перечень элементов, в котором указываются обозначения элементов согласно нумерации и их основные электрические величины. Для стандартных деталей указывается ГОСТ и соответствующие обозначения.

Расчет согласующих целей и устройств сопряжения микросхем производится упрощенными инженерными методами (без применения ЭВМ, которые не исключены в некоторых особых случаях) на основании заданных входных и выходных сопротивлений соединяемых схем или доступных КСВН на входе и выходе по паспортным данным. Если условия согласования не выполняются в соединительную линию, включаются направленные ответвители (НО). При отсутствии паспортных данных полагают, что интегральные микросхемы рассчитаны на подключение к 50-омным линиям передачи. Для каждой линии передачи указываются номера соединяемых выводов микросхем согласно их УГО.

3.3.1. Принципиальная схема передающего модуля.

Принципиальная схема передающего модуля, функциональная и структурная схемы которого приведены на рис.2.20,3.6 соответственно, показана на рис. 3.16., перечень элементов к принципиальной схеме приведен в приложении ПЗ.

Схема содержит 7 ИМС: D1/К561РУ2 – датчик информации, запоминающее устройство, в памяти которого хранится цифровой

Рис. 3.16. Принципиальная схема передающего модуля.

информационный сигнал – ЦИС, записанный с выхода приемника; D2/АТ89с1051, частотный модулятор D3,D4/ХХХ10002Q4 – умножитель частоты, D5/ГК153УН – задающий генератор. Транзисторы VT-1 KT342Б, VT-2 KT865A – коммутатор реле Р1/РС4524202.

ИМС D1, D7 не входят в состав передающего модуля согласно функциональной схеме рис. 2.20, однако включены в принципиальную схему как принципиально необходимые элементы, определяющие формирование входного сигнала.

ИМС D1 К561РУ2 представляет собой оперативное запоминающее устройство с побитовой системой записи/считывания 256×1 бит информации и двумерной адресацией. Структура ИМС представляет собой квадратурную решетку-матрицу 256-ти электрически запоминающих элементов (ЭЗЭ), каждый из которых рассчитан на хранение одного бита информации. Схема обеспечивает произвольный доступ к информации каждого отдельного ЭЗЭ путем адресации строки и столбца, пересечение которых определяет точку расположения ЭЗЭ. Адресация осуществляется подачей двоичного кода десятичного номера строки или столбца на соответствующие адресные входы. Так как объем памяти ЗУ составляет 256 бит, то число строк и столбцов равно 16-ти, а число адресных входов и разрядность адресных кодов равна 4. Номер строки определяется 4-х разрядным кодом канала (КК), подаваемым на адресные входы А0-А3 с выхода МИКУ, номер столбца – 4-х разрядным кодом тактового импульса – КТИ, подаваемым на адресные входы В0-А3. Таким образом, схема D1 бронирует для каждого канала одну строку матрицы ЭЗЭ, предоставляя каждому абоненту 15 бит информации. Шестнадцатый бит каждой строки используется для формирования в МИКУ сигналов управления, подаваемых на входы «WE», «CE», обеспечивающих реализацию запрашиваемого режима работы:

– «запись»:

![]() ,

при котором информация, подаваемая на

вход «D»,

записывается по указанному адресу,

выход закрыт;

,

при котором информация, подаваемая на

вход «D»,

записывается по указанному адресу,

выход закрыт;

– «чтение»

![]() ,

при котором информация, выбираемая по

определенному адресу, подается на выход

ИМС;

,

при котором информация, выбираемая по

определенному адресу, подается на выход

ИМС;

– «хранение»

![]() сигналы

сигналы

![]() отсутствуют,

выход закрыт.

отсутствуют,

выход закрыт.

Сигналы

![]() формируются в МИКУ по коду операции

сигнала запроса и N-го

импульса сигнала синхронизации.

формируются в МИКУ по коду операции

сигнала запроса и N-го

импульса сигнала синхронизации.

Модулятор

D2

выполнен на микроконтроллере АТ89С-1051

ф. Atmel,

который представляет собой высокоскоростной

однокристальный микропроцессор для

применения в схемах различного назначения.

В данной схеме режим «модуляция»

осуществляется при подаче цифрового

модулирующего напряжения с выхода 13

D1

на вывод 11 D2

и гармонического колебания поднесущей

частоты

![]() с выхода задающего генератора D7

на вывод 12 D2.

Модулированный сигнал снимается с

вывода 19 и через фильтр НЧ на

с выхода задающего генератора D7

на вывод 12 D2.

Модулированный сигнал снимается с

вывода 19 и через фильтр НЧ на

![]() подается на вход умножителя частот D3.

Амплитуда входного/выходного гармонического

сигнала составляет (0–5) В, выходной

уровень логической «1» – (4,9-5) В.

Указанные номинальные значения элементов

определены после предварительного

программирования на основе набора

прилагаемых стандартный программ

«BayRom»

(MCS-51TM)

по алгоритму перемножения входных

сигналов [1]. При этом выход 8 заземляется.

подается на вход умножителя частот D3.

Амплитуда входного/выходного гармонического

сигнала составляет (0–5) В, выходной

уровень логической «1» – (4,9-5) В.

Указанные номинальные значения элементов

определены после предварительного

программирования на основе набора

прилагаемых стандартный программ

«BayRom»

(MCS-51TM)

по алгоритму перемножения входных

сигналов [1]. При этом выход 8 заземляется.

D3, D4 (ИМС ХХ1002Q4) представляет собой мощный умножитель частот с коэффициентом умножения M=16, амплитудой входного и выходного напряжения (0-5)В и выходной мощностью 1,2 Вт.

D5

– усилитель мощности НМС 636ST-89

(ф Hittite)

обеспечивает выходную мощность

![]() 7Вт

в диапазоне частот 200-2000 МГц с коэффициентом

усиления

7Вт

в диапазоне частот 200-2000 МГц с коэффициентом

усиления

![]() Дб.

Дб.

D6 – ИМС К561ЛА7 представляет собой четыре ЛЭ «2И-НЕ», два из которых используются как преобразователи уровня напряжения СУ до уровня отпирания транзистора VT-2 КТ865А. При поступлении импульсного сигнала управления транзистор VT-2 открывается на время длительности операции считывания, срабатывает реле Р1 (РС4524202), замыкая свои контакты К1 и подавая напряжение питания U0 на ИМС передающего модуля D2, D3, D4, D5.