- •1. Цель работы

- •2. Структура проекта

- •3. Рекомендуемый путь и этапы создания проекта в vdsp

- •3.1 Пример и описание .Ldf файла

- •Search_dir() - определение путей к текущей рабочей директории и к директории lib.

- •3.2 Структура простейшего .Asm файла

- •Rti; nop; nop; nop; /* 0x0008: irql1*/

- •3.3 Компоновка проекта и создание исполняемого .Dxe файла

- •Rti; nop; nop; nop; /* 0x0008: irql1*/

- •Rti; nop; nop; nop; /* 0x0020: sport1 transmit*/

- •Rti; nop; nop; nop; /* 0x0028: Timer*/

- •4. Запуск и отладка проекта.

- •4.1 Запуск проекта Lab1

- •4.2 Отображение содержимого памяти

- •4.3 Отображение содержимого регистров

- •4.4 Построение графиков

- •5. Задание к лабораторной работе

- •1. Особенности и типы команд сигнального процессора

- •2. Используемые условия

- •2.1 Подробное описание регистров состояния и значения их битов

- •2.2 Логическое описание условий (cond), используемых с оператором if

- •2.3 Условия завершения цикла do until (term)

- •3. Многофункциональные инструкции

- •3.1 Операции alu/mac с одновременным чтением памяти данных и памяти программ

- •3.2 Чтение памяти данных и памяти программ

- •3.3 Вычисления с чтением из памяти

- •3.4 Вычисления с записью в память

- •3.5 Вычисления с пересылкой регистр-регистр

- •4. Инструкции alu, mac и shifter

- •4.1 Инструкции и стандартные функции

- •4.2 Инструкции и стандартные функции

- •4.3 Инструкции и основные функции

- •5. Команды пересылки данных

- •6. Инструкции управления исполнением программы

- •If eq jump my_label; call (i6);

- •7. Другие инструкции и команды не вошедшие в

- •8. Обобщённая таблица команд

4.2 Инструкции и стандартные функции

умножителя

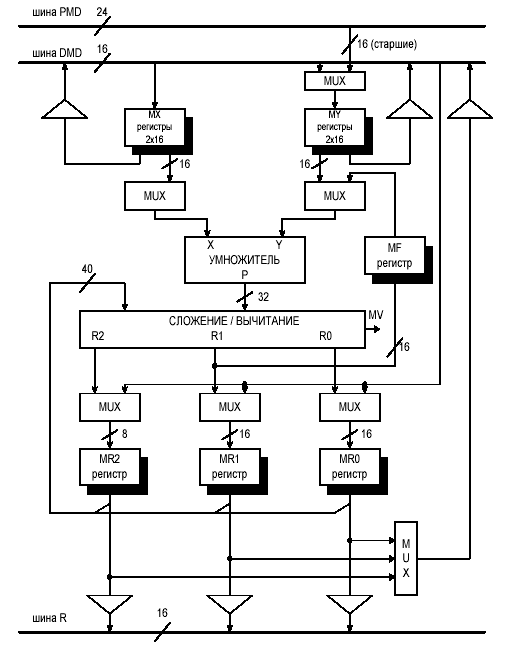

В умножителе (рис. П2) имеется два входных порта Х и Y разрядностью 16 бит и порт вывода результата Р разрядностью 32 бита. Результат разрядностью 32 бита передается в 40-разрядный сумматор/вычитатель, который прибавляет или вычитает новый результат из содержимого регистра умножителя MR (рис. П3) или передает новый результат прямо в МR. Регистр МR имеет разрядность 40 бит и состоит из трех регистров меньшей разрядности: МRО и МR1 разрядностью 16 бит и МR2 разрядностью 8 бит.

Рис. П2. Блок-схема умножителя-накопителя

Умножитель-накопитель реализует следующие функции:

R = X*Y, умножение операндов X и Y;

R = MR + X*Y, умножение операндов X и Y и сложение результата с содержимым регистра МR;

R = MR – X*Y, умножение операндов X и Y и вычитание полученного результата из содержимого регистра МR;

MR = 0, обнуление содержимого регистра MR.

Источниками-приемниками данных умножителя являются:

источники ввода данных в порт X: MX0, MX1, AR, MR0, MR1, MR2, SR0, SR1;

источники ввода данных в порт Y: MY0, MY1,MF;

направление вывода данных через порт R: MR (MR2, MR1, MR0), MF.

Общий

вид инструкции MAC

на языке ассемблера, например, умножения

с накоплением двух беззнаковых чисел

записывается следующим образом:

Общий

вид инструкции MAC

на языке ассемблера, например, умножения

с накоплением двух беззнаковых чисел

записывается следующим образом:

[IF cond] MR=MR+xop*yop (SS|UU|US|SU|RND);

IF NOT MV MR=MR+MXO*MY0 (UU);

Условное выражение IF NOT MV проверяет флаг переполнения MAC. Если флаг сброшен, исполняется инструкция NOP. Выражение MR=MR+MXO*MY0 – это операция умножения с суммированием. В регистре результата (MR) получается сумма его предыдущего значения с произведением значений входных Х и Y регистров. Модификатор в скобках (UU) сообщает процессору, что операнды беззнаковые.

Режим "знаковый * знаковый" (SS) используется при умножении двух знаковых чисел с одинарной точностью или старших слов двух знаковых чисел с повышенной точностью.

Режимы "беззнаковый * знаковый" (US) и "знаковый *беззнаковый" (SU) используются при умножении старших бит одного знакового числа с повышенной точностью на младшие биты другого, или при умножении знакового числа с одинарной точностью на беззнаковое число с одинарной точностью.

Режим "беззнаковый * беззнаковый" (UU) используется при умножении беззнаковых чисел с одинарной точностью или всех бит, кроме старших, двух знаковых чисел с повышенной точностью.

Режим RND – округление результата (для знаковых операндов).

4.3 Инструкции и основные функции

устройства циклического сдвига

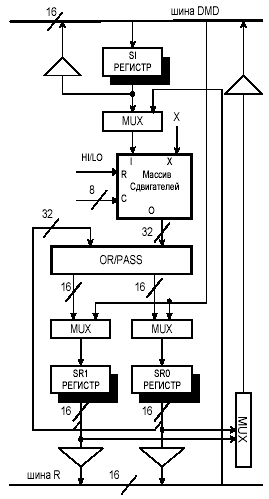

Устройство сдвига (рис. П4) обеспечивает полный набор функций сдвига для 16-разрядных входных значений, в результате чего на выходе получается 32-разрядный результат.

Устройство сдвига выполняет следующие операции:

арифметический сдвиг (ASHIFT);

логический сдвиг (LSHIFT);

нормализация (NORM);

определение порядка (EXP);

нахождение блочного порядка (EXPADJ).

В скобках указана мнемоника соответствующих им ассемблерных инструкций.

Источниками/приемниками данных для устройства сдвига являются:

источники ввода данных: SI, AR, MR0, MR1, MR2, SR0, SR1;

направление вывода результатов: SR (SR0, SR1).

Рис. П4. Блок-схема устройства циклического сдвига

Ниже приведены примеры некоторых операций устройства сдвига и реализующих их ассемблерных инструкций.

Пример №1 показывает непосредственный логический сдвиг вправо относительно старших бит SR (SR1):

SI = 0xB6A3; /* Входное значение 10110110 10100011 */

SR = LSHIFT SI BY –5 (HI); /* Величина сдвига –5 */

/* Выходное значение SR = 00000101101101010001100000000000*/

Пример №2 – то же самое значение сдвигается в другом направлении относительно младших бит SR:

SI=0xB6A3;

SR=LSHIFT SI BY 5 (LO); /* Величина сдвига +5 */ /*Выходное значение SR=00000000000101101101010001100000 */

Пример №3 соответствует операции непосредственного арифметического сдвига:

SI=0xB6A3;

SR=ASHIFT SI BY –5 (HI);

/* Выход: SR=11111101101101010001100000000000 */

Пример №4 – операция нормализации для входного значения с одинарной точностью, проводится в два этапа:

AR = 0xF6D4; /* Входное значение 1111011011010100 */

SE = EXP AR (HI); /* Определяет порядок, SE устанавливается на –3 */

SR = NORM AR (HI); /* Нормализация : сдвиг значения AR на величину, содержащуюся в SE */

/* Выход SR = 10110110101000000000000000000000 */

Пример №6 – инструкция нормализации, записанная ниже в обобщенной и конкретной форме:

[IF cond] SR=[SR OR] NORM xop (HI | LO);

IF NOT CE SR=SR OR NORM SI (HI);

Условное выражение IF NOT СЕ проверяет условие «если счетчик числа повторений ненулевой». Если условие не выполняется, исполняется инструкция NOP. Приемником для всех операций устройства циклического сдвига является регистр результата SR, кроме операции определения экспоненты (порядка), где приемник – это регистры SE или SB. В этом примере SI (входной регистр) является операндом. Длина и направление сдвига контролируются знаковым числом в регистре SE для всех операций сдвига, кроме немедленного сдвига. Положительные значения приводят к сдвигу влево; отрицательные – к сдвигу вправо. Модификатор «SR OR» (который может быть опущен) производит операцию логическое ИЛИ результата с текущим содержимым регистра SR - это позволяет получить 32-битное значение в SR из 16-битных частей. «NORM» – это оператор, a (HI) - модификатор, который определяет, происходит ли сдвиг относительно верхней (НI) или нижней (LO) 16-битной части SR. Если модификатор «SR ОR» опускается, результат сразу записывается в регистр SR.